Hall sensor with local groove structure of two-dimensional electron gas channel barrier layer and its manufacturing method

A Hall sensor, two-dimensional electronic technology, applied in the direction of Hall effect devices, electromagnetic device manufacturing/processing, electromagnetic equipment components, etc. Effects of increased voltage drop, improved device sensitivity, high electron mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

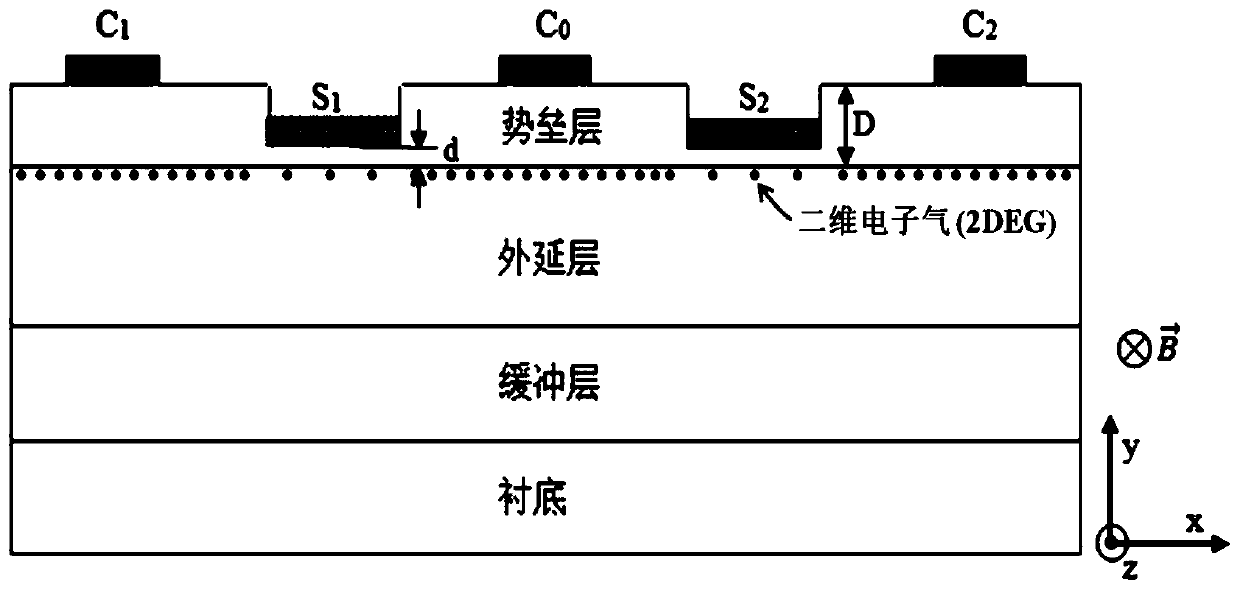

[0028] The structural schematic diagram of the technical solution of the present invention is as follows: figure 1 . Grow buffer layer, epitaxial layer and barrier layer respectively on a semiconductor substrate, the substrate is semiconductor or any other common substrate that can support semiconductor epitaxial growth, especially including Si, InAs, GaAs, SiC, GaN, ZnO, gallium oxide , boron nitride, diamond, sapphire, or any one of quartz, without special limitation; the epitaxial layer can be GaAs, GaN or SiC, without special limitation; the barrier layer can be AlGaAs, There is no special limitation on AlGaN (or InAlN or AlN), or AlN, and the material composition in the barrier layer is not particularly limited. All material combinations and parameter selections for semiconductor heterojunction structures that can generate two-dimensional electron gas are included in this paper. The scope of the patent is limited. The background carrier concentration range of epitaxial ...

Embodiment 2

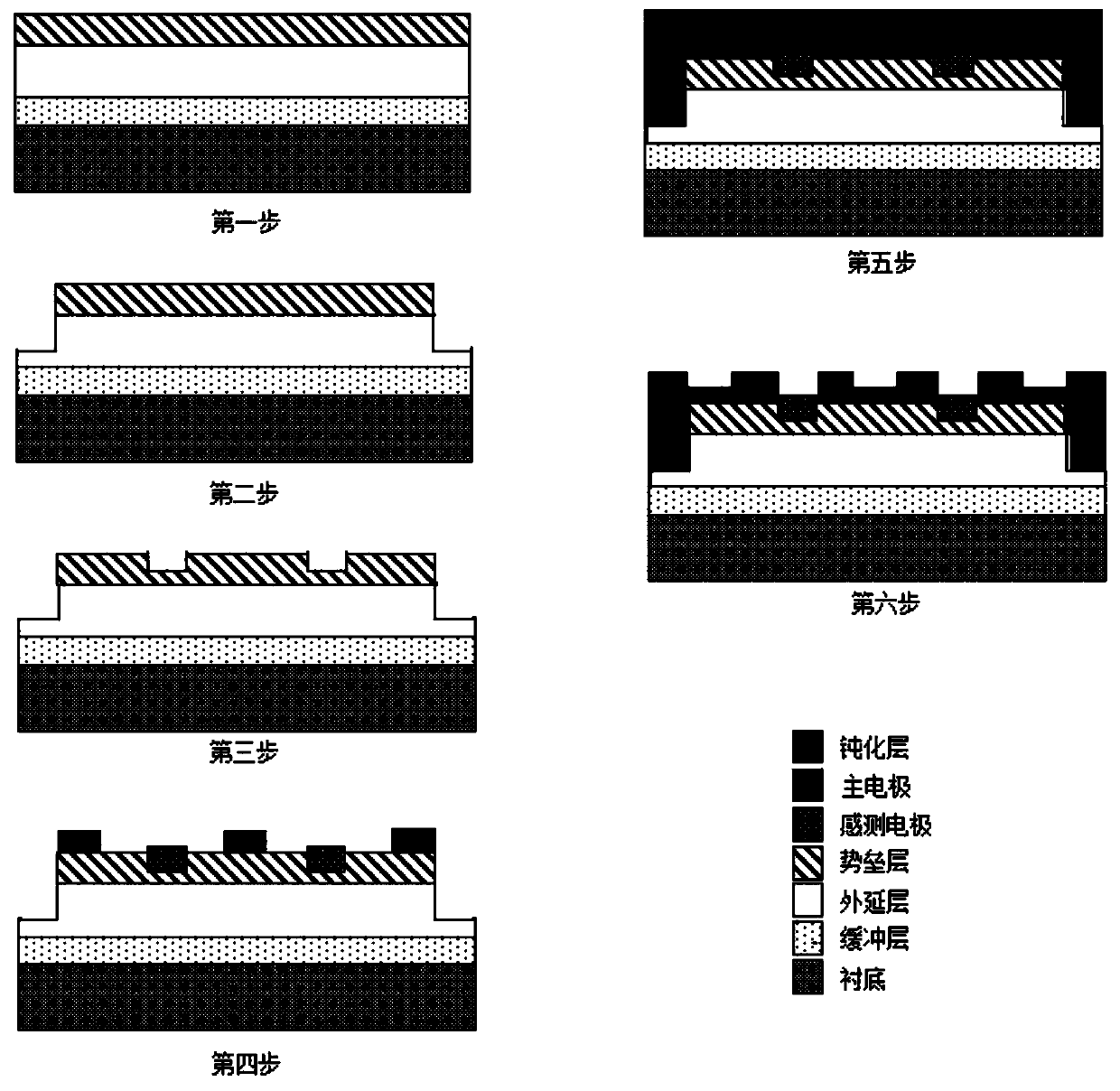

[0032] figure 2 Shows the basic process of making the Hall sensor proposed by the present invention:

[0033] Step 1: Device chip material preparation with heterojunction structure:

[0034] Device base material includes substrate, buffer layer, epitaxial layer and barrier layer. The device materials were ultrasonically cleaned with acetone, ethanol, and deionized water, each step was ultrasonically timed for 10 minutes, then dried with nitrogen, and baked in an oven at 110°C for 10 minutes for use.

[0035] The second step: device mesa etching and isolation:

[0036] The device mesa is defined by photolithography technology, and a good etching window is formed through steps such as glue coating, glue leveling, photolithography, and development, and then wet or dry etching technology is used to etch the material barrier layer and epitaxial layer. The etching depth is generally 20-2000nm.

[0037] Step 3: The barrier layer is selectively etched to form a local groove:

[...

Embodiment 3

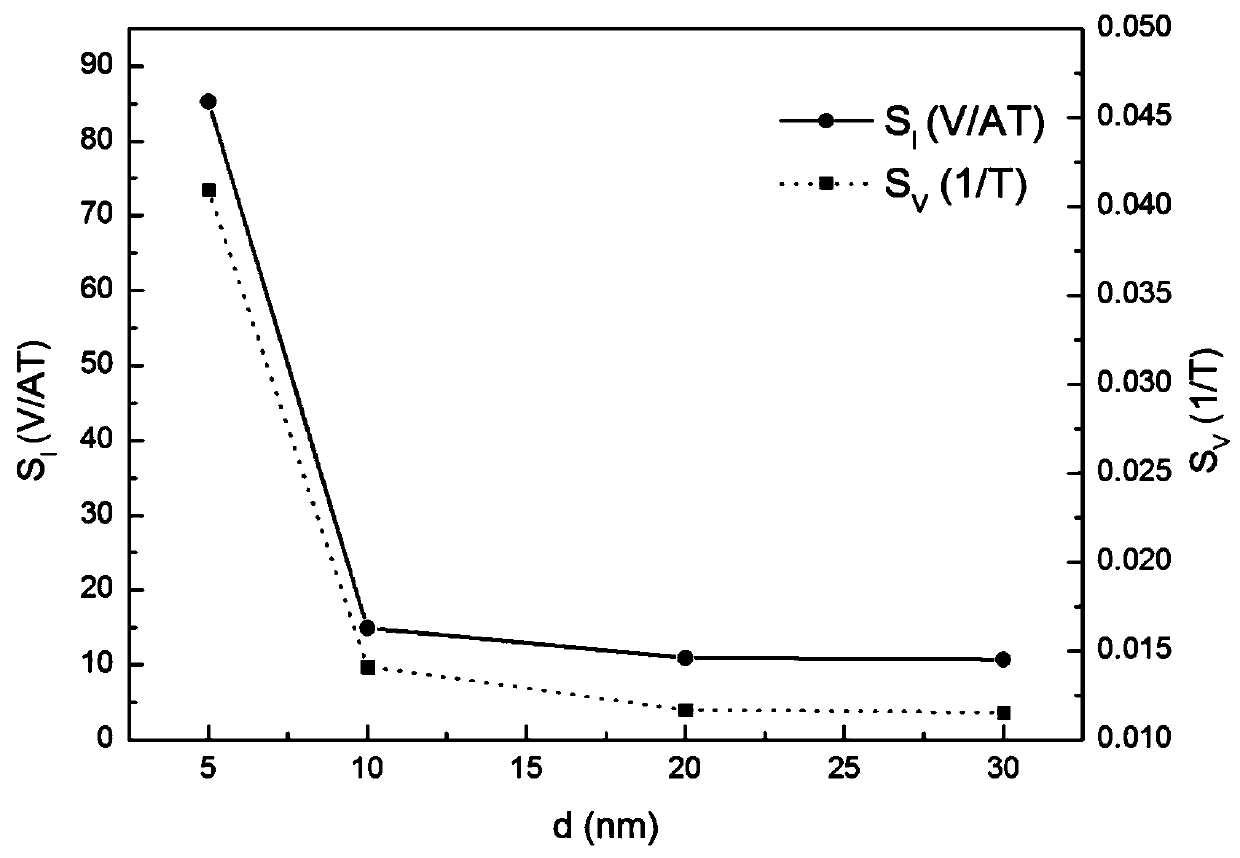

[0046] 1. Device structure parameters

[0047] A GaN material epitaxial wafer with Si substrate AlN as the buffer layer was used, in which the epitaxial layer was unintentionally doped GaN with a thickness of 6 μm and a background electron concentration of 1×10 16 cm -3 , the barrier layer is AlGaN, the thickness is 30nm, and the Al composition is 0.25. The three main electrodes of the chip C 0 、C 1 and C 2 and the Hall sensing electrode S on the groove 1 and S 2 The width is 2μm, where the electrode C 0 with electrode C 1 、C 2 The spacing is 8μm, the electrode C 0 with electrode S 1 , S 2 The pitches are all 3.5 μm.

[0048] 2. Device manufacturing process

[0049] Step 1: Device chip material preparation with heterojunction structure:

[0050] The device materials were ultrasonically cleaned with acetone, ethanol, and deionized water, each step was ultrasonically timed for 10 minutes, then dried with nitrogen, and baked in an oven at 110°C for 10 minutes for us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com