SoC visual design method based on IP core

A design method, IP-XACT technology, applied in computing, special data processing applications, instruments, etc., can solve the problems of complex SoC design, no silicon-level optimization and verification, and tedious RTL-level code development and maintenance. , to facilitate quick reading and understanding, reduce IC design cycles, and reduce syntax or functional errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific embodiments.

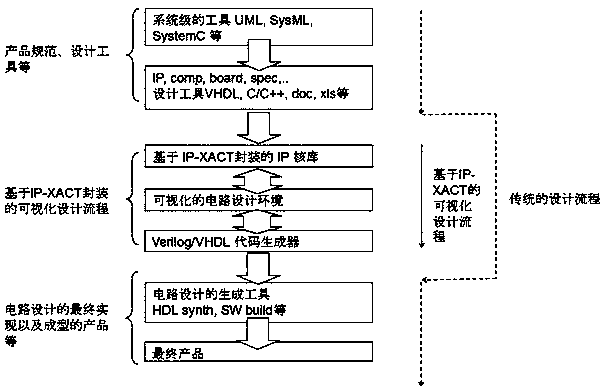

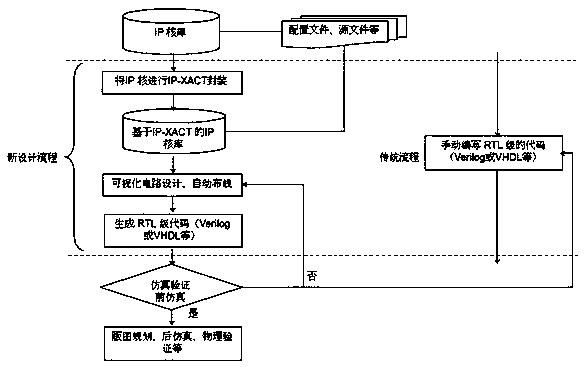

[0026] see Figure 1 to Figure 2 , the present invention provides a kind of technical scheme: a kind of SoC visual design method based on IP core, described visual design method comprises the following steps:

[0027] Step 1: Product specification and modeling; determine the functions required by the system, including the basic input and output of the system, basic algorithm requirements, and the functions, performance, power consumption, cost and development time required by the system, etc., and convert the user's requirements into user requirements. Design-based technical documents, and initially determine the design process of the system, formulate product definition instructions and specifications, etc., and then the designer uses the modelin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More