Silicon-based solar cell, preparation method and photovoltaic module

A solar cell, silicon-based technology, applied in the field of solar cells, can solve the problems of reducing cell photoelectric conversion efficiency, photoelectric conversion performance dependence, solar cell voltage and current loss, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

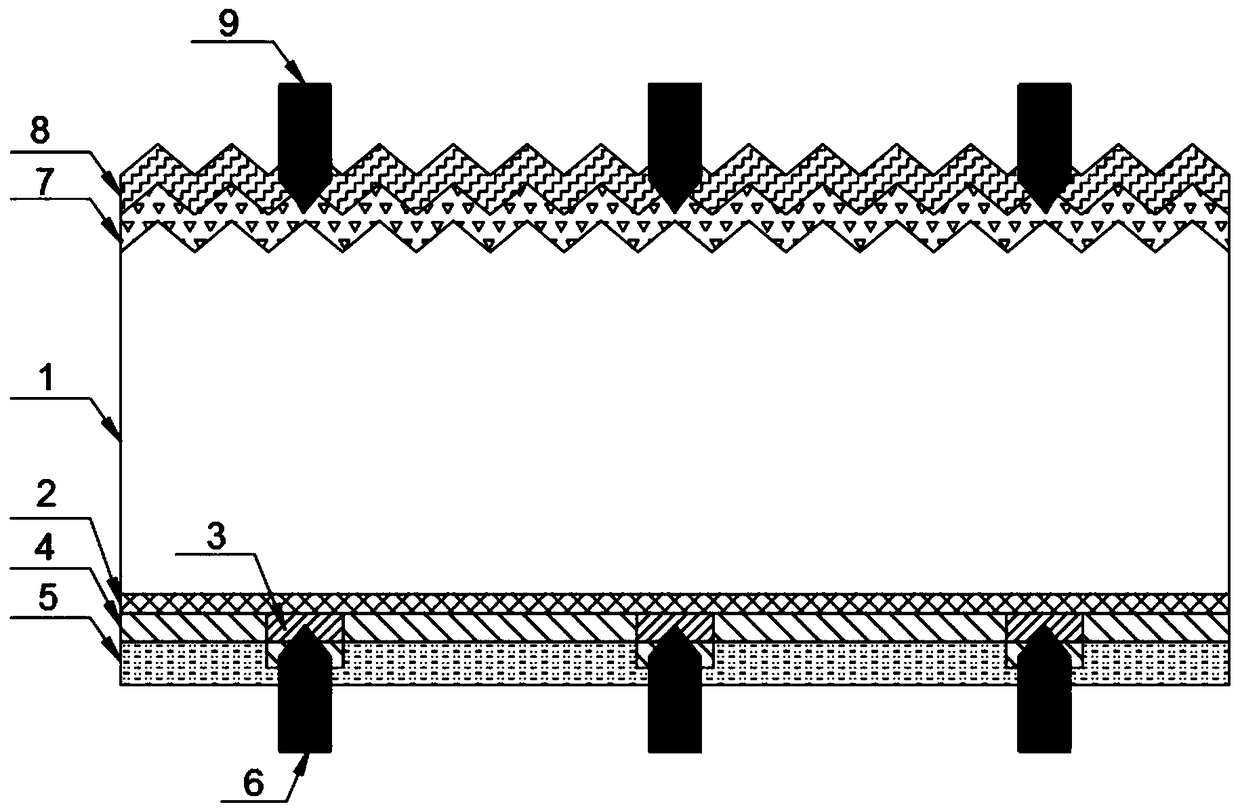

[0141] like figure 1 As shown, in this embodiment, the front side of the silicon-based solar cell includes:

[0142] The emitter layer 7 arranged on the front surface of the P-type crystalline silicon substrate 1,

[0143] an anti-reflection layer 8 disposed on the emitter layer 7,

[0144] as well as,

[0145] A front electrode 9 disposed on the anti-reflection layer 8 .

[0146] Wherein, the front electrode 9 is in ohmic contact with the emitter layer 7 through the anti-reflection layer 8 .

[0147] It can be understood that the emitter layer 7 is N-type silicon, which can be formed by doping the P-type crystalline silicon substrate 1 with group V elements (including but not limited to phosphorus). In this embodiment, the sheet resistance value of the emitter layer 7 formed after doping can be 40Ω / □~200Ω / □ (such as 40Ω / □, 50Ω / □, 60Ω / □, 70Ω / □, 80Ω / □, 90Ω / □ / □, 100Ω / □, 110Ω / □, 120Ω / □, 130Ω / □, 140Ω / □, 150Ω / □, 160Ω / □, 170Ω / □, 180Ω / □, 190Ω / □, 200Ω / □, etc.), emission The she...

Embodiment approach 2

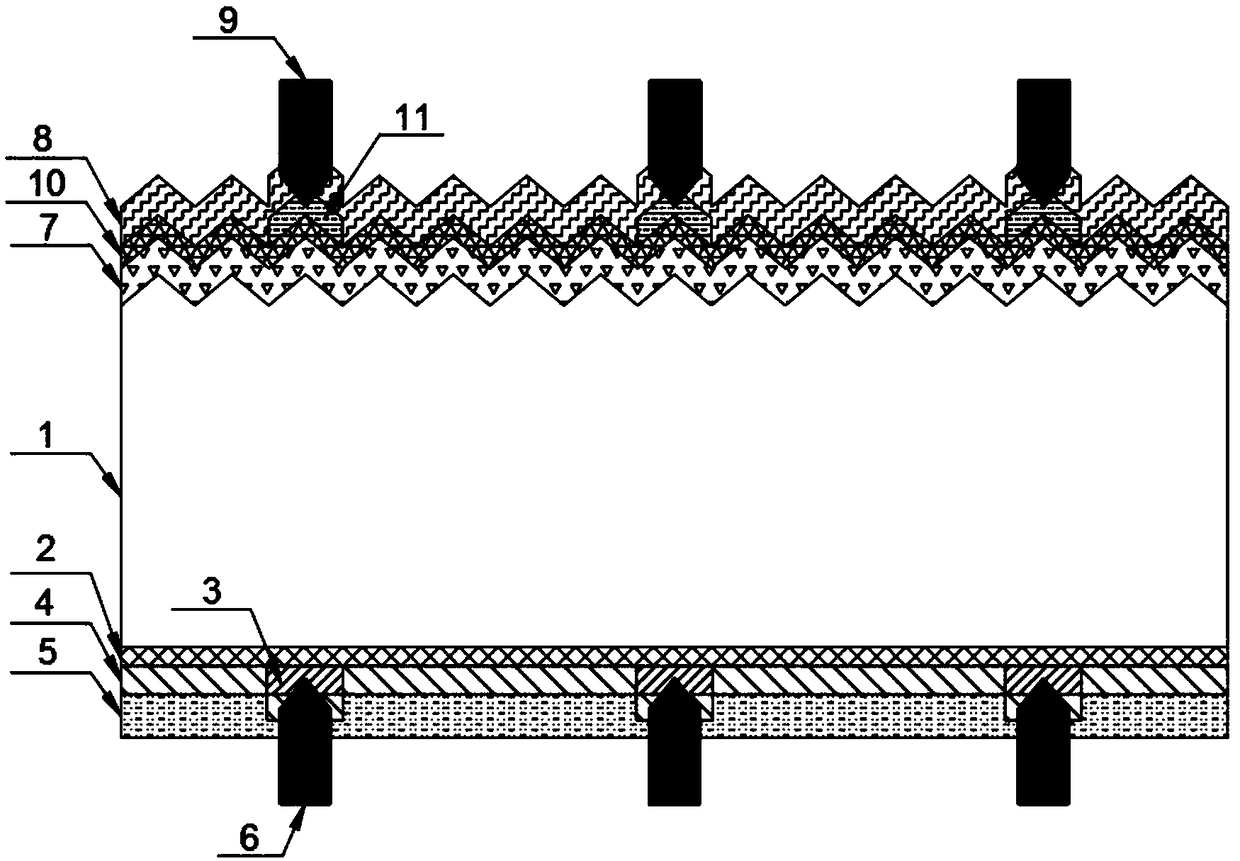

[0151] like figure 2 As shown, in this embodiment, the front side of the silicon-based solar cell includes:

[0152] The emitter layer 7 arranged on the front surface of the P-type crystalline silicon substrate 1,

[0153] a front tunneling passivation layer 10 arranged on the emitter layer 7,

[0154] a group V element-doped front-side doped silicon layer 11 disposed on a partial region of the front-side tunneling passivation layer 10,

[0155] anti-reflection layer 8 disposed on the front-side doped silicon layer 11 and on the region of the front-side tunneling passivation layer 10 where the front-side doped silicon layer 11 is not provided, and,

[0156] A front electrode 9 disposed on the anti-reflection layer 8 .

[0157] Wherein, the front electrode 9 is in ohmic contact with the front doped silicon layer 11 through the antireflection layer 8 .

[0158] In this embodiment, the structures of the emitter layer 7 , the anti-reflection layer 8 and the front electrode 9 ...

Embodiment 1

[0234] This embodiment provides a silicon-based solar cell passivated by gallium oxide, such as figure 1 As shown, the solar cell includes a P-type crystalline silicon substrate 1, an emitter layer 7 arranged on the front of the P-type crystalline silicon substrate 1, an antireflection layer 8 arranged on the emitter layer 7, and an antireflection layer 8 arranged on the antireflection layer 8. The front electrode 9 is arranged on the back tunnel passivation layer 2 on the back of the P-type crystalline silicon substrate 1, and the back doped polysilicon layer doped with boron element is arranged on the back tunnel passivation layer 2 corresponding to the region of the back electrode 6, The gallium oxide layer 4 arranged on the back doped polysilicon layer and the region of the back tunnel passivation layer 2 not provided with the back doped polysilicon layer, the covering layer 5 arranged on the gallium oxide layer 4, and the covering layer 5 arranged on the covering layer 5 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More