Non-junction dual-grid line tunneling field-effect transistor

A technology of tunneling field effect and double gate lines, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of small on-state current of devices and limited tunneling area, so as to increase the on-state current, enhance the electric field, The effect of increasing the tunneling area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

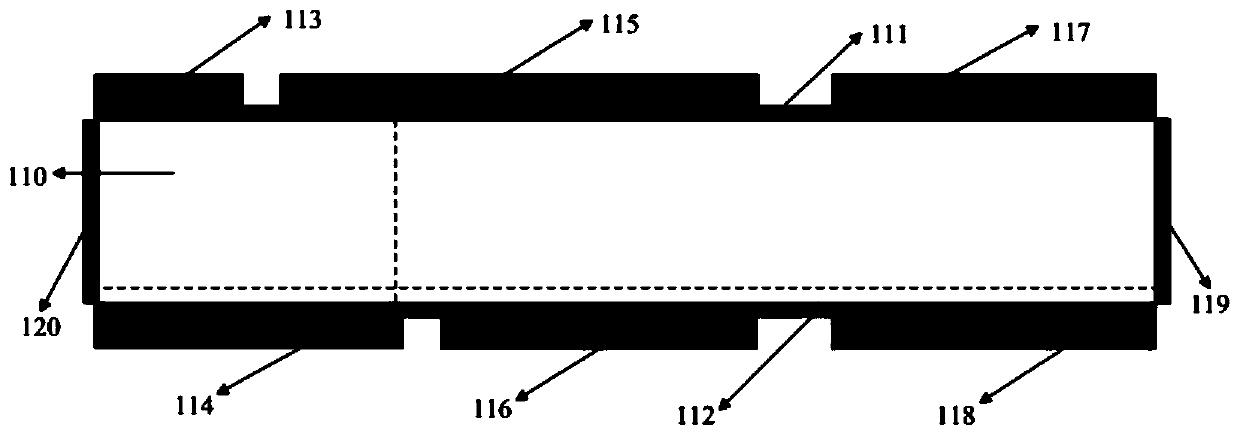

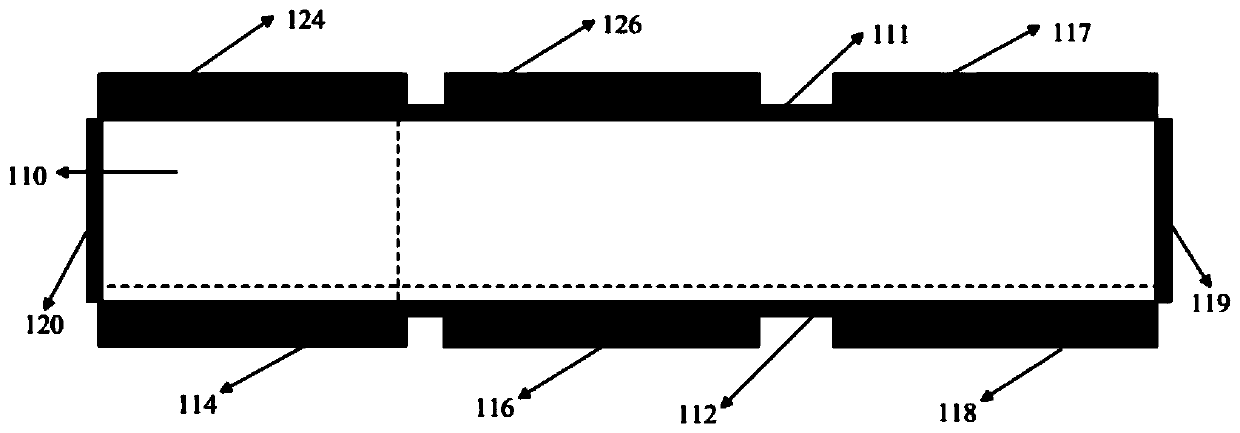

[0026] This embodiment provides a junctionless double gate line tunneling field effect transistor, the structure of which is as follows figure 1 As shown, it includes a channel region (110), an insulating layer, a source metal, a metal gate, a drain metal, a drain electrode (119) and a source electrode (120), wherein the insulating layer includes a top insulating layer (111) , a bottom insulating layer (112), the source metal includes a top source metal (113) and a bottom source metal (114), and the metal gate includes a top metal gate (115) and a bottom metal gate (116), so The drain metal includes the top drain metal (117) and the bottom drain metal (118); wherein,

[0027]The channel region is in the shape of a cuboid, the upper surface of the channel region is covered with a top insulating layer, the lower surface is covered with a bottom insulati...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More