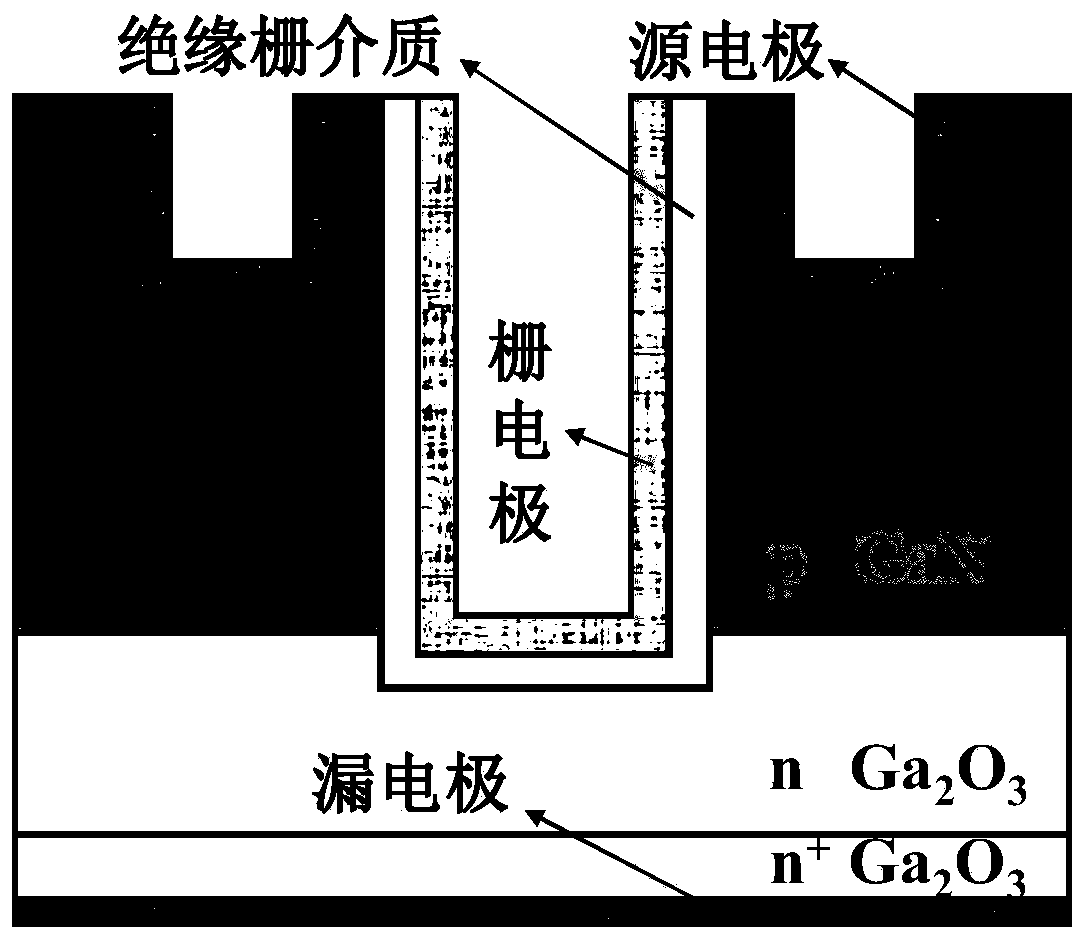

Vertical high-voltage MOSFET device and manufacturing method thereof

A vertical, device technology, applied in the field of microelectronics, can solve the problems of increasing the difficulty of etching and masking, limiting the etching depth, and increasing static power consumption, so as to reduce the difficulty of masking and etching, and reduce the static power consumption. Power consumption and the effect of reducing reverse leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

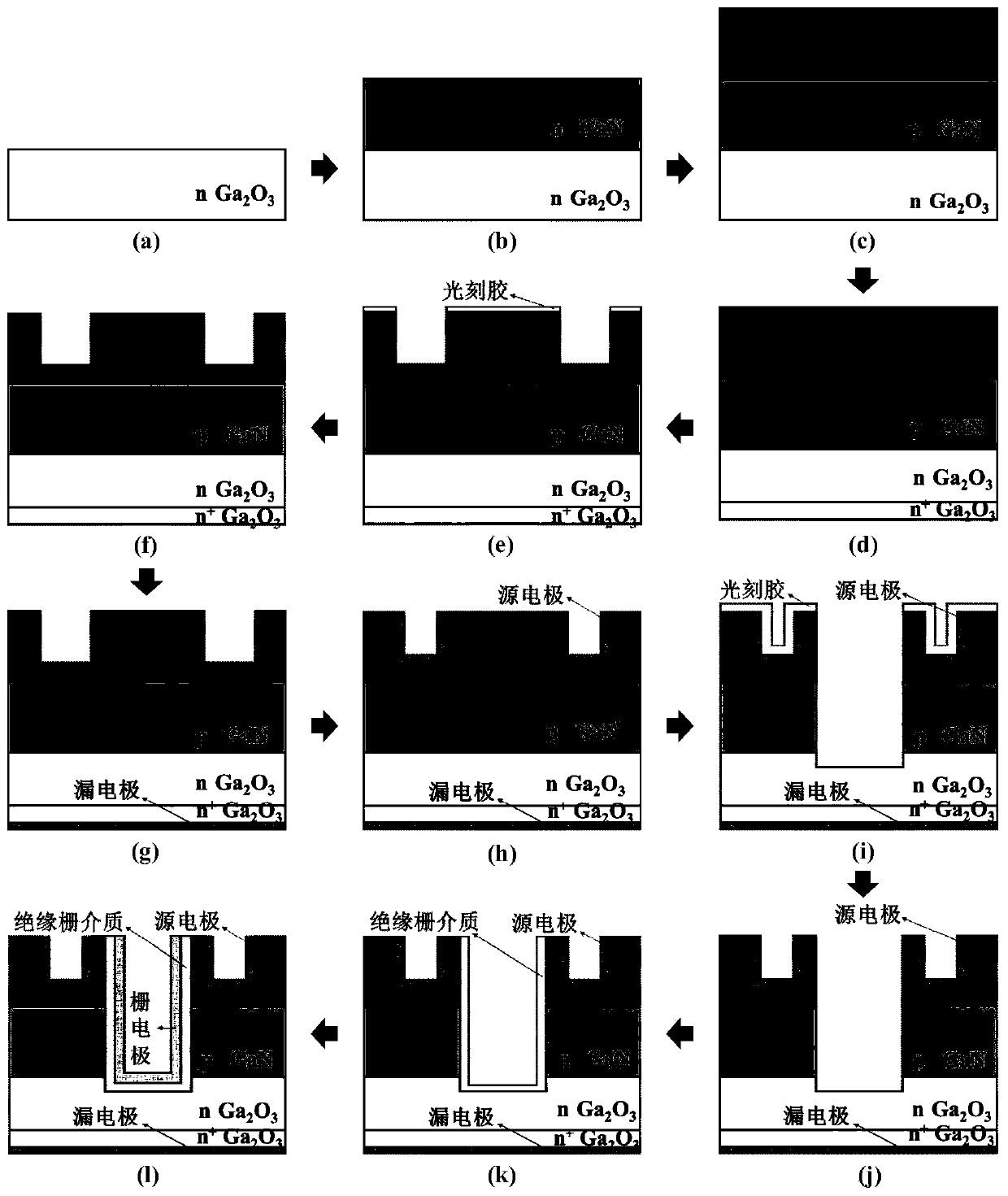

[0040] Embodiment 1, make substrate front electron density be 10 15 cm -3 , the hole concentration of the p-type GaN epitaxial layer is 10 17 cm -3 vertical high voltage MOSFET devices.

[0041] Step 1, carry out organic cleaning to substrate, such as figure 2 (a).

[0042] Use n-type Ga 2 o 3 The substrate was cleaned with flowing deionized water, and then placed in HF:H 2 Corrosion was carried out in the solution of O=1:1 for 30-60s, and finally cleaned with flowing deionized water and dried with high-purity nitrogen.

[0043] Step 2, growing a p-type GaN epitaxial layer on the substrate, such as figure 2 (b).

[0044] Will clean the Ga 2 o 3 Put the substrate into the reaction chamber of the MOVPE equipment, set the pressure of the reaction chamber at 80Torr, the temperature at 600°C, and at the same time feed NH at a flow rate of 800sccm 3 , with a flow rate of 800sccm of trimethylgallium, a 300nm thick GaN film was grown by vapor phase epitaxy; and then anne...

Embodiment 2

[0065] Embodiment 2, making the electron concentration on the front side of the substrate is 5×10 15 cm -3 , the hole concentration in the p-type GaN epitaxial layer is 5×10 17 cm -3 vertical high voltage MOSFET devices.

[0066] Step 1, the substrate is organically cleaned, such as figure 2 (a).

[0067] The specific implementation method of this step is the same as step 1 in embodiment 1;

[0068] Step 2, growing a p-type GaN epitaxial layer on the substrate, such as figure 2 (b).

[0069] Will clean the Ga 2 o 3 The substrate is placed in the reaction chamber of the MOVPE equipment, and a 400nm thick GaN film is grown by vapor phase epitaxy, and then annealed at a temperature of 100°C for 150s to obtain a sample with p-type GaN on the substrate. The process conditions are as follows :

[0070] Set the pressure of the reaction chamber at 100 Torr, the temperature at 700°C, and at the same time feed NH at a flow rate of 1000 sccm 3 , trimethylgallium at a flow ra...

Embodiment 3

[0096] Embodiment 3, make substrate front electron density be 10 16 cm -3 , the hole concentration of the p-type GaN epitaxial layer is 10 18 cm -3 vertical high voltage MOSFET devices.

[0097] Step A, carry out organic cleaning to substrate, as figure 2 (a).

[0098] The specific implementation method of this step is the same as step 1 in embodiment 1;

[0099] Step B, growing a p-type GaN epitaxial layer on the substrate, such as figure 2 (b).

[0100] Will clean the Ga 2 o 3 Put the substrate into the reaction chamber of the MOVPE equipment, set the pressure of the reaction chamber at 150 Torr, and the temperature at 800°C, and simultaneously feed NH with a flow rate of 1400 sccm into the reaction chamber 3 , trimethylgallium with a flow rate of 1400sccm, and a 500nm thick GaN film grown by vapor phase epitaxy;

[0101] Then annealed at a temperature of 1100° C. for 180 s to obtain a sample with p-type GaN growing on the substrate.

[0102] Step C, growing n-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More