A method for manufacturing gate oxide layer for sic power device chip

A technology of gate oxide layer and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as interface state density reduction, gate leakage current increase, SiC device performance impact, etc., to reduce the interface The effect of density of states

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

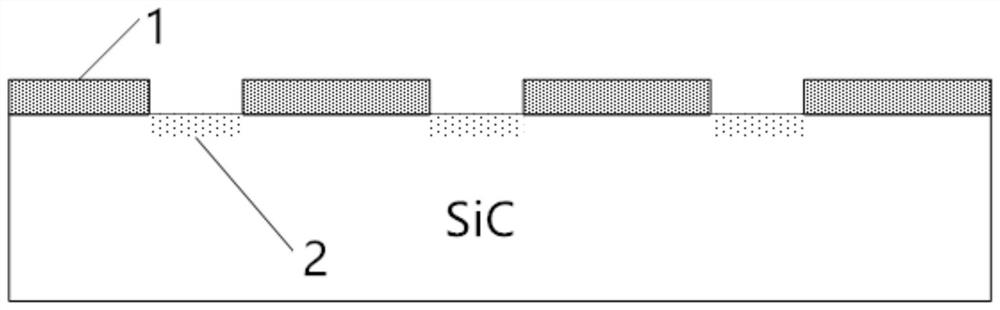

[0032] like figure 1 As shown, step 1: select SiC N-type epitaxial wafer. On the SiC surface, the ion implantation area 2 is divided by the photoresist 1, and the ion implantation area 2 is etched out by photolithography, and P ion implantation is performed three times. The energy of the first implantation is 15KeV, and the dose is 5×10 14 . The energy of the second implant is 10KeV, and the dose is 3×10 14 , the energy of the third implant is 5KeV, and the dose is 1×10 14 .

[0033] Step 2: Perform low-temperature annealing at 850° C. for 15 minutes under NO atmosphere.

[0034] Step 3: Carry out high temperature thermal oxidation (oxygen atmosphere), the thermal oxidation temperature is 1400°C.

[0035] Step 4: After the thermal oxidation is completed, the temperature is not lowered, and the temperature is directly raised under an Ar atmosphere for high-temperature annealing. The heating rate is greater than 30°C / min, the annealing time is 3min, and the annealing temper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More