Semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve problems such as photoresist residue, device leakage current, and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

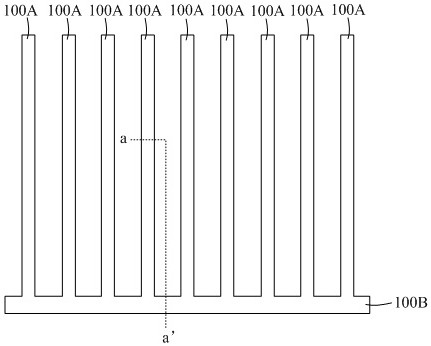

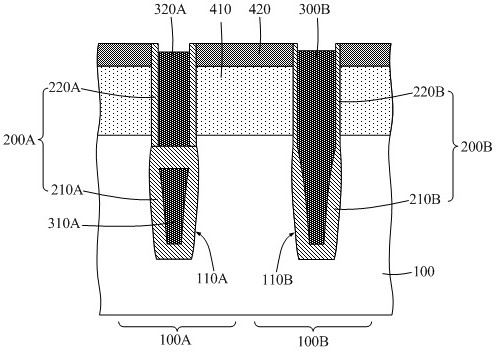

[0090] figure 2 is a layout structure of the semiconductor device in Embodiment 1 of the present invention, image 3 for figure 2 The schematic cross-sectional view of the semiconductor structure in the first embodiment of the present invention in the aa' direction is shown. Such as figure 2 with image 3 As shown, the semiconductor device includes a substrate 100 on which a cellular region 100A and a non-cellular region are defined. Wherein, shielded gate field effect transistors are formed in the cellular region 100A. In this embodiment, the semiconductor device has multiple cellular regions 100A, so that multiple shielded gate field effect transistors can be formed. And, a super barrier rectifier (SBR) is formed in the non-cellular region.

[0091] continue to refer figure 2 with image 3 As shown, the shielded gate field effect transistor includes: a first trench 110A formed in the substrate of the cell region 100A; a first dielectric layer 200A covering the bo...

Embodiment 2

[0122] The difference from Embodiment 1 is that in this embodiment, the non-cellular region includes a rectification region and a source connection region, and the rectification region and the source connection region are respectively located in different regions to perform their corresponding functions. That is, a super-barrier rectifier is formed in the rectification region, and a source connection structure is formed in the source connection region.

[0123] Figure 4 It is the layout structure of the semiconductor device in the second embodiment of the present invention. Such as Figure 4 As shown, the non-cellular region includes a rectification region 100C and a source connection region 100B.

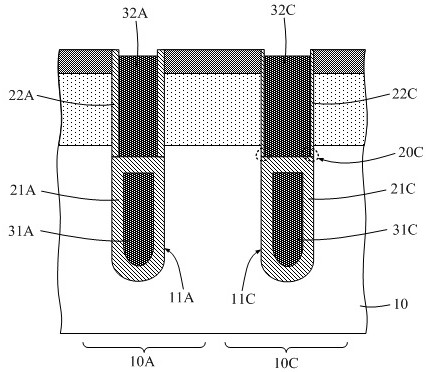

[0124] Wherein, the super-barrier rectifier is formed in the rectification region 100C. Specifically, the second trench of the super-barrier rectifier is formed in the substrate of the rectification region 100C, and the second dielectric layer and the second gate electrode are ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More