Micro-LED chip with epitaxial growth in selected area and preparation method of Micro-LED chip

A selective area epitaxy and chip technology, applied in identification devices, instruments, semiconductor devices, etc., can solve the problems of small improvement, lowering the electrical injection efficiency of p-GaN layer, and the influence of the electrical performance of Micro-LED chips, to prevent crosstalk, improve Display effect, improve the effect of photoelectric performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

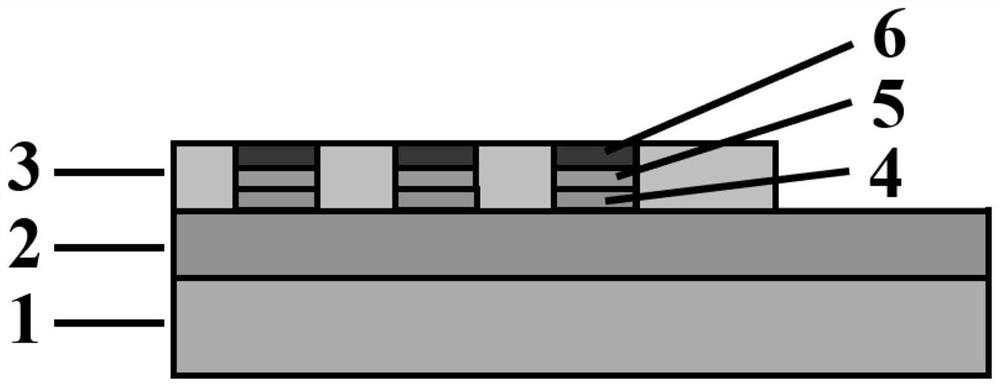

[0045] A method for preparing a Micro-LED chip grown by selective epitaxial growth is provided, which specifically includes the following steps:

[0046] 1) Provide a sapphire substrate with a thickness of 400 μm, and then grow an n-GaN layer 1 with a thickness of 2.5 μm on the sapphire substrate 1 by MOCVD technology;

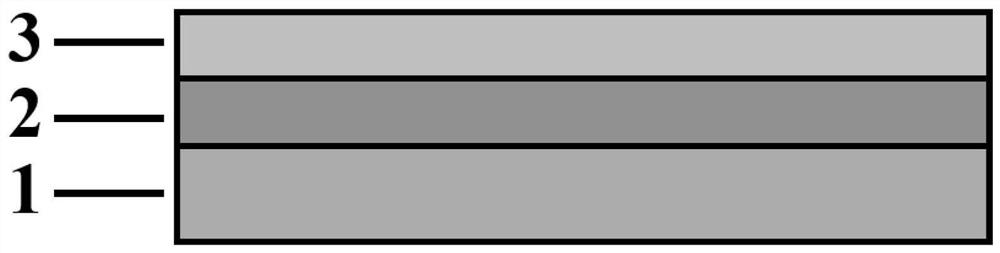

[0047] 2) Deposit SiO on the n-GaN layer 1 obtained in step 1) by PECVD 2 insulating dielectric layer with a thickness of 500nm, such as figure 1 shown;

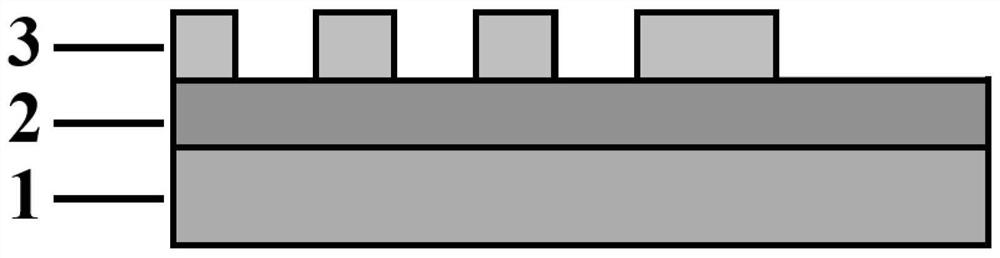

[0048]3) after preparing a mask layer on the insulating dielectric layer obtained in step 2) by using photolithography technology, using ICP etching technology to selectively etch the insulating dielectric layer to obtain a microhole array penetrating through the insulating dielectric layer, and The n-GaN layer 1 is exposed at the edge of one side of the insulating medium layer to obtain a mesa structure of the n-GaN layer 1, wherein the microporous structure is a regular hexagonal prism with a bottom side...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com