Bridging system and bridging method for accessing Flash memory by RISCV processor

A memory and processor technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of large area consumption of bridge modules, RISCV processor and Flash memory cannot be interconnected, etc., to ensure work efficiency, realize high-speed reading, reduce The effect of development difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

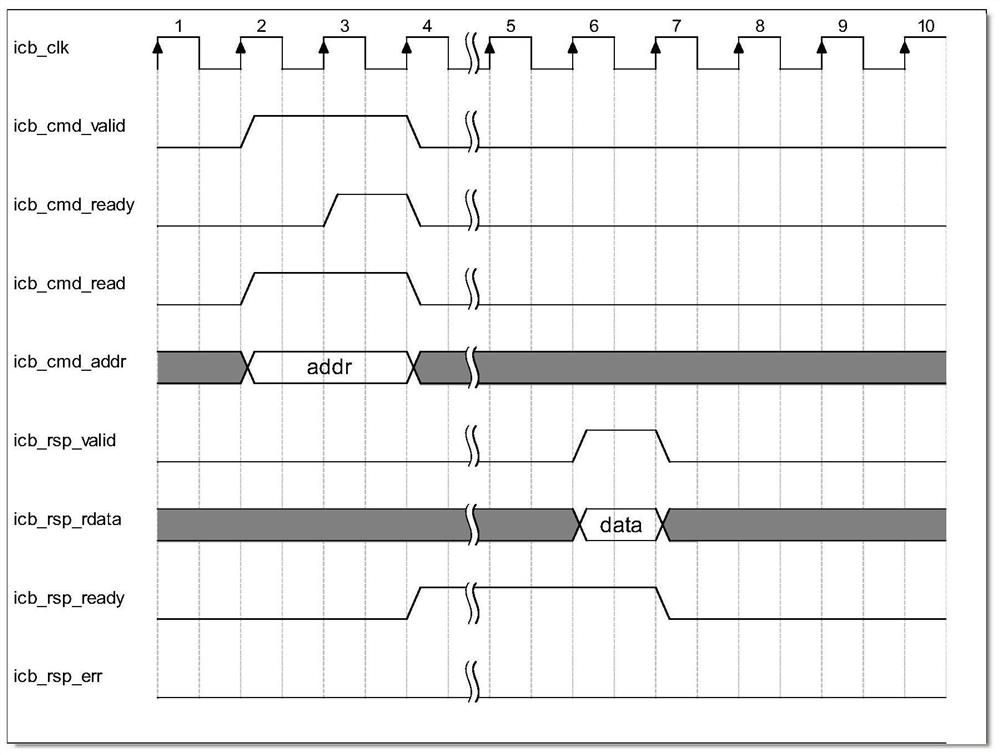

[0032] The read timing diagram of the ICB bus is as follows: figure 1 shown.

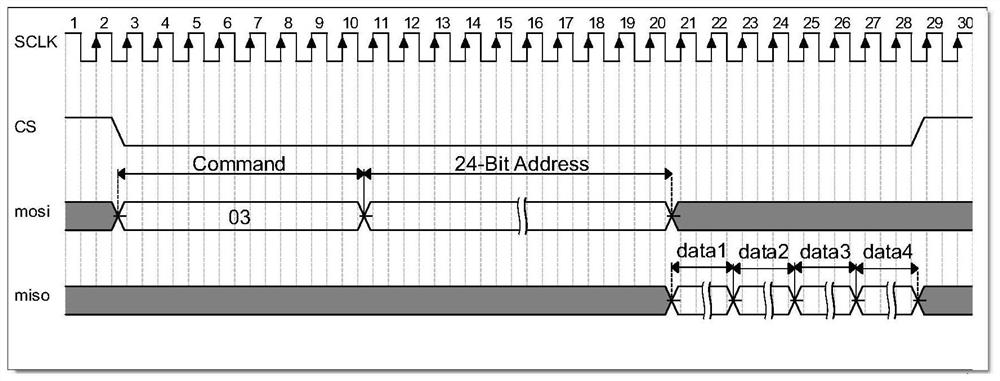

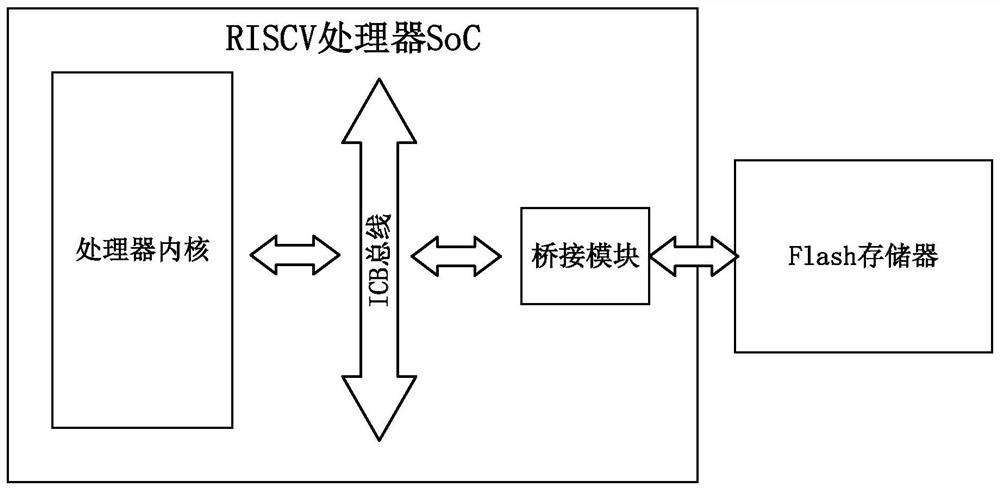

[0033] Flash memory usually adopts SPI bus interface. SPI is a serial peripheral interface, which has the characteristics of synchronous transmission, high transmission rate, full-duplex support, and simple communication method. The SPI bus is only composed of 1 clock line, 1 chip select line and 2 data lines, which can greatly reduce the pin requirements of the processor and reduce the area of the processor. Both the master and slave devices of the SPI bus transmit data on the falling edge, and complete data sampling on the rising edge. The read timing of the Flash memory is as shown figure 2 shown. Described RISCV processor accesses the bridging module of Flash memory, is connected with the ICB bus of RISCV processor by ICB bus interface, is connected with external Flash memory by SPI bus interface, and bridge module realizes RISCV processing as a module of RISCV processor SoC Chip-to-chip i...

Embodiment 2

[0038] The ICB control module mainly works under the drive of the ICB state machine. The ICB state machine includes three states: ICB_IDLE, ICB_REQ, and ICB_WAIT: the ICB_IDLE state is the initial state. When the RISCV processor initiates a read request, the state machine changes from ICB_IDLE to ICB_REQ, and the module Register the control signal and read address signal, and generate a 1-beat ICB start signal; when the ICB end signal is sampled to be valid, the state machine changes from ICB_REQ to ICB_WAIT state, and the module returns the read data on the ICB bus; After the RISCV processor samples the read data, the state machine changes from the ICB_WAIT state to the ICB_IDLE state, waiting for the RISCV processor to initiate the next read request. The state transition of the ICB state machine is as follows Figure 5 shown.

[0039] The SPI control module mainly works under the drive of the SPI state machine. The SPI state machine includes three states: SPI_IDLE, SPI_SEND...

Embodiment 3

[0043] Based on the first and second embodiments above, the specific working process of the present invention is as follows: the interconnection between the RISCV processor and the bridge module is realized through the bus interface of the RISCV processor. The interconnection between the Flash memory and the bridge module is realized through the Flash memory bus interface. According to the requirements of the ICB bus protocol, it receives and responds to the read request initiated by the RISCV processor, and returns the data of the corresponding address of the Flash memory to the ICB control module.

[0044] After the read request initiated by the RISCV processor, the ICB control module starts, analyzes and registers the address and control signal of the ICB bus, and the generated ICB start signal is processed asynchronously by the ICB-SPI interactive module to obtain the SPI start signal, and the SPI start signal The SPI control module can be started. The SPI control module s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More