Semiconductor structure and forming method thereof

A semiconductor and electrode layer technology, which is applied in the fields of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve the problem that the formation method of semiconductor structure needs to be improved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0037] refer to figure 1 , providing a substrate 100.

[0038]In this embodiment, the material of the substrate 100 is silicon. In other embodiments, the material of the substrate is germanium.

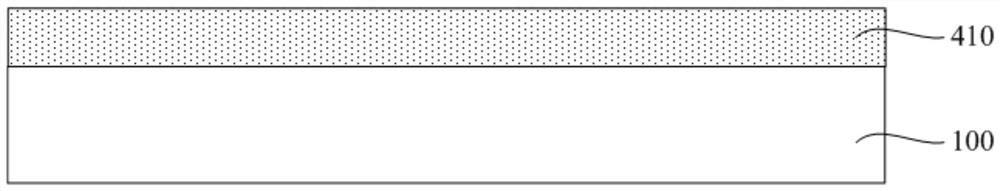

[0039] refer to figure 2 , forming a first electrode layer 410 on the substrate 100 .

[0040] In this embodiment, the material of the first electrode layer 410 is titanium nitride. In other embodiments, the material of the first electrode layer is tantalum nitride.

[0041] The first electrode layer 410 is formed by chemical vapor deposition or atomic layer deposition.

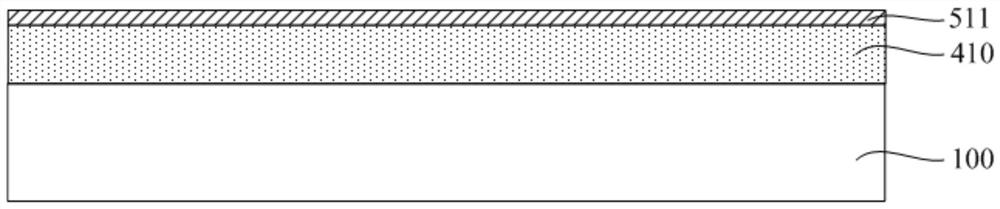

[0042] refer to image 3 , forming a dielectric layer 511 on the first electrode layer 410 .

[0043] The material of the dielectric layer 511 is a high-K dielectric material. In this embodiment, the material of the dielectric layer 511 is HfO 2 ; In other embodiments, the material of the dielectric layer can also be HfSiO, HfSiON, HfTaO, HfTiO, HfZrO or ZrO 2 .

[0044] refer to Figure 4 , forming the...

no. 2 example

[0060] refer to Figure 10 , providing a substrate 100.

[0061] In this embodiment, the material of the substrate 100 is silicon. In other embodiments, the material of the substrate is germanium.

[0062] In this embodiment, the substrate 100 includes a first region I and a second region II.

[0063] refer to Figure 11 , form a dielectric layer 200 on the surface of the substrate 100; etch the dielectric layer 200 to form a plurality of through holes in the dielectric layer 200; form a conductive layer 210 that fills the through holes, and the conductive layer 210 The top is flush with the top of the dielectric layer 200 .

[0064] The material of the dielectric layer 200 is insulating material. In this embodiment, the material of the dielectric layer 200 is silicon oxide. In other embodiments, the material of the dielectric layer is silicon nitride, silicon carbonitride, silicon oxycarbonitride, silicon oxynitride, boron nitride or boron carbonitride.

[0065] In thi...

no. 3 example

[0118] The difference between this embodiment and the second embodiment will be described in detail below. For the formation of the first electrode layer 410 and the previous process steps, reference may be made to the second embodiment, and details are not repeated here.

[0119] refer to Figure 24 and Figure 25 , forming a dielectric layer 511 on the first electrode layer 410 ; forming a second electrode layer 421 on the dielectric layer 511 .

[0120] In this embodiment, the dielectric layer 511 exposes part of the surface of the first electrode layer 410 , and the dielectric layer 511 includes a plurality of sub-dielectric structures 510 arranged in a discrete manner.

[0121] In this embodiment, the second electrode layer 421 includes a plurality of second sub-electrode structures 420 , and the second sub-electrode structures 420 correspond to the sub-dielectric structures 510 one by one.

[0122] The method for forming the dielectric layer 511 and the second electro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More