Multi-channel trench insulated gate bipolar transistor and manufacturing method thereof

A technology of bipolar transistors and insulated gates, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as gate dielectric reliability, reduce conductance modulation effects in drift regions, and device breakdown.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

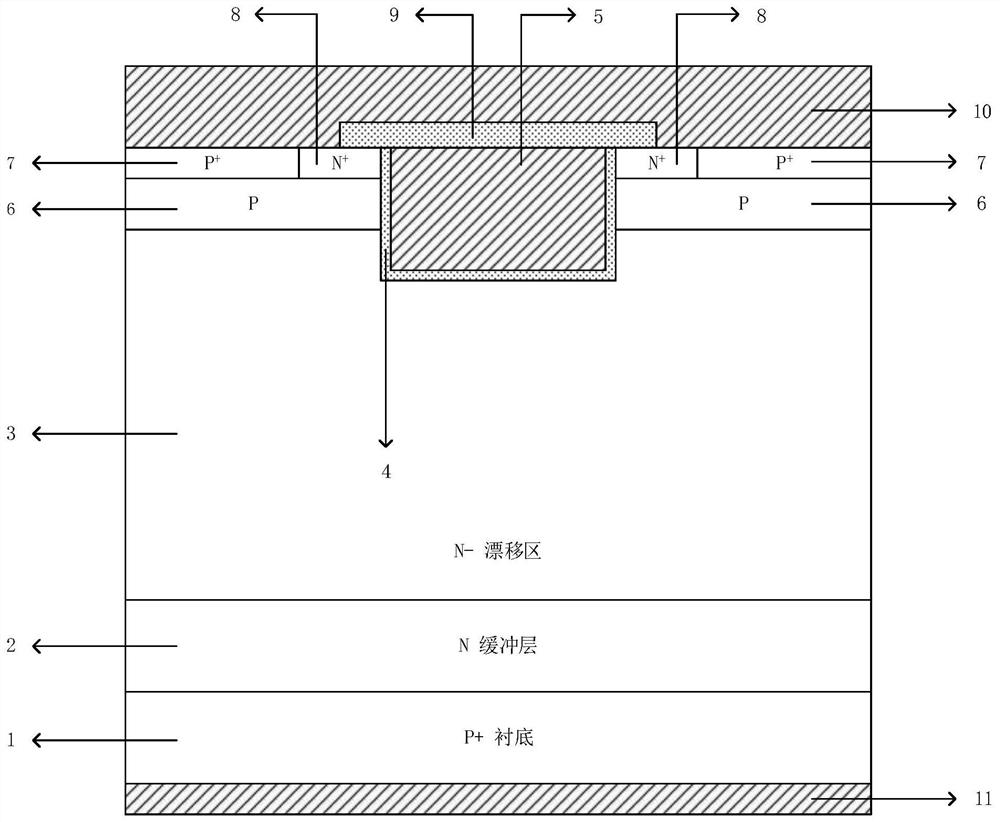

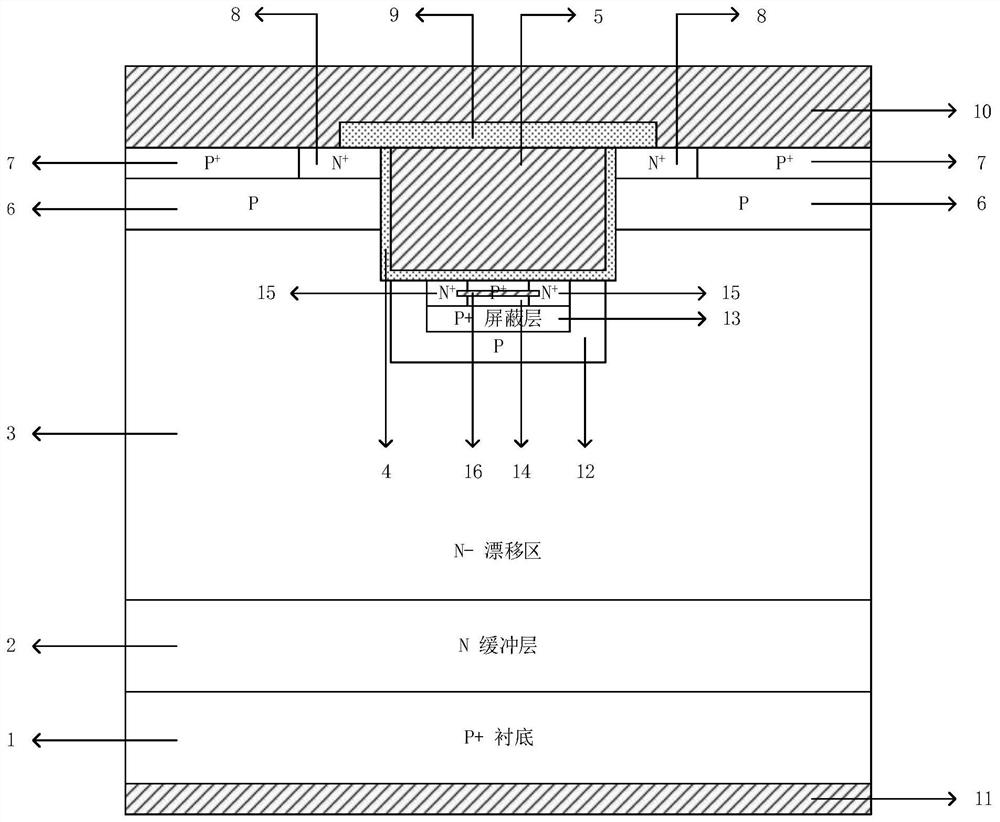

[0039] A multi-channel trench insulated gate bipolar transistor, comprising a P-type substrate 1, a collector metal 11 is arranged on one surface of the P-type substrate 1, and a collector metal 11 is arranged on the other surface of the P-type substrate 1. There is an N-type buffer layer 2, an N-type drift region 3 is arranged on the N-type buffer layer 2, a first P-type base region 6 is arranged on the N-type drift region 3, and a first P-type base region 6 is arranged on the first P-type base region 6. The first P-type contact region 7 and the first N-type emitter region 8, and the first P-type contact region 7 is located outside the first N-type emitter region 8, and a ditch is opened on the first N-type emitter region 8 and the trench is deep into the N-type drift region 3, a gate oxide layer 4 is provided on the inner wall and bottom of the trench, and a polysilicon gate 5 is provided in the gate oxide layer 4, covering the trench There is a passivation layer 9, and a fi...

Embodiment 2

[0048] A method for manufacturing a multi-channel trench insulated gate bipolar transistor,

[0049] Step 1: Take a P-type substrate layer 1, grow and form an N-type buffer layer 2 and an N-type drift region 3 on the P-type substrate layer 1;

[0050] Step 2: using an etching process to open a trench on the N-type drift region 3;

[0051] Step 3: performing ion implantation of P-type impurities at the bottom of the trench to form a second P-type base region 12;

[0052] Step 4: performing ion implantation of P-type impurities to form the P-type shielding layer 13 below the trench;

[0053] Step 5: perform ion implantation of heavily doped P-type impurities to form a second P-type contact region 14 below the trench; then perform ion implantation of N-type impurities to form a second N-type emitter region 15 below the trench;

[0054] Step 6: using a chemical vapor deposition process, forming a gate oxide layer 4 on the sidewall and bottom of the trench and filling the trench ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More