Multi-layer alloy diffusion barrier layer for Cu interconnection integrated circuit and preparation method of multi-layer alloy diffusion barrier layer

A technology for integrated circuits and barrier layers, which is applied in the field of multilayer alloy diffusion barrier layers for Cu interconnected integrated circuits and its preparation, can solve the problems of Cu atom diffusion, etc., and achieve increased diffusion probability, increased activation energy, and low resistivity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

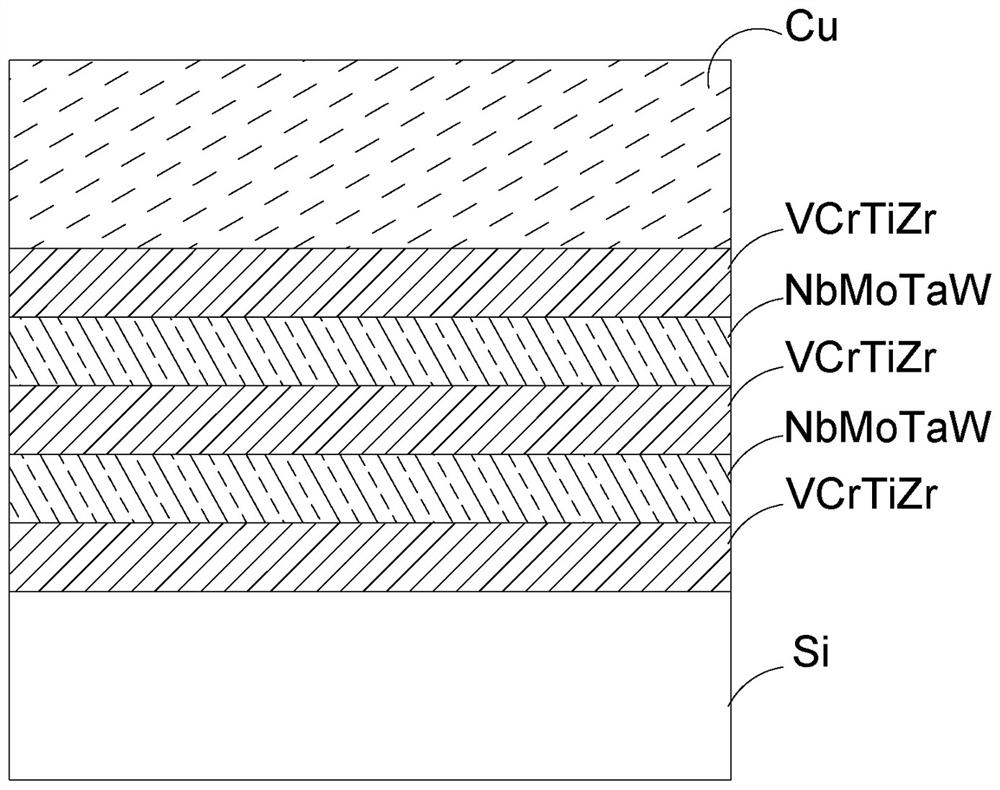

[0023] In another aspect, the present invention also provides a method for preparing a multi-layer alloy diffusion barrier layer for Cu interconnection integrated circuits, comprising the following steps: Step S1, vacuum smelting to obtain a NbMoTaW high-entropy alloy target and a VCrTiZr high-entropy alloy target In step S2, the single crystal Si substrate is cleaned by ultrasonic oscillation to obtain a Si substrate layer; in step S3, the NbMoTaW high-entropy alloy target and the VCrTiZr high-entropy alloy target are pre-sputtered and cleaned; in step S4, the VCrTiZr high-entropy alloy target is cleaned by pre-sputtering. The alloy target is sputtered on the Si substrate layer by a DC magnetron sputtering process to form a VCrTiZr high-entropy alloy coating; step S5, the NbMoTaW high-entropy alloy target is sputtered on the VCrTiZr high-entropy alloy coating by a DC magnetron sputtering process. layer to form a NbMoTaW high-entropy alloy coating; step S6, repeat steps S4 and ...

Embodiment 1

[0031] Mix Nb, Mo, Ta, and W in an equimolar ratio, and smelt 5 times in a vacuum electric furnace to obtain a NbMoTaW high-entropy alloy target with uniform composition; V, Cr, Ti, and Zr are mixed in an equimolar ratio, and smelted in a vacuum electric furnace 5 times to obtain a VCrTiZr high-entropy alloy target with uniform composition; before sputtering the high-entropy alloy intermediate coating, the Si substrate was ultrasonically cleaned with acetone, alcohol and deionized water in turn to remove surface oxides or impurities; The impurities on the VCrTiZr and NbMoTaW targets were cleaned by pre-sputtering, the power was 30 W, and the time was 2 minutes; the prepared VCrTiZr high-entropy alloy targets were sputtered on the Si lining by a DC magnetron sputtering process in an Ar atmosphere. On the bottom layer, a VCrTiZr high-entropy alloy coating is formed, when the base pressure reaches 2.0×10 −4 At Pa, argon gas was introduced, the flow rate was 25sccm, the working pr...

Embodiment 2

[0035] Mix Nb, Mo, Ta, and W in an equimolar ratio, and smelt 5 times in a vacuum electric furnace to obtain a NbMoTaW high-entropy alloy target with uniform composition; V, Cr, Ti, and Zr are mixed in an equimolar ratio, and smelted in a vacuum electric furnace 5 times to obtain a VCrTiZr high-entropy alloy target with uniform composition; before sputtering the high-entropy alloy intermediate coating, the Si substrate was ultrasonically cleaned with acetone, alcohol and deionized water in turn to remove surface oxides or impurities; The impurities on the VCrTiZr and NbMoTaW targets were cleaned by pre-sputtering, the power was 30 W, and the time was 2 minutes; the prepared VCrTiZr high-entropy alloy targets were sputtered on the Si lining by a DC magnetron sputtering process in an Ar atmosphere. On the bottom layer, a VCrTiZr high-entropy alloy coating is formed, when the base pressure reaches 2.0×10 −4 At Pa, argon gas was introduced, the flow rate was 25sccm, the working pr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| purity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More