Process for making super-thin silicon nitride / silicon oxide grid electrode dielectric layer

A gate dielectric layer and manufacturing method technology, applied in the field of ultra-thin silicon nitride/silicon oxide gate dielectric layer manufacturing, can solve the problem of high process thermal budget, increase process complexity and instability, and reliable components sexual degeneration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

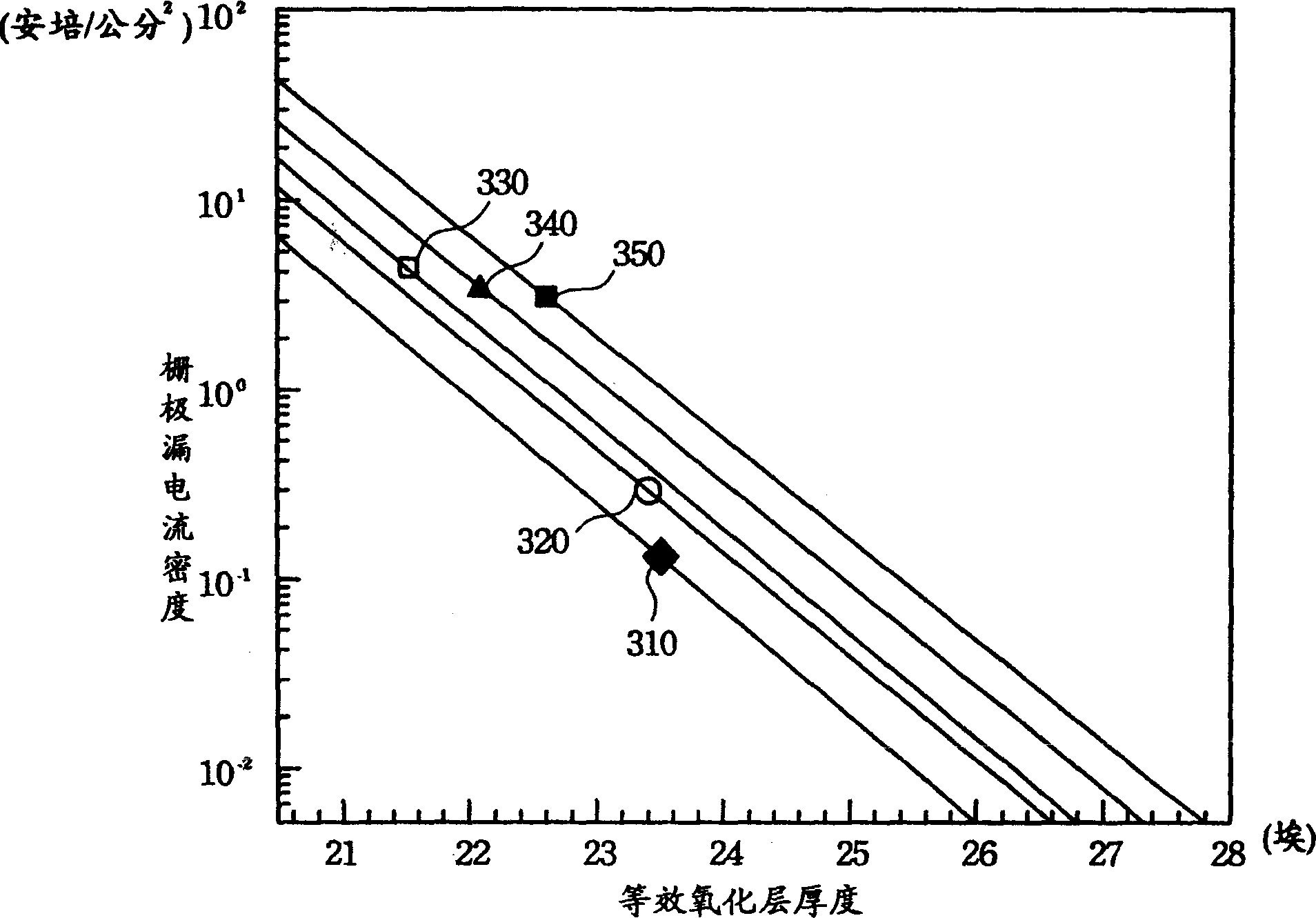

[0021] Due to the existing methods of manufacturing ultra-thin silicon nitride / silicon oxide gate dielectric layers in the background of the invention, an annealing treatment must be used to optimize the silicon nitride deposition process to reduce the defect density of the film. However, the annealing process causes the diffusion of impurities in the substrate, resulting in deterioration of device characteristics. Moreover, the multiple annealing processes of temperature rise and fall also increase the complexity and uncontrollability of the entire process, and further reduce the production capacity. Furthermore, the nitridation with ammonia gas further causes high concentration of hydrogen in the dielectric layer, which degrades the reliability of the device.

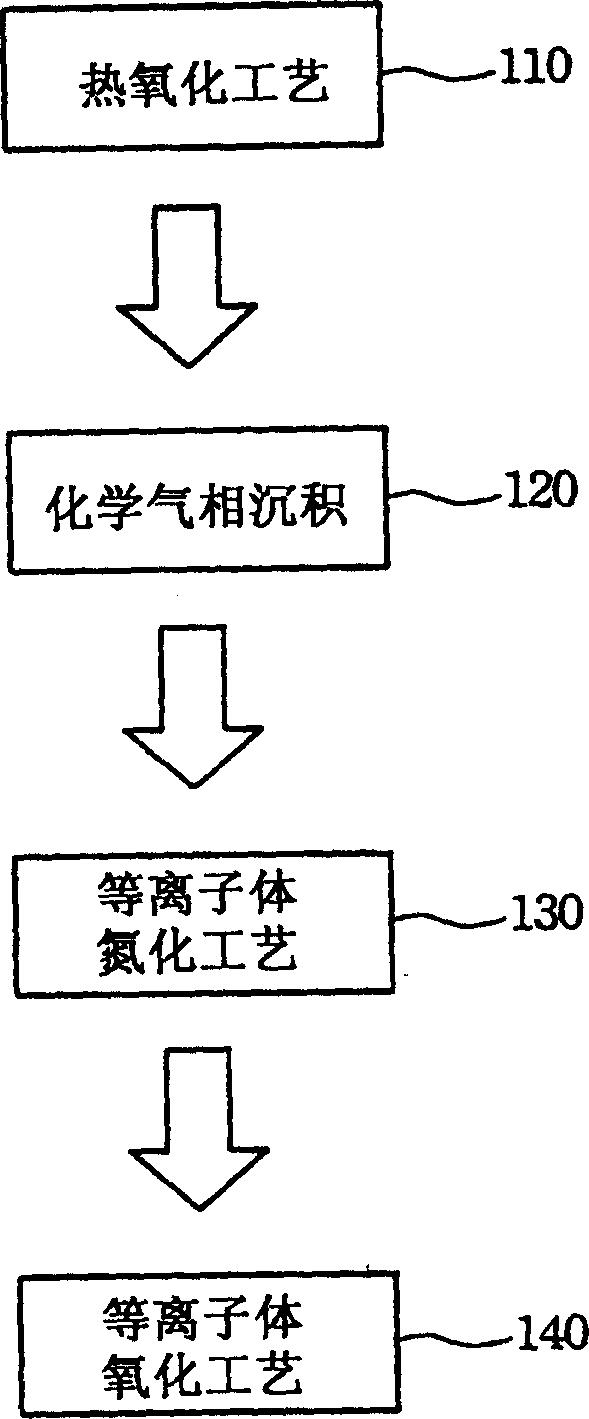

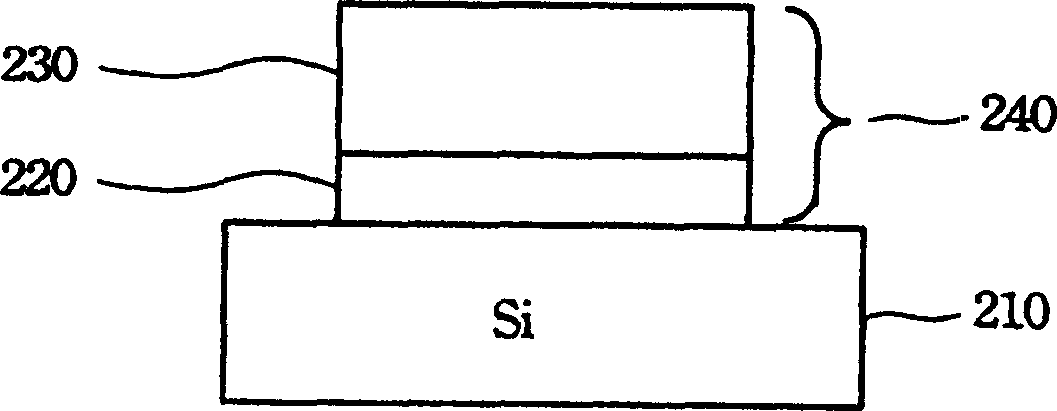

[0022] The invention provides a method for manufacturing an ultra-thin silicon nitride / silicon oxide gate dielectric layer, which utilizes N 2 Plasma nitriding process and O 2 or N 2 O plasma re-oxidation process t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More