Method for eliminating primary pit defects of silicon monocrystal device making area

A silicon single wafer, native technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

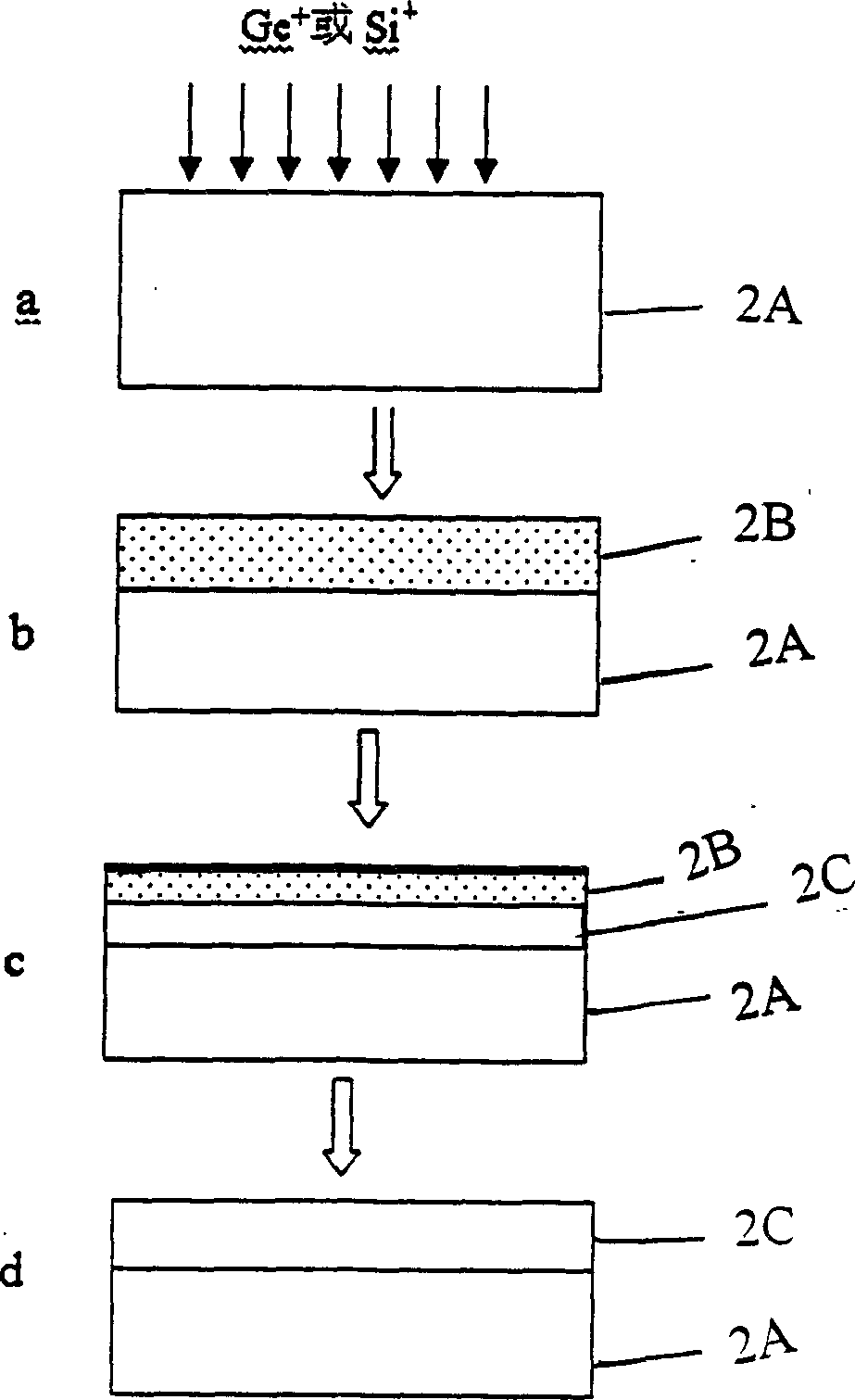

Method used

Image

Examples

Embodiment 1

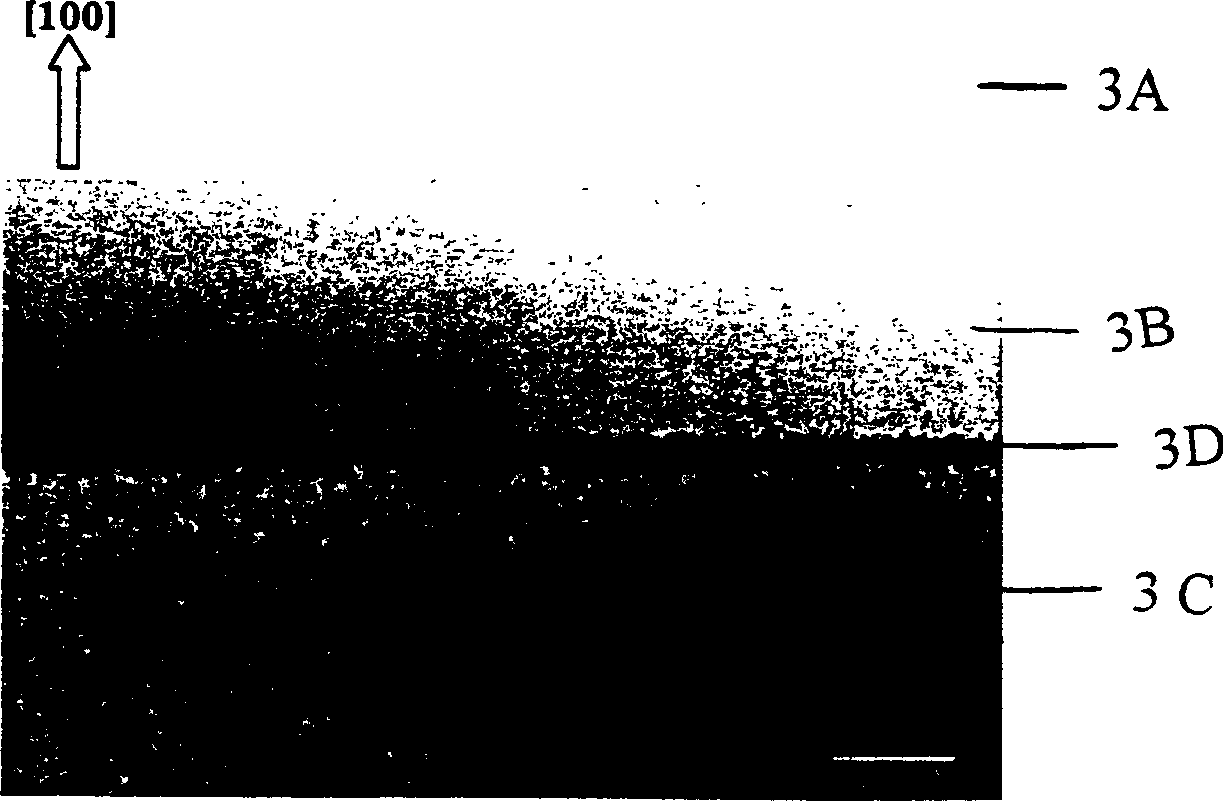

[0128] In this embodiment, a boron-doped Czochralski P-type silicon single crystal polished wafer with a diameter of 150 mm facing (100) is used as the original silicon wafer. The resistivity is 15-25Ωcm, and the original silicon wafer is cleaned to remove all kinds of pollution on the surface of the original silicon wafer. The cleaning process adopts the standard RCA process, in the pre-annealing cleaning machine of K·C·TECH (produced by KOCK TECK company) cleaning. First, wash with No. 1 solution (SC-1) at a temperature of 70°C to clean off the particles on the surface of the silicon wafer; the used SC-1 solution consists of ammonium hydroxide, hydrogen peroxide and water in a volume ratio of 1:1:5 It is formulated, then rinsed with deionized water, and cleaned with No. 2 solution. The No. 2 solution is prepared by mixing commercially available hydrochloric acid, hydrogen peroxide and water at a volume ratio of 1:1:5 to clean off the surface of the silicon wafer. Metal cont...

Embodiment 2

[0150] Its processing steps and related equipment are basically the same as in Example 1, except that the annealing is carried out in the SHS100 rapid heat treatment furnace produced by Steag AST Company. This equipment utilizes light heating, that is, heating with a tungsten halogen lamp, which can greatly reduce the temperature of silicon wafers. The time of heat treatment.

[0151] The specific process steps of rapid heat treatment are as follows:

[0152] (1) The silicon wafer whose surface layer has been amorphized is placed in the furnace cavity of the SHS100 rapid heat treatment furnace, and the furnace cavity is flushed with argon (or nitrogen), and the flow rate of the argon gas is 17 standard cubic centimeters per minute.

[0153] (2) Reduce the flow rate of argon gas for flushing the furnace cavity to 4 standard cubic centimeters per minute, and rapidly raise the temperature to 900° C., with a heating rate of 40° C. / s.

[0154] (3) In the atmosphere of argon gas, t...

Embodiment 3

[0157] Its operating steps and equipment are basically the same as in Embodiment 1, except that silicon ions are implanted so that the incident ion silicon has an implantation energy of 200KeV, and the dose of implanted Si ions is 5×10 14 Si + / cm 2 , the average implantation depth is 300nm, and the implantation temperature is 298K.

[0158] Implanted Si by furnace annealing heat treatment + The silicon wafer after ionization, its specific steps are:

[0159] (1) The flow rate of filling nitrogen gas is 8 standard cubic liters per minute, and the pressure of argon gas in the furnace cavity is 0.2Mpa.

[0160] (2) Raise the temperature in the furnace chamber at a rate of 25° C. / min, and send the silicon wafer whose surface layer has been amorphized into the furnace chamber at a temperature of 800° C. in the furnace chamber.

[0161] (3) Raise the temperature in the furnace chamber to 1000° C. at a rate of 25° C. / min.

[0162] (4) Furnace annealing was carried out at constant...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More