Semiconductor device having a stacked capacitor

a technology of stacked capacitors and semiconductor devices, which is applied in the direction of semiconductor devices, capacitors, electrical equipment, etc., can solve the problems of tantalum oxide problems, difficult to use hsg structures, and difficult to meet the requirements of stacked capacitors, etc., to achieve the effect of reducing leakage current, reducing thickness, and reducing the thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

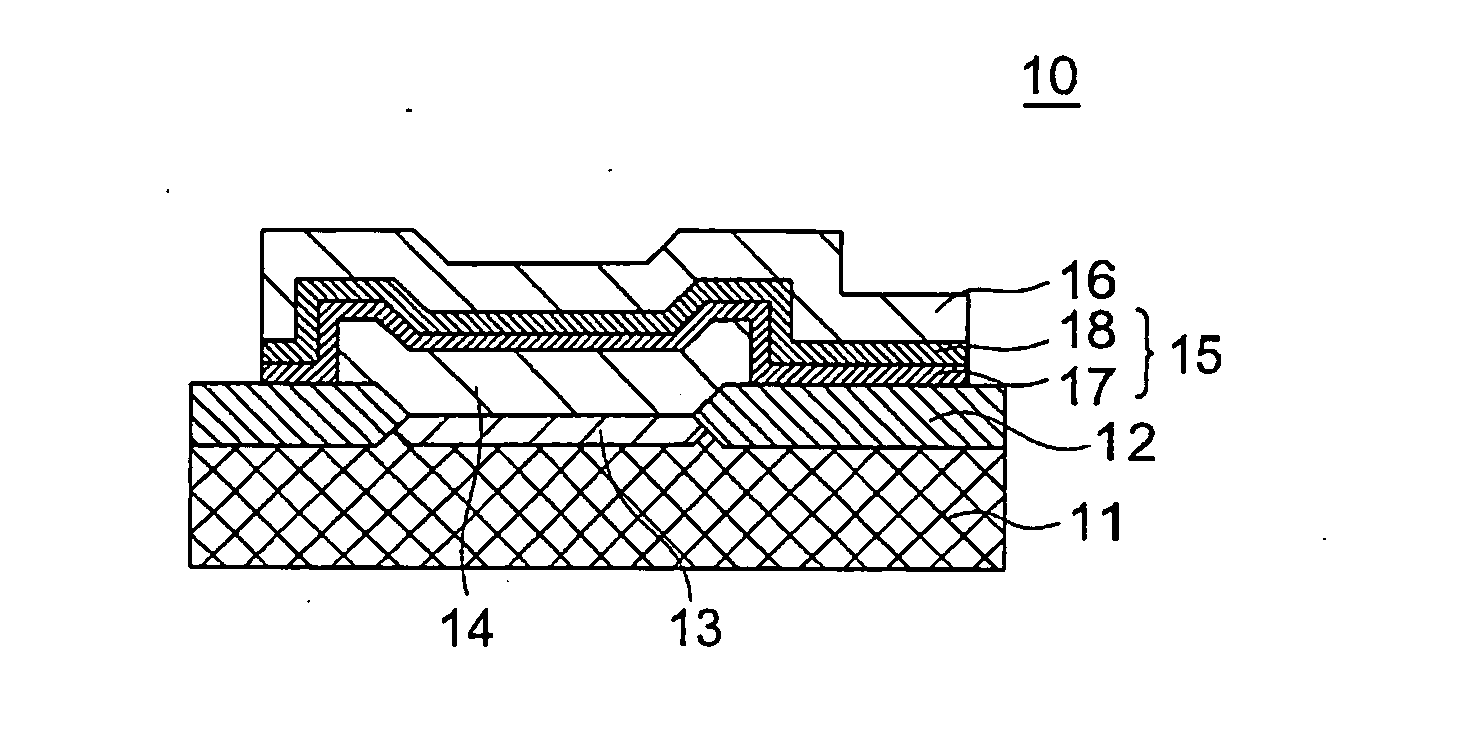

[0091] Now, the embodiments of the present invention are specifically described with reference to accompanying drawings. FIG. 20 shows a layer structure of a capacitor in a semiconductor device according to the present invention. The semiconductor device 10 includes a silicon substrate 11, a LOCOS film 12 formed on the silicon substrate 11 for isolation of element regions, a titanium silicide film 13 formed on the element region of the silicon substrate 11, and a layered structure of a capacitor formed on the titanium silicide film 13. The capacitor includes a bottom electrode 14 made of titanium nitride formed on the titanium silicide film 13, a capacitor insulation film 15 having a two-layer structure, and a top electrode 16 made of titanium nitride. Other insulator films and interconnect patterns are omitted for depiction in the drawing.

[0092] The titanium silicide film 13 reduces the contact resistance between the bottom electrode 14 and the silicon substrate 11. The capacitor i...

second embodiment

[0110] A semiconductor device of a modification from the second embodiment shown in FIG. 24 is such that the hafnium oxide 22 sandwiched between the aluminum oxide films 21 and 23 in FIG. 24 has a polycrystalline structure. The term polycrystalline structure used herein means that every measurable area has an exclusive crystalline structure and does not assume an amorphous state. The polycrystalline structure can be identified using an X-ray diffraction technique or transmission electron microscope.

[0111] In manufacture of the semiconductor device of the modification, formation of the bottom electrode 14 is followed by consecutively depositing 2-nm-thick aluminum oxide 21, 3-nm-thick hafnium oxide 22 and 2-nm-thick aluminum oxide 23, all of them in an amorphous state. Thereafter, in a nitrogen atmosphere, a heat treatment is performed at a temperature of 700 degrees C. for 3 minutes. Since the crystallizing temperature for the hafnium oxide 22 is 550 degrees C., the hafnium oxide 22...

third embodiment

[0116]FIG. 29 shows a semiconductor device according to the present invention. The semiconductor device 100 configures a DRAM device including a memory cell area 100A wherein a plurality of memory cells are arranged in a matrix on a p-type silicon substrate 101. The silicon substrate 101 includes an n-well 102 in the surface region thereof, and a first p-well 103 in the surface region of the n-well 102. The DRAM device 100 also includes a peripheral circuit area 100B, wherein the silicon substrate 101 includes a second p-well 104 in the surface region thereof, the second p-well 104 being isolated from the first p-well 103 by an element isolation area 105.

[0117] Switching transistors 106, 107 each configuring a memory cell are formed on the first p-well 103. Transistor 106 includes a drain 108, a source 109, and a gate electrode 111 formed on the silicon substrate 101 with an intervention of a gate insulation film 110. Transistor 107 includes the source 109 provided in common with tr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thicknesses | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More