Semiconductor device including bipolar transistor and buried conductive region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

(First Embodiment)

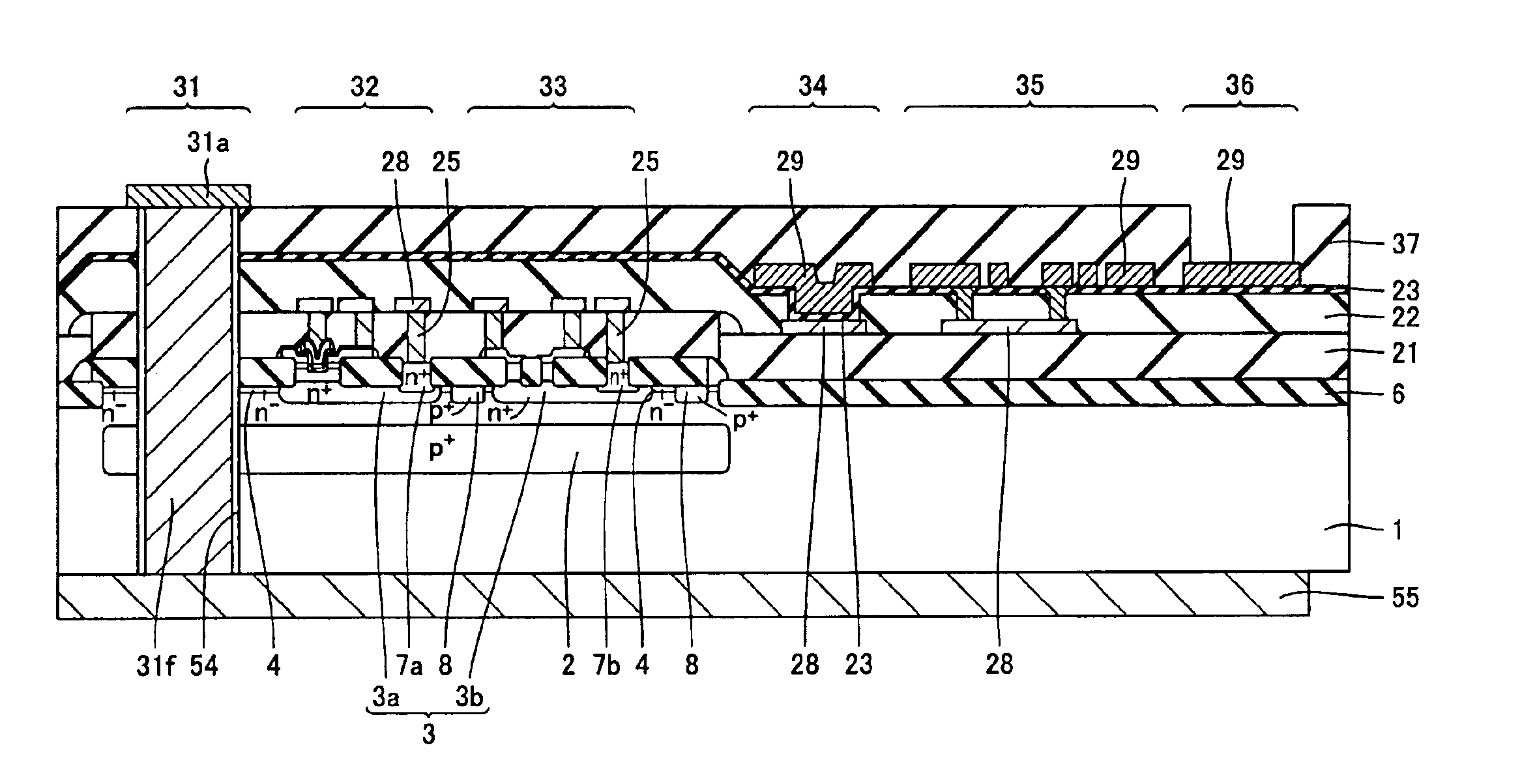

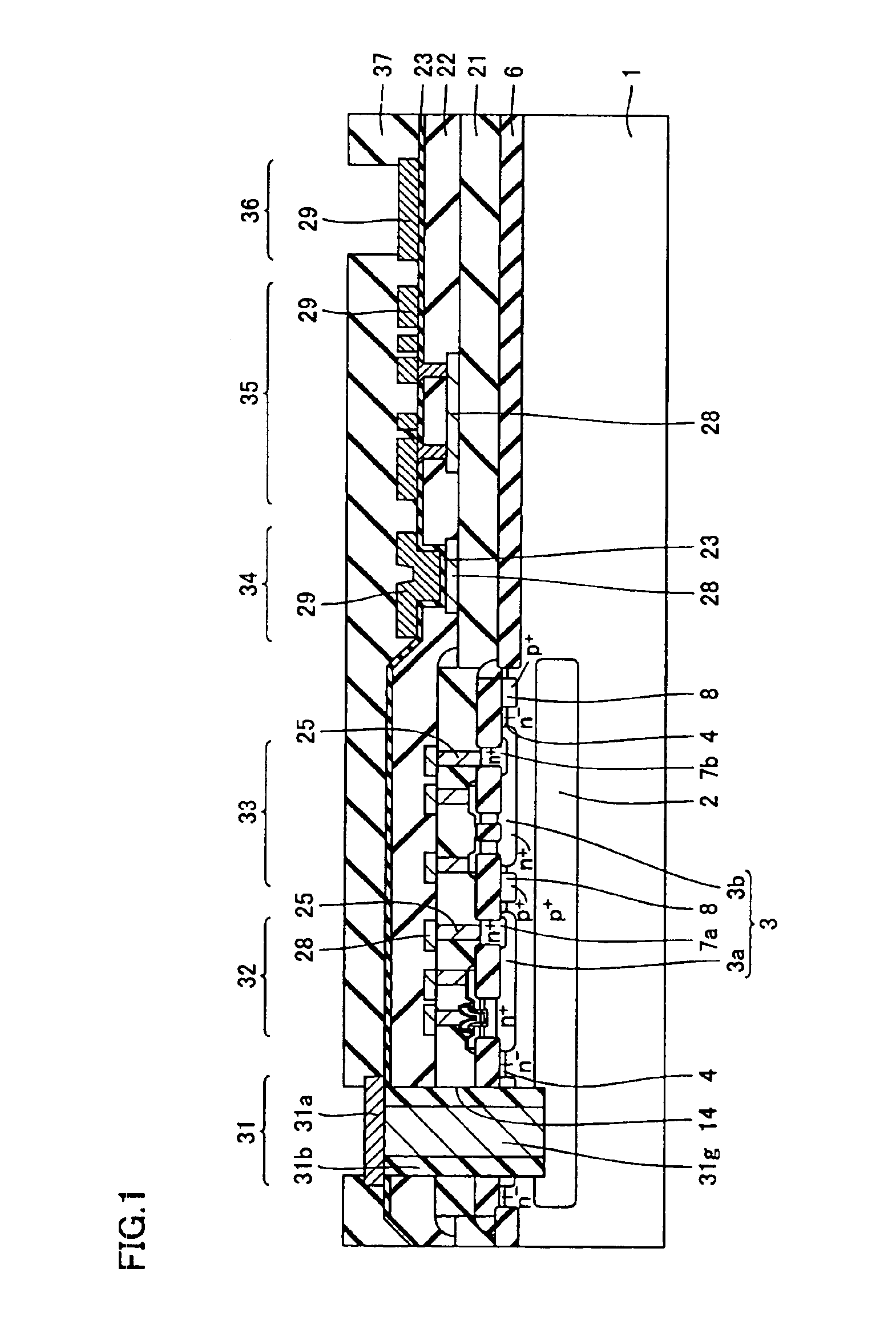

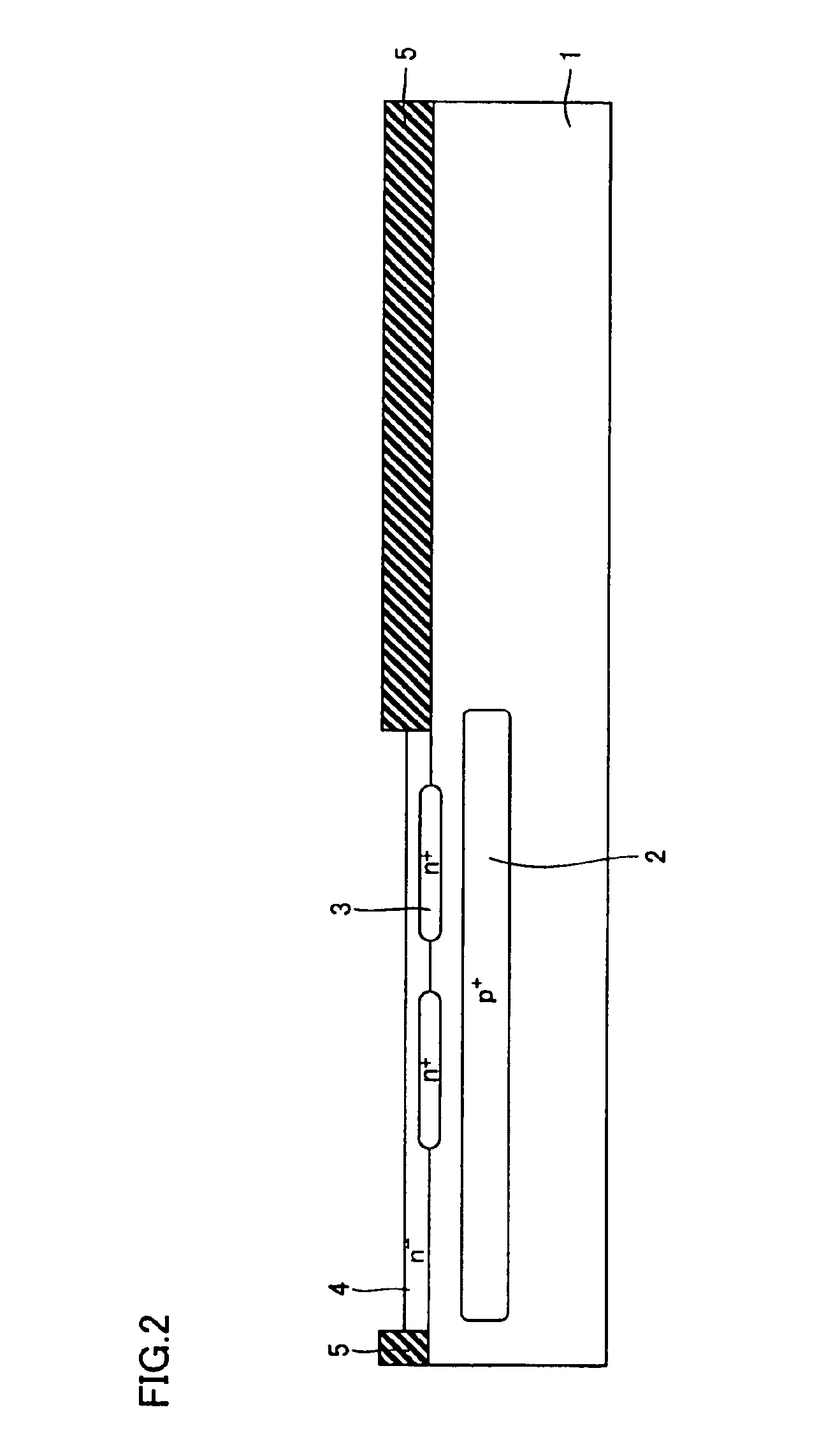

[0037]In FIG. 1, a buried layer 2 of a p conductive type is placed in an Si substrate 1 having a specific resistance of no less than 100 Ωcm and a vertical npn transistor 32 and a horizontal pnp transistor 33, which are active elements, are provided above this buried layer 2 of the p conductive type. A leading electrode 31 is electrically connected to buried layer 2 of the p conductive type and an electrode portion 31a of the leading electrode is placed on a plug wire 31g so as to be exposed from the upper surface of the semiconductor device. Plug wire 31g of this leading electrode is provided in an opening 14 that penetrates interlayer insulating films 21 and 22 and an epitaxial growth layer 3 located there beneath and reaches to buried layer 2 of the p conductive type. The sidewalls of this opening 14 are covered with an oxide film 31b and a Ti film, a TiN film or an Al film forming leading electrode terminal 31a is provided above oxide film 31b.

[0038]A collecto...

second embodiment

(Second Embodiment)

[0062]A base is formed of SiGe in the semiconductor device according to the second embodiment of the present invention. The configuration of this semiconductor device is the same as in the semiconductor device shown in FIG. 1. The semiconductor device according to the present embodiment is characterized by the point that the base is formed of SiGe and it is easier to understand the characteristics of this device by beginning the description from the manufacturing method.

[0063]The manufacturing method of the semiconductor device according to the present embodiment is the same as in the first embodiment up to the step of FIG. 3. Next, as shown in FIG. 8, an Si epitaxial layer 58, an SiGe epitaxial layer 60 and an Si epitaxial layer 62 are made to sequentially grow from below in this order so as to cover the entirety of the wafer. At this time, an Si film or an SiGe film grows as a polycrystal film above an element isolation insulating film 6. Si epitaxial film 58 fo...

third embodiment

(Third Embodiment)

[0071]In reference to FIG. 14, the third embodiment has a structure wherein a contact of a buried layer 2 of a p conductive type or of a substrate 1 is formed of a layer 31c of a p+ conductive type, formed in an Si substrate and in an epitaxial layer 4 of an n− conductive type, a tungsten (W) plug 31d electrically connected to this layer of the p+ conductive type and an Al wire 31e connected to this W plug. The W plug may be separated into a plurality of pieces or may have a layered structure.

[0072]The above described structure is formed as follows. As the next stage after the process of FIG. 2, as shown in FIG. 15, impurities of a p conductive type are implanted into the opening for a leading electrode provided in an element isolation insulating film 6 so that region 31c of the p+ conductive type is formed. This region of the p+ conductive type is formed so as to be electrically connected to buried layer 2 of the p+ conductive type. After this, the process steps o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More