Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of large performance differences of semiconductor devices and reduced performance of semiconductor devices, and achieve the effect of reducing performance differences and improving performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063] In order to make the object, technical solution and advantages of the present invention clearer, the solutions of the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0064] Figure 13 It is a flowchart of a manufacturing method of a semiconductor device provided by the present invention. Such as Figure 13 As shown, the method includes the following steps:

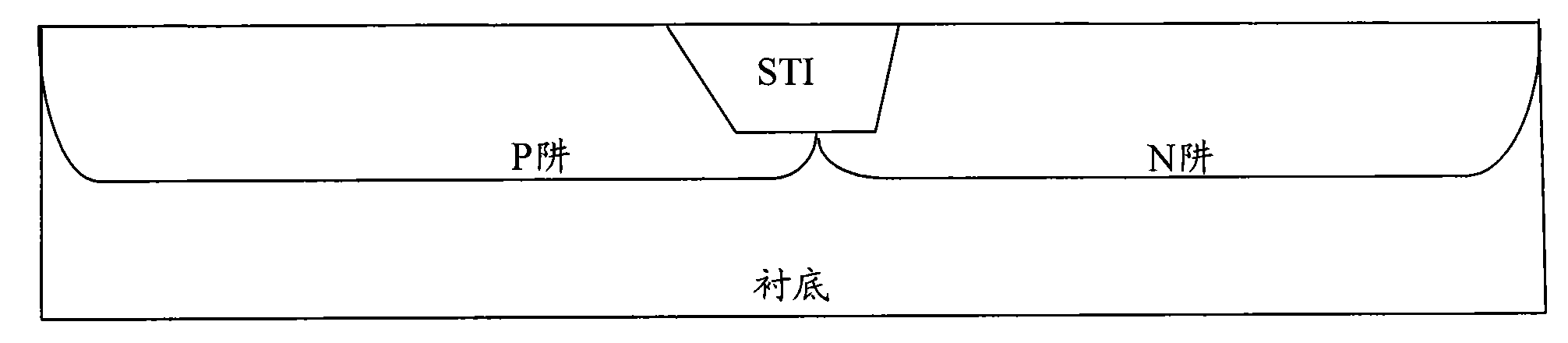

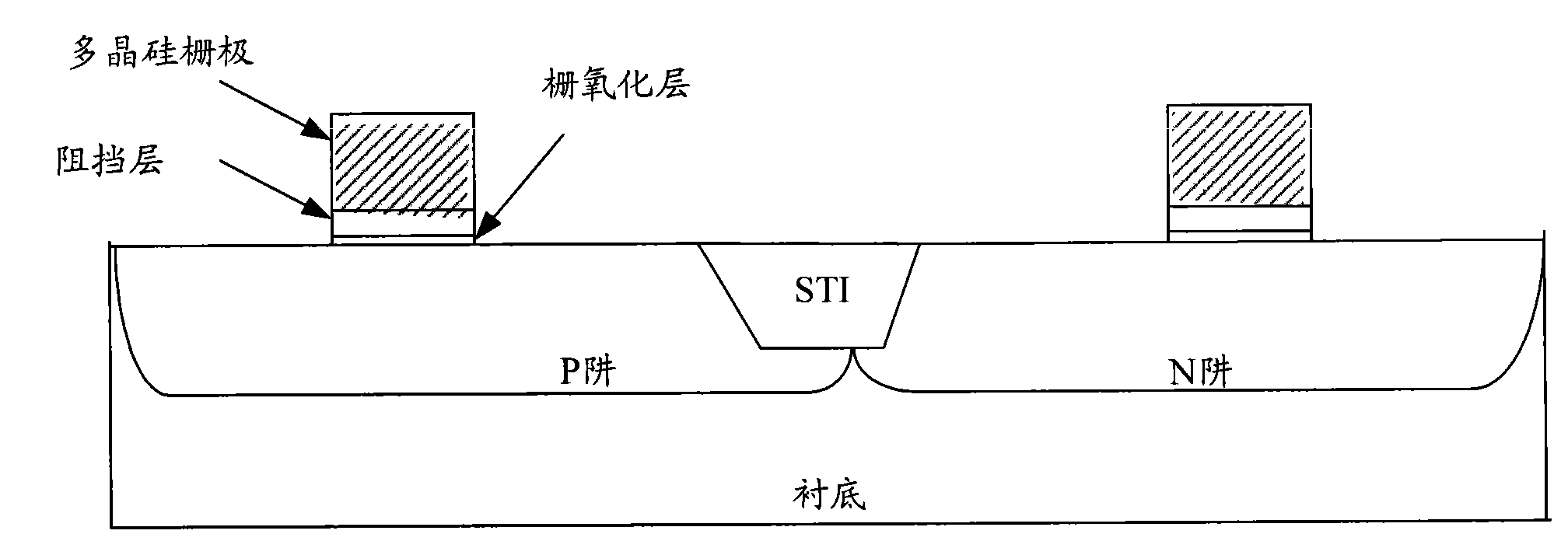

[0065] In step 201, an STI for isolating the active region is formed in the substrate, and a high dielectric constant gate oxide layer, a titanium nitride barrier layer and After the temporary polysilicon gate, auxiliary sidewall layers on both sides of the temporary polysilicon gate of the NMOS transistor and the PMOS transistor are formed.

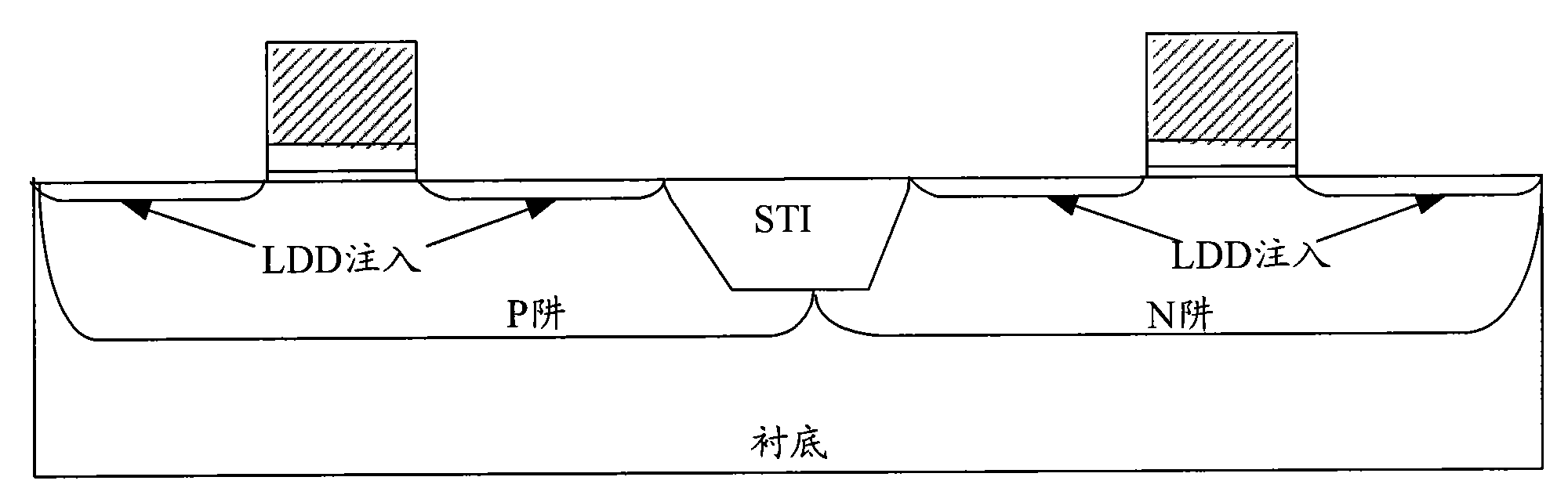

[0066] Step 202 , perform LDD implantation on the substrate on both sides of the temporary polysilicon gates of the NMOS transistor and the PMOS transistor.

[0067] Step 203 , forming sidewall layers ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More