Asymmetrical multichip system level integrated packaging device and packaging method for same

A technology of integrated packaging and packaging methods, which is applied in the manufacture of semiconductor devices, electrical solid state devices, semiconductor/solid state devices, etc., can solve the problems of high aspect ratio and cost, and achieve the effects of high frequency integration, low RC delay, and wide application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be described in detail below in conjunction with the accompanying drawings.

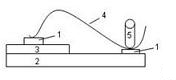

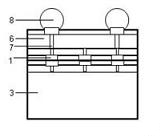

[0033] In the drawings: 1 pad, 2 substrate, 3 bottom chip, 4 connection wire, 5 bonding head, 6 top chip, 7 penetrating silicon channel, 8 solder ball, 9 spacer barrier layer, 10 metal line in chip, 11 Plasma generator, 12 plasma vent ring, 13 vacuum cover, 14 failure pad, 15 redundant repair pad, 16 redundant repair metal layer, 17 transistor, 18 polymer, 19 small pad, 20 vacuum pressure welding suction head, 21-wafer mobile platform.

[0034] image 3 , Figure 4 It is a structural schematic diagram of an embodiment of the present invention. Including: pad 1, such as CU, substrate, such as PCB 2, bottom chip 3, connection wire 4, such as AL, top chip 6, and metal wire 10 in the chip. Through the face-to-face contact between the top chip and the bottom chip, the pads 1 of the top chip and the bottom chip are bonded, and the bottom chip is connected to the substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More