Monolithic integration processing method for unequal-height silicon structure and integrated circuit

A technology of integrated circuits and processing methods, applied in the field of single-chip integrated processing of high-silicon structures and integrated circuits, which can solve problems affecting device performance and achieve the effect of ensuring performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

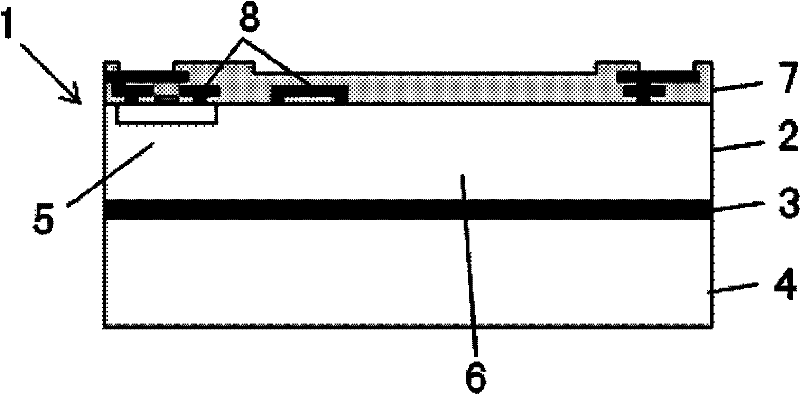

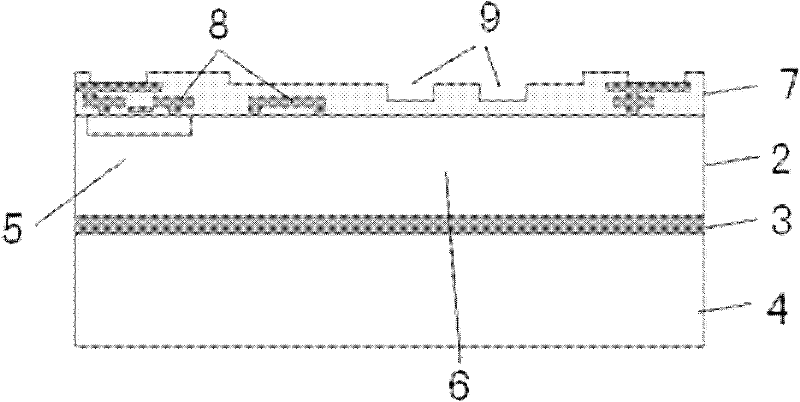

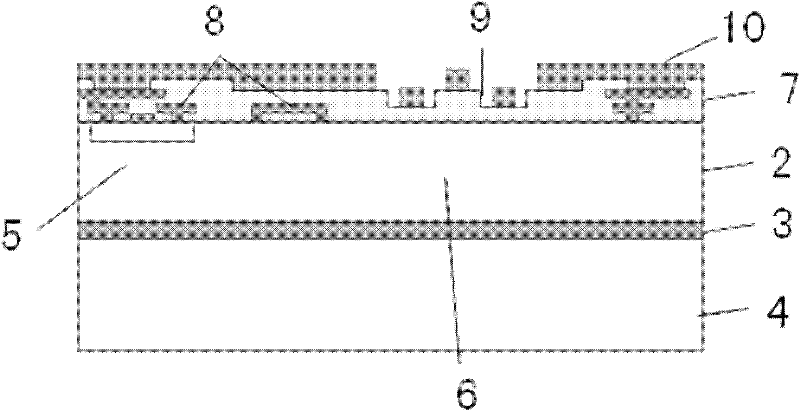

[0024] Such as figure 1 Shown, the present invention adopts and realizes integrated circuit processing on SOI (Silicon-on-insulator silicon on insulator) substrate, and it comprises the steps:

[0025] 1) select SOI substrate 1, SOI substrate 1 includes device layer 2, buried oxide layer 3 and substrate layer 4, wherein, device layer 2 is made of integrated circuit region 5 and MEMS (micro-electromechanical system) structure region 6; Wherein, The silicon structure corresponding to the integrated circuit region 5 and the silicon structure corresponding to the MEMS structure region 6 are mechanically connected through the buried oxide layer 3 and the substrate layer 4 .

[0026] 2) Integrated circuit processing is carried out on the integrated circuit area 5 of the SOI substrate 1, and a dielectric layer 7 of silicon oxide or silicon nitride is genera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More