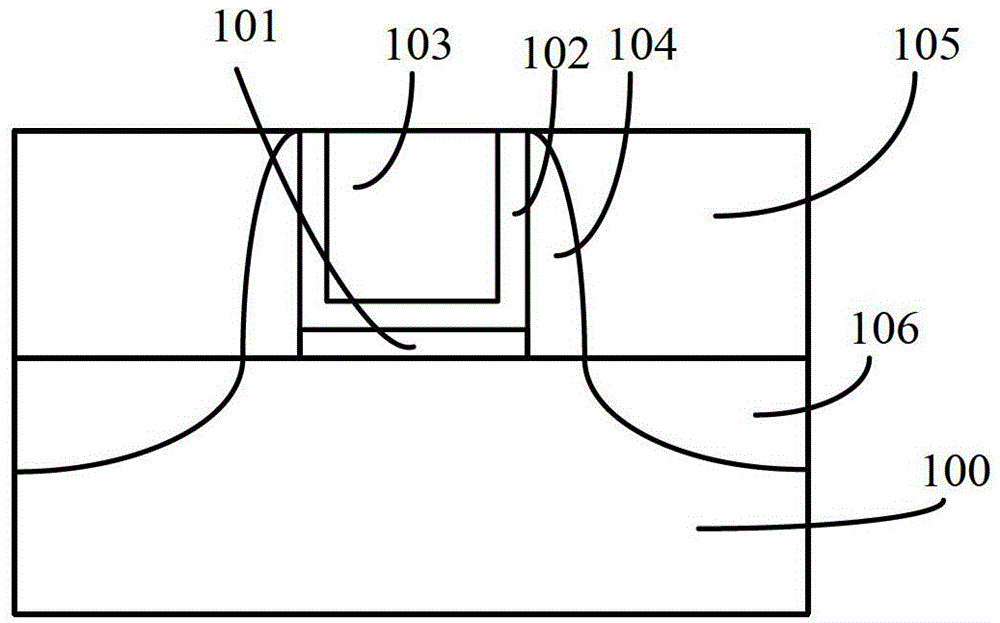

How the transistor is formed

A technology of transistors and semiconductors, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as poor performance and short channel effect, achieve excellent performance, precise size, avoid leakage current or short channel Tao effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

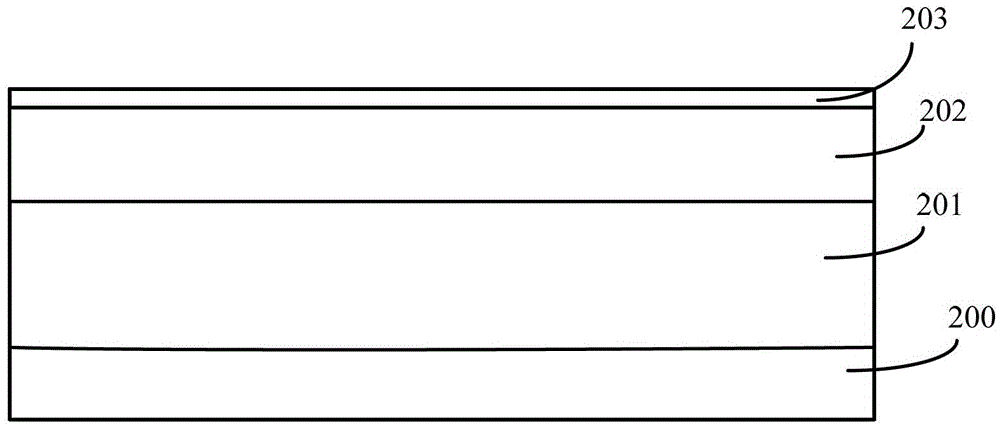

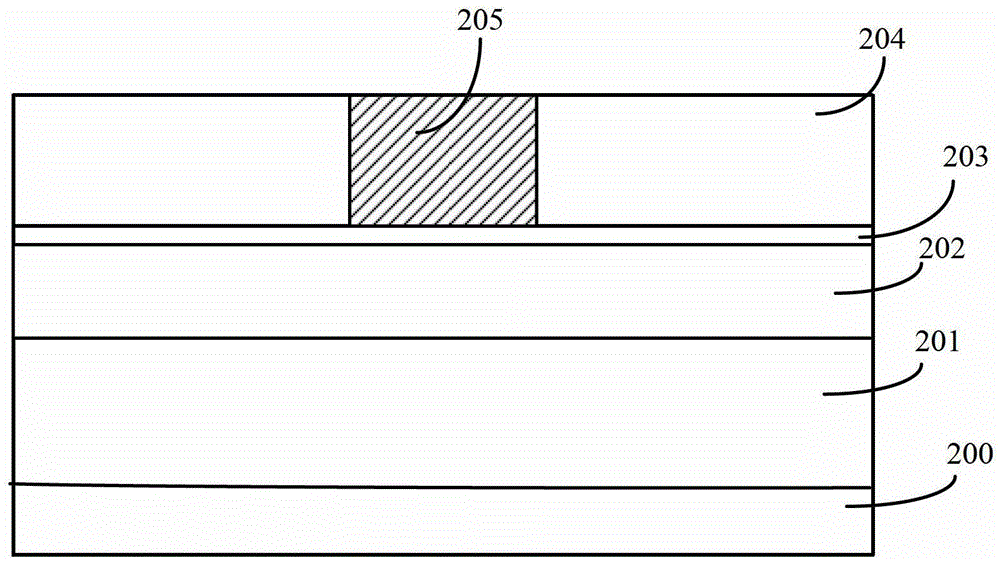

[0037] Figure 2 to Figure 7 It is a schematic cross-sectional structure diagram of the method for forming a transistor described in the first embodiment of the present invention.

[0038] Please refer to figure 2 , providing a semiconductor substrate 200 with an active region 201, performing ion implantation in the active region 201 to form a doped layer 202, the implanted ions are p-type or n-type, and the surface of the doped layer 202 is in contact with the semiconductor The surface of the substrate 200 is flush; the doped layer 202 is activated by a thermal annealing process.

[0039] The semiconductor substrate 200 is used to provide a working platform for subsequent processes; the semiconductor substrate 200 is a silicon substrate, a silicon germanium substrate, a silicon carbide substrate or a silicon-on-insulator (SOI) substrate.

[0040] The doped layer 202 is formed by an ion implantation process, and the implanted ions are subject to the type of transistor to be...

no. 2 example

[0073] Figure 8 to Figure 10 is a schematic cross-sectional structure diagram of the method for forming a transistor described in the second embodiment of the present invention.

[0074] Please refer to Figure 8 , providing a semiconductor substrate 300 with an active region 301, performing ion implantation in the active region 301 to form a doped layer 302, the implanted ions are p-type or n-type, the surface of the doped layer 302 is in contact with the semiconductor substrate The surface of the bottom 300 is flush; the doped layer 302 is activated by a thermal annealing process; after the doped layer 302 is activated, a dielectric layer 304 and a dummy gate layer (not shown) are formed on the surface of the doped layer 302 ), the dielectric layer 304 covers the sidewall of the dummy gate layer; using the dielectric layer 304 as a mask, etch the dummy gate layer and the doped layer 302 until the doped layer 302 is penetrated The opening 306 is formed until the active reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More