Substrate based bumped flip chip CSP (Chip Scale Package) package part, substrate and manufacturing method

A flip-chip, manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as large differences and mismatched thermal expansion coefficients, and achieve small capacitance, thin shape, and good heat dissipation performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

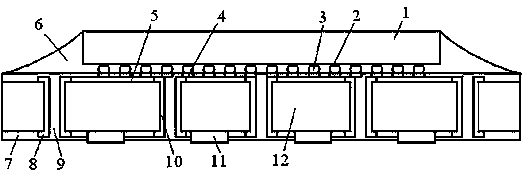

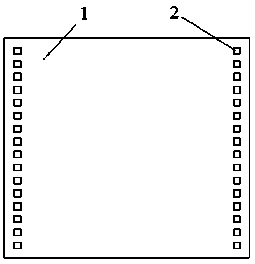

Embodiment 1

[0085] Design the substrate according to the requirements of use; the raw material of the substrate is FR-4 copper-clad laminate, and the raw material of the substrate includes the middle layer of the substrate covered with a copper layer on the upper surface and the lower surface; according to the design requirements of the substrate, mechanical drilling is used to drill holes on the substrate A plurality of holes through the raw material of the substrate are formed on the raw material; a cylindrical side wall of copper with uniform thickness is electroplated on the surface of the hole, and the two ends of the side wall are respectively connected with the copper on the upper surface and the lower surface of the middle layer of the substrate. The layers are connected; a layer of dry film is respectively laid on the copper layer on the upper and lower surfaces of the original substrate, and the dry film on the two layers of copper except for the graphic part is removed by exposur...

Embodiment 2

[0087] The substrate is obtained by the method of Example 1, and the passivation layer, the passivation layer opening, the sputtering Ti layer and the Cu layer are coated on the substrate according to the method of Example 1, and the photoresist is coated to form a thickness of 35.5 mm. μm photoresist layer, baked at 85°C for 18 seconds to make the photoresist and Ti / Cu layer tightly bonded; .

Embodiment 3

[0089] The substrate is obtained according to the method of Example 1, and the passivation layer, the opening of the passivation layer, the sputtering Ti layer and the Cu layer are coated on the substrate according to the method of Example 1, and the photoresist is coated to form a thickness of 34.5 μm photoresist layer, baked at 75°C for 12 seconds to make the photoresist and Ti / Cu layer tightly bonded; .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com