Wafer alignment method

A wafer and alignment mark technology, applied in the field of integrated circuit manufacturing, can solve problems such as high cost and inability to use a lithography machine, and achieve the effects of low cost, effective alignment, and reduced difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the accompanying drawings, the present invention is described in detail as follows:

[0027] The alignment method between the wafer and the wafer of the present embodiment, its specific implementation process flow is as follows:

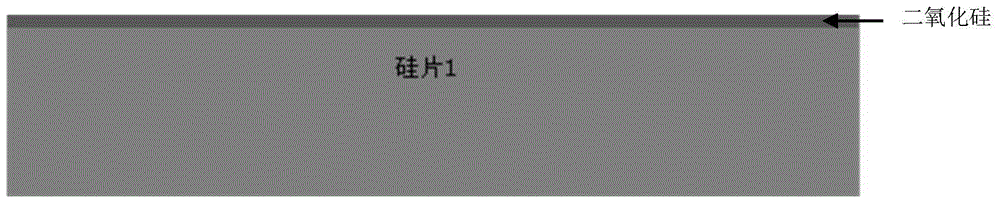

[0028] Step 1, form a thin layer of silicon dioxide on silicon wafer 1 with physical vapor deposition method, such as figure 1 shown.

[0029] The silicon wafer 1 has a diameter of 200 mm and a thickness of 725 microns. The silicon dioxide layer has a thickness of 100 angstroms.

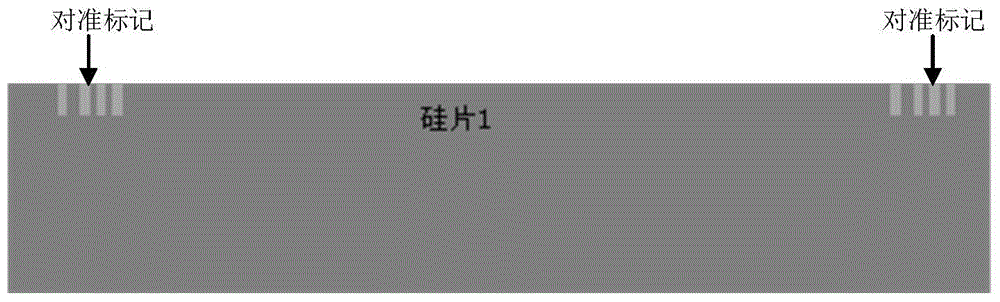

[0030] Step 2, forming 9 groups of alignment marks with a grating period of 12 microns and a depth of 0.5 to 100 microns on the silicon wafer 1, and then removing the silicon dioxide layer, such as figure 2 shown.

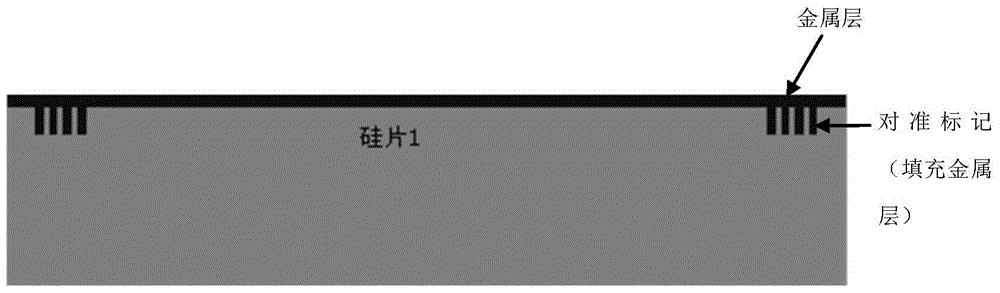

[0031] Step 3, deposit a layer of metal on the silicon wafer 1, so that a layer of metal layer is ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com