Fabrication method of wafer-level uniaxial strained SiGe on SiN buried insulating layer based on silicon nitride stress film and scale effect

A scale effect and technology on the insulating layer, applied in the field of microelectronics, can solve problems such as poor process compatibility, small strain, and poor reliability, and achieve the effects of low cost, large strain, and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

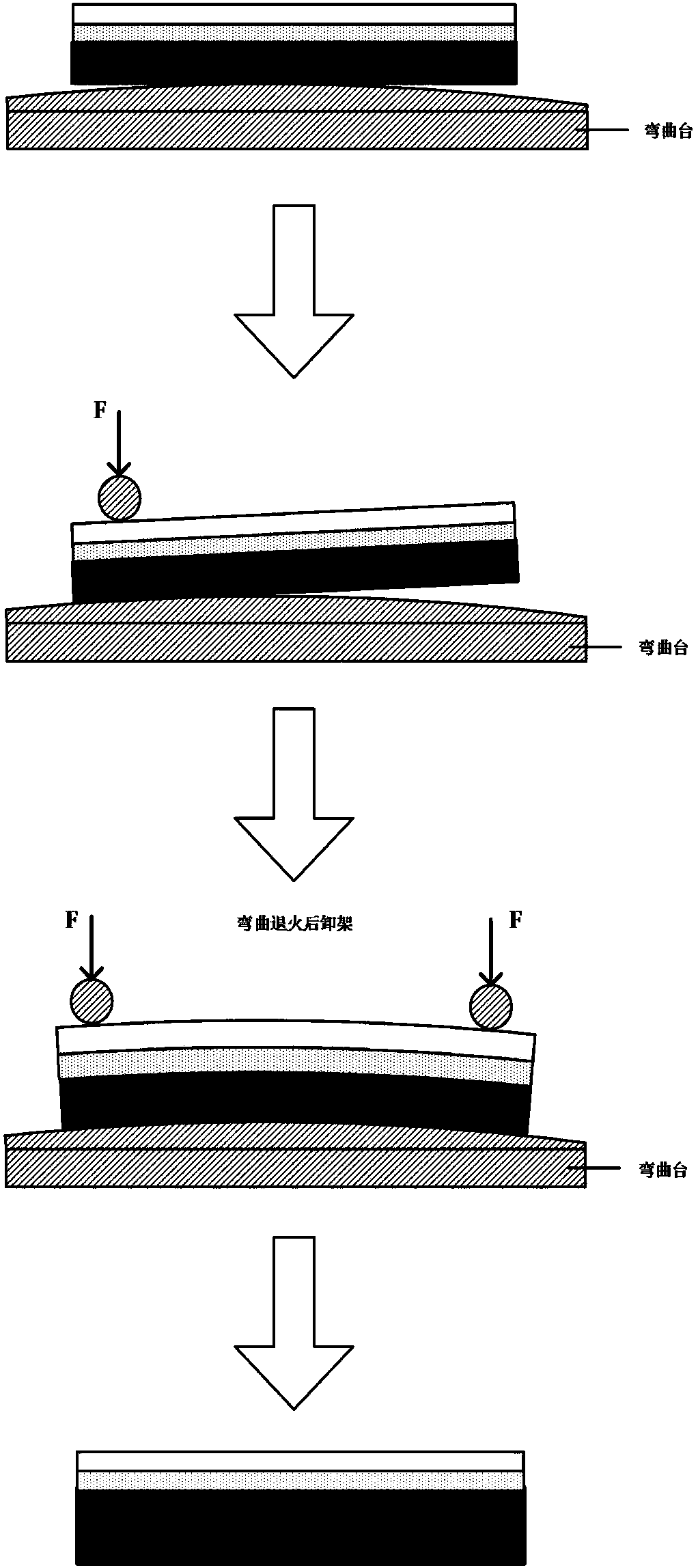

Method used

Image

Examples

Embodiment 1

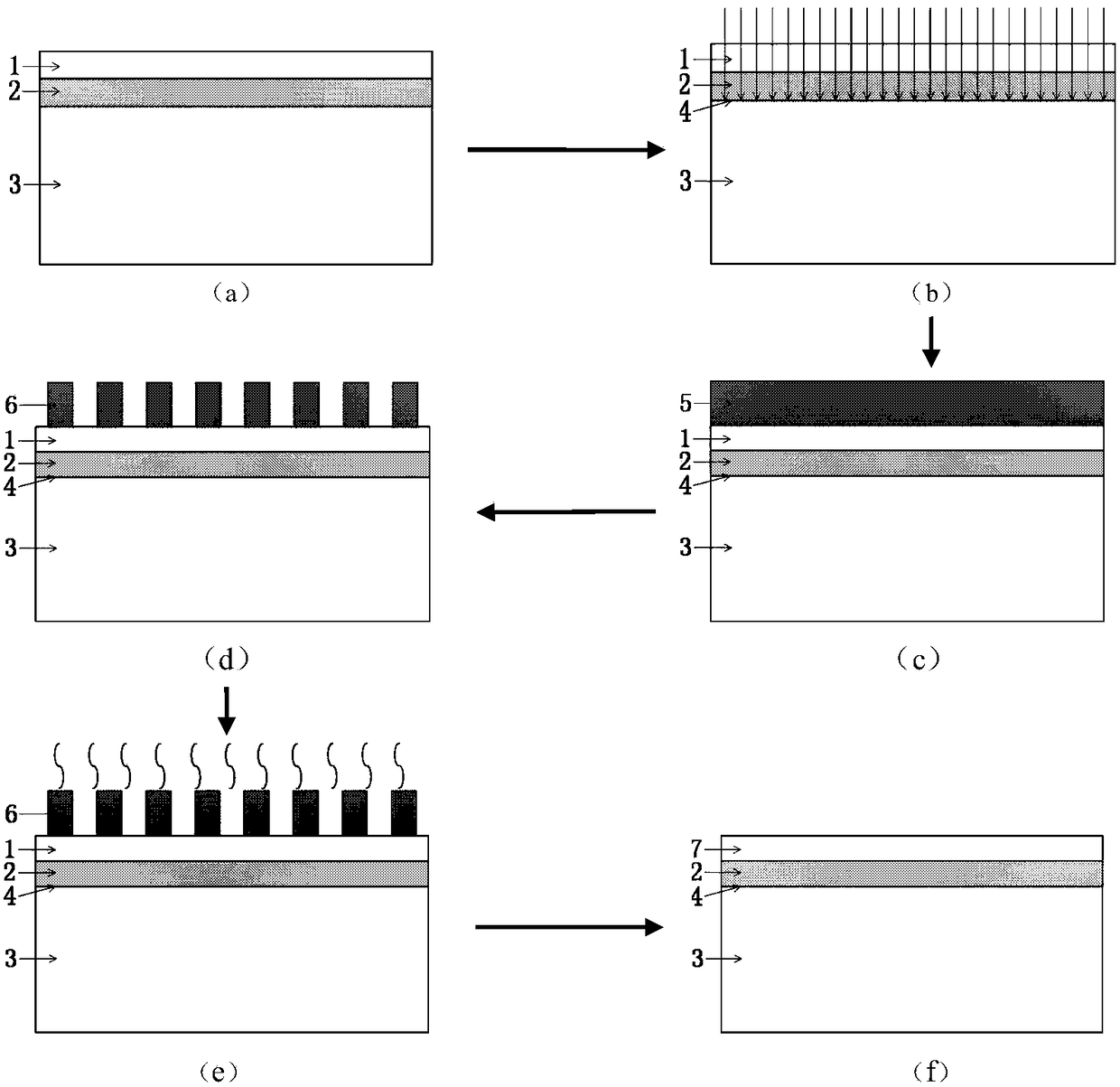

[0036] Example 1, preparing a 5-inch SiN buried insulating layer uniaxially strained SGOI wafer material.

[0037] Step 1: Clean the SiN buried insulating layer SGOI wafer to remove surface contaminants.

[0038] (1.1) Use acetone and isopropanol to alternately perform ultrasonic cleaning on the SGOI wafer to remove organic contamination on the substrate surface;

[0039] (1.2) Prepare a 1:1:3 mixed solution of ammonia, hydrogen peroxide, and deionized water, and heat it to 120°C, soak the SGOI wafer in the mixed solution for 12 minutes, take it out and rinse it with a large amount of deionized water, To remove inorganic pollutants on the surface of SGOI wafers;

[0040] (1.3) Soak the SGOI wafer in HF acid buffer for 2 minutes to remove the oxide layer on the surface.

[0041] Step 2: Ion implantation.

[0042] The implantation dose to the cleaned SGOI wafer is 1E14cm -2 , He ions with an energy of 50Kev to loosen the interface 4 between the Si substrate 3 and the SiN bur...

Embodiment 2

[0056] Example 2, preparing an 8-inch SiN buried insulating layer uniaxially compressively strained SGOI wafer material.

[0057] Step 1: cleaning the SiN buried insulating layer SGOI wafer to remove surface pollutants.

[0058] The implementation of this step is the same as step 1 of Embodiment 1.

[0059] Step 2: Implant the cleaned SGOI wafer with a dose of 1E15cm -2 , He ions with an energy of 85Kev to loosen the interface 4 between the Si substrate 3 and the SiN buried insulating layer 2, such as figure 2 as shown in b.

[0060] Step 3: Deposit a tensile stress SiN film 5 with a thickness of 0.7 μm and a stress of 1.2 GPa on the surface of the top SiGe layer 1 of the ion-implanted SGOI wafer, such as figure 2 as shown in c.

[0061] The realization process of this step is identical with the step 3 of embodiment 1, and its process parameter is as follows:

[0062] The reaction chamber temperature is 400°C, the reaction chamber pressure is 3.1Torr, the high frequency...

Embodiment 3

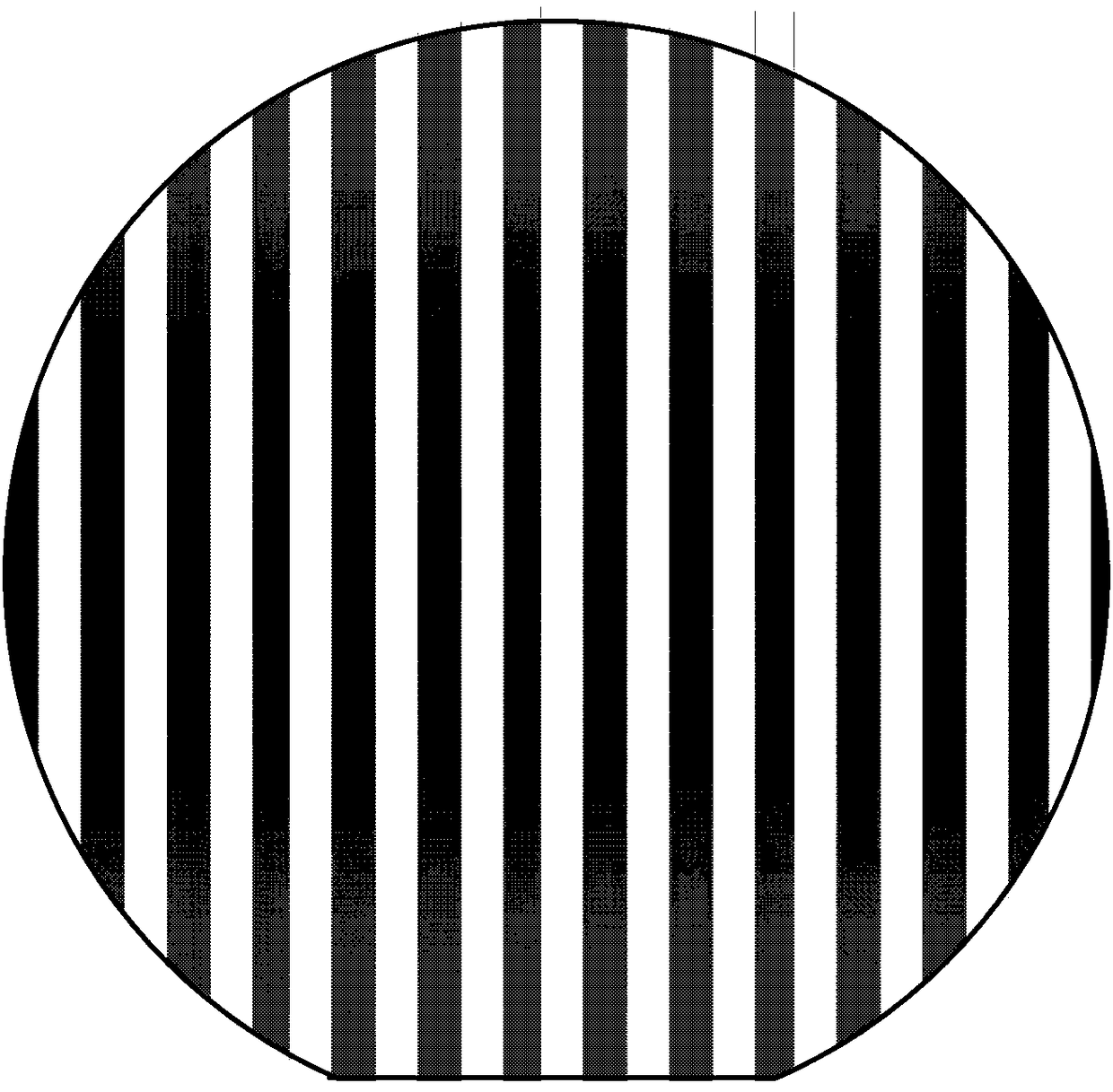

[0070] Example 3, preparing a 12-inch SiN buried insulating layer uniaxially strained SGOI wafer material.

[0071] Step A: cleaning the SiN buried insulating layer SGOI wafer to remove surface pollutants.

[0072] The implementation of this step is the same as step 1 of Embodiment 1.

[0073] Step B: Perform ion implantation on the cleaned SGOI wafer to loosen the interface 4 between the Si substrate 3 and the SiN buried insulating layer 2, such as figure 2 as shown in b.

[0074] The ion implantation process is: the implanted ions are He ions, and the implantation dose is 1E16cm -2 , inject energy 120Kev.

[0075] Step C: Depositing a SiN film.

[0076] On the surface of the top SiGe layer 1 of the ion-implanted SGOI wafer, a compressive stress SiN film 5 with a thickness of 0.9 μm and a stress of -1.3 GPa is deposited, such as figure 2 as shown in c;

[0077] The realization process of this step is identical with the step 3 of embodiment 1, and its process parameter...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More