GaAs-based PMOS device manufacturing method

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of slow progress of PMOS devices, achieve mobility and high electron concentration, low interface state density, and improve the Dimensional electron gas concentration effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

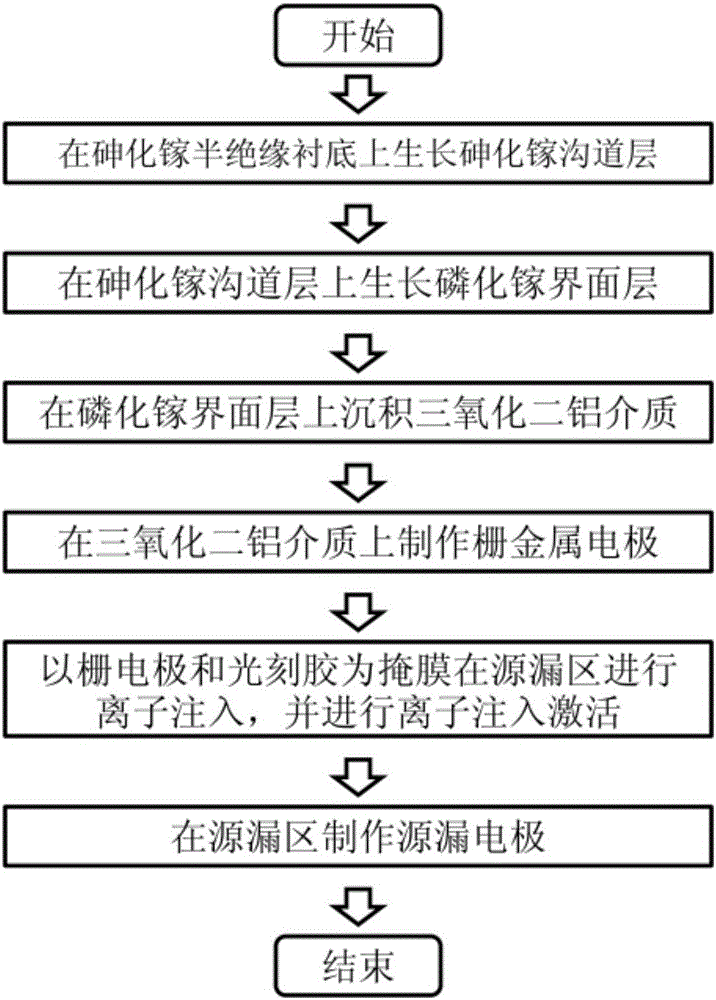

[0026] Such as Figure 2-7 as shown, Figure 2-7 This embodiment provides a method for manufacturing a gallium arsenide PMOS device.

[0027] Its production steps are as follows:

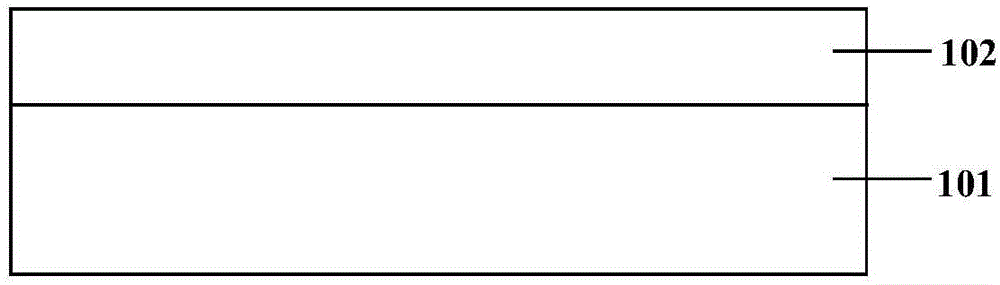

[0028] (1) if figure 2 As shown, the N-type doped gallium arsenide channel layer (102) with a doping concentration of 5×10 is grown on a semi-insulating gallium arsenide substrate (101) with a thickness of 100 nanometers. 17 cm -3 , the doping impurity is silicon;

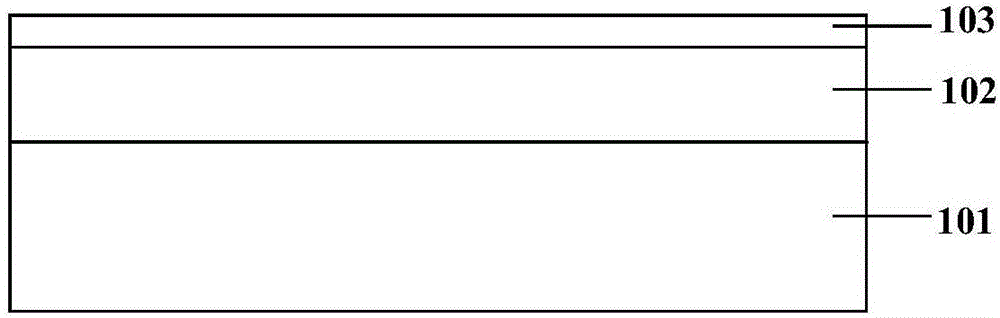

[0029] (2) if image 3 As shown, a gallium phosphide interface layer (103) with a thickness of 1 nanometer is grown on the gallium arsenide channel layer (102);

[0030] (3) if Figure 4 As shown, a 3-nanometer-thick aluminum oxide medium (104) is grown on the surface of th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More