Trench gate charge storage type IGBT (Insulated Gate Bipolar Translator) and manufacturing method thereof

A charge storage and charge storage layer technology, applied in circuits, electrical components, semiconductor/solid-state device manufacturing, etc., can solve problems such as increasing charge/discharge time, increasing device saturation current density, and affecting device switching loss compromise characteristics.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

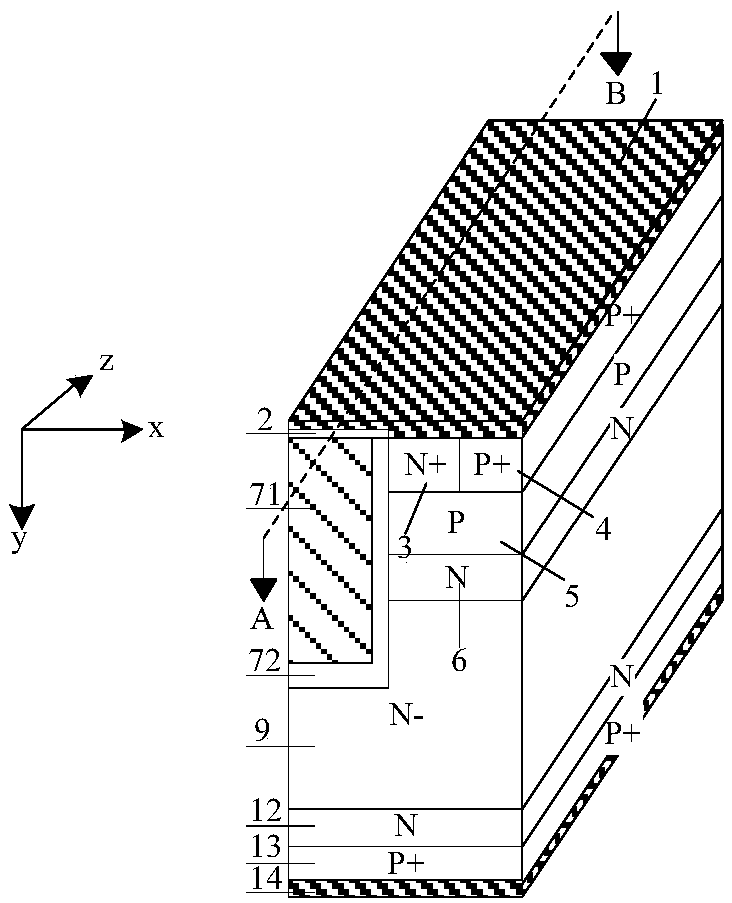

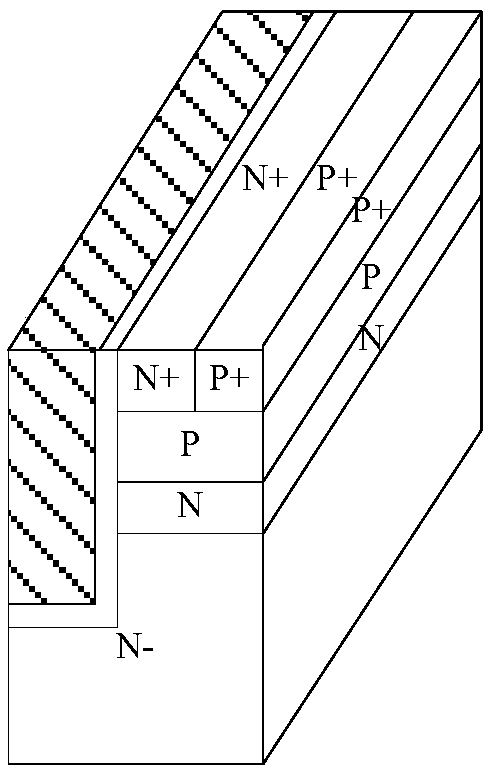

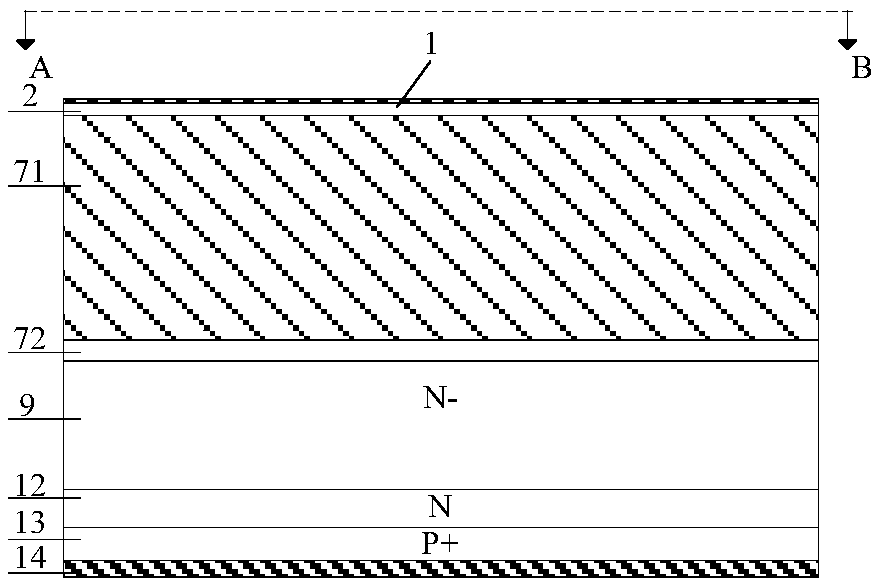

[0099] A trench gate charge storage type IGBT, one-half of the cell such as Figure 4 As shown, its section along AB line and CD line is as follows Image 6 and Figure 7 As shown, a three-dimensional coordinate system is established with any inflection point of one-half cell as the origin, and the bottom surface of one-quarter cell intersects with the two sides of the inflection point as the x-axis and z-axis respectively, passing through the inflection point and A straight line perpendicular to the bottom surface is used as the y-axis, and the directions of the x, y, and z-axes refer to Figure 4 ;

[0100] The half cell includes a collector metal 14, a P-type collector region 13, an N-type drift region 9, and an emitter metal 1 stacked sequentially from bottom to top; the top layer of the N-type drift region 9 has N-type charge storage layer 6, P-type base region 5, P+ body contact region 4 and N+ emitter region 3; the P-type base region 5 is located on the top layer of ...

Embodiment 2

[0103] A trench gate charge storage type IGBT, one-half of the cell such as Figure 8 As shown, its section along AB line, CD line, EF line and GH line is as follows Figures 10 to 13 As shown, the establishment method of the coordinate system is the same as that in Embodiment 1, see for details Figure 8 ;

[0104] The difference between this embodiment and Embodiment 1 is that the extension depth of the gate electrode 71 in the top layer of the N-type drift region 9 in this embodiment is equal to the extension depth of the split electrode 81, but the extension width of the gate electrode 71 at both ends of the top layer of the device is less than The extended width of the split electrode 81, while retaining part of the split electrode dielectric layer 82 and part of the split electrode 81 structure on the top layer of the device; the thickness of the split electrode dielectric layer 82 is greater than the thickness of the gate dielectric layer 72.

[0105] In this embodime...

Embodiment 3

[0107] A trench gate charge storage type IGBT, one-half of the cell such as Figure 14 As shown, its section along AB line, CD line, EF line and GH line is as follows Figures 16 to 19 As shown, the establishment method of the coordinate system is the same as that in Embodiment 1, see for details Figure 14 ;

[0108] The difference between this embodiment and Embodiment 2 is that: this embodiment does not have a split electrode 81 and a split electrode dielectric layer 82 structure on the top layer of the device, the split electrode 81 and the split electrode dielectric layer 82 are located at the bottom of the gate electrode 71, and the N+ emitter region 3 It is equal to the depth of the P+ body contact region 4 along the z-axis direction and less than the depth of the P-type base region 5 along the z-axis direction. The thickness of the gate electrode 71 connected to the region 3

[0109] In this embodiment, by changing the width of the gate electrode 71, under the same ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More