3D integrated circuit through silicon via fault detection system and detection method

An integrated circuit and fault detection technology, which is applied in the direction of electronic circuit testing, measuring electronics, measuring devices, etc., can solve the problems of low test accuracy, high-density TSV array testing difficulty, and occupying a large area, etc., to achieve a simple circuit structure Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

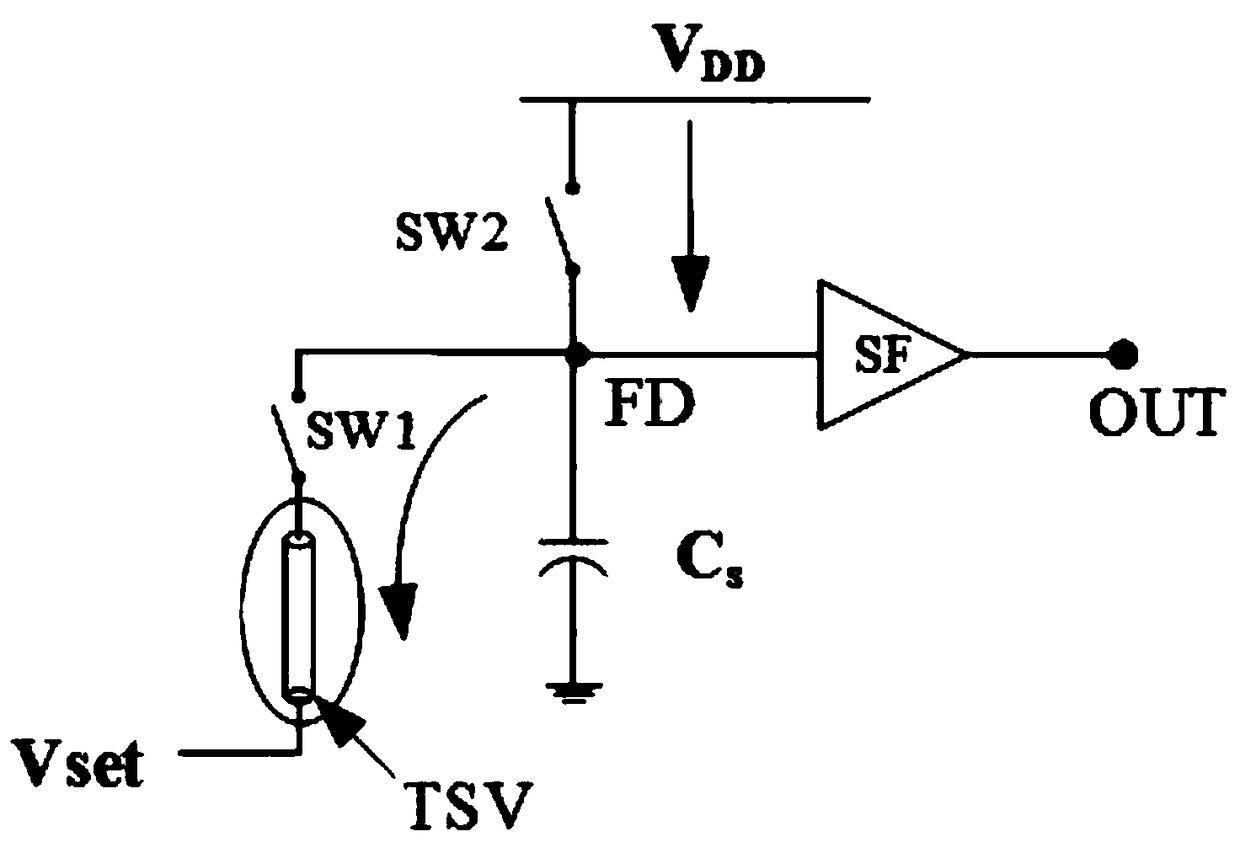

[0036] The invention provides a 3D integrated circuit through-silicon via fault detection system, such as figure 1 shown, the first switch SW1 and capacitor C S , the first switch SW1 connects the capacitor C S The upper plate FD, capacitance C S The upper plate FD of is connected with the second switch SW2 and the source follower SF, the capacitor C S The lower plate is grounded.

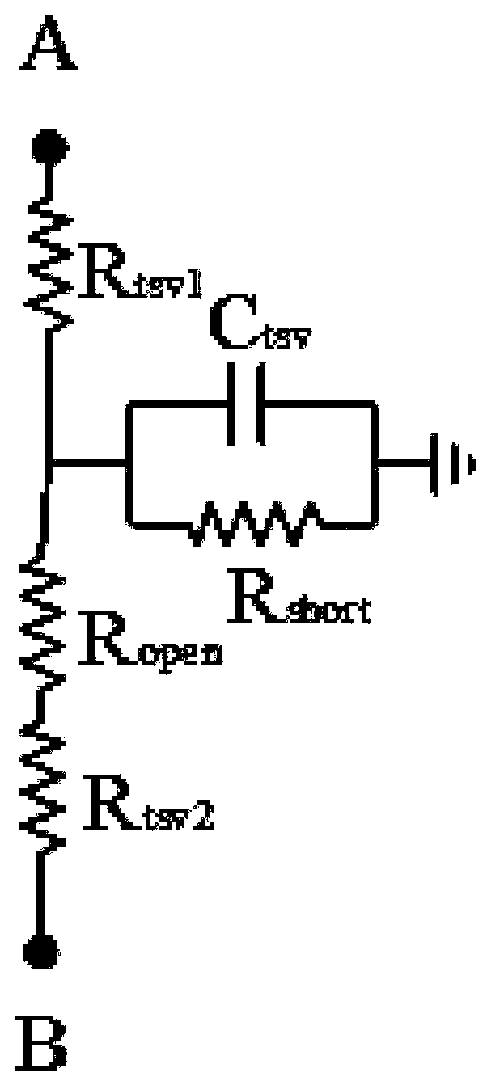

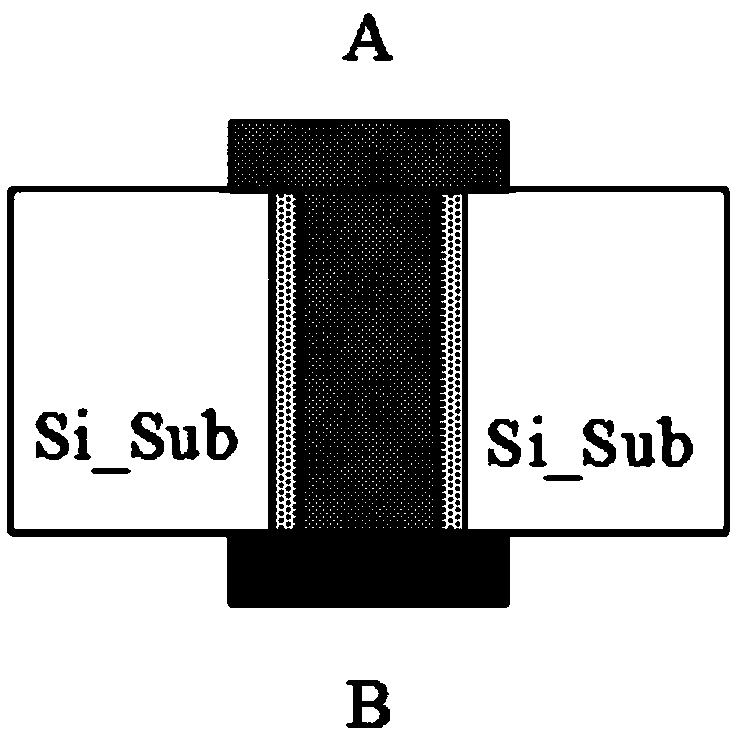

[0037] Such as figure 2 As shown, the TSV includes a metal conductive cylinder whose outer wall is coated with an insulating layer. The defect of TSV is caused by the instability that may exist in the process during processing. The normal TSV silicon chip is insulated from the substrate through the insulating layer of the side wall, and the A and B ends of the metal conductive cylinder have good conductivity and low resistance. If there is a breakdown or defect in the insulating layer of the TSV, the metal conductive cylinder of the TSV passes through the insulating layer. This defect is usu...

Embodiment 2

[0047] TSV fault response electric signal readout array implementation scheme, as follows:

[0048] The value of the capacitor Cs in the readout circuit has a great influence on the discharge time, and the larger the value of the capacitor Cs, the wider range of TSV resistance characteristics the readout circuit can distinguish. When the value of the capacitor Cs is large enough, the resistance characteristics of the TSV without failure can be evaluated; however, since the on-chip capacitor Cs occupies a large area, it is difficult to integrate a large capacitor in a limited area.

[0049] In order to solve the detection of multiple TSVs, reduce the large area occupied by the on-chip capacitor, integrate a large capacitor in a limited area, and share the capacitor Cs, such as Figure 4 As shown in , an example of a circuit is given; for a high-density TSV array (assuming there are i TSVs), one end of each TSV passes through its corresponding MOS switch (by Rst_n Control) conn...

Embodiment 3

[0051] Implementation scheme of readout electrical signal array device and TSV position matching

[0052] Due to the small scale and spacing of TSV, the electrical signal of the high-density TSV through-hole is read by the electrode lattice, specifically: the response electrical signal readout circuit array is designed using the same process as the TSV to be tested, and at the same time as the TSV is prepared, Complete readout array preparation. An electrode lattice is designed on the top layer of the readout circuit array, and the lattice adopts the same layout as the high-density TSV array. During the test, real-time online TSV fault test and diagnosis can be realized by using the existing alignment technology on the existing production line. The electrode plate applies an electrical signal to the TSV, and uses the TSV response electrical signal readout circuit based on charge charging and discharging to read the response signal from the lower electrode of the TSV, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More