Integrated low-capacitance ESD protection device and preparation method thereof

An ESD protection, low-capacitance technology, applied in the fields of electrical solid-state devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of reduced ESD leakage capability, increased chip area, and low discharge current value, to ensure ESD leakage capability, uniform current distribution, and small transient on-state voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

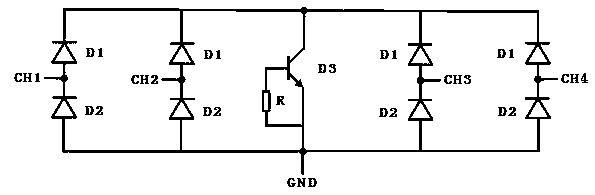

[0036] Such as figure 1 It is an equivalent circuit diagram of the present invention, an integrated low-capacitance ESD protection device, which is a four-channel low-capacitance unidirectional integrated ESD protection device, and the direction of ESD leakage is: CH1 to GND, and the channel flows through the low-capacitance diode D1 and the low-voltage The diode D3 is connected to the ground, and the low-voltage diode D3 is the main part of the ESD discharge. D3 is a triode structure in which EB is short-circuited. The IV characteristic between C and E is used to realize the discharge of the ESD current. The residual voltage of the structure is lower than that of the conventional diode structure using reverse avalanche breakdown voltage leakage, and there is no latch-up effect of the thyristor structure. From GND to CH1, the current flows through the low-capacity diode D2 to CH1, and the low-capacity diode D2 is forward-conducting. Since the capacitance of the diode D3 is mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More