LDMOS device and process method

A process method and device technology, applied in the field of NLDMOS devices, can solve problems such as unsatisfactory breakdown voltage of LDMOS devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

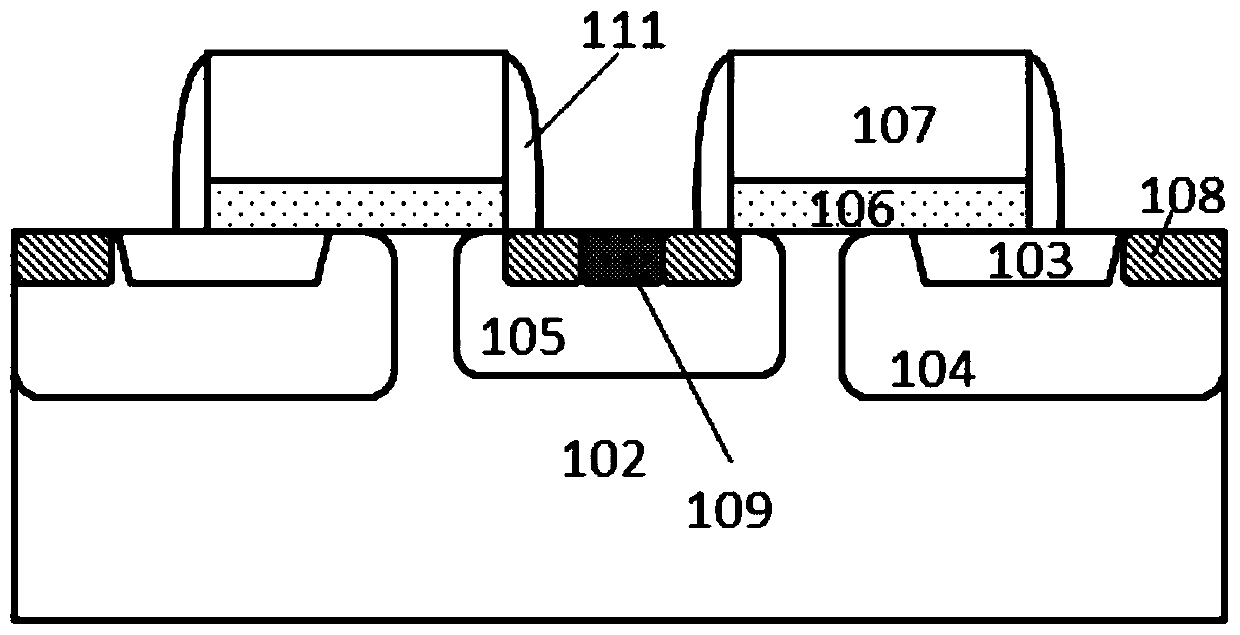

[0060] An LDMOS device according to the present invention, such as image 3 As shown, the P-type substrate 102 (or P-type epitaxy) has a P-type body region 105 and an N-type drift region 104 .

[0061] There is also a polysilicon gate structure on the surface of the P-type substrate, and the polysilicon gate structure includes a gate dielectric layer 106, a polysilicon gate 107, a metal silicide 110 above the polysilicon gate, and gate spacers 111, so The gate dielectric layer is located on the surface of the substrate to isolate the polysilicon gate from the substrate, and the spacers are located on both sides of the polysilicon gate.

[0062] The polysilicon gate structure is located on the surface of the substrate between the P-type body region and the N-type drift region, and overlaps with the body region 105 and the drift region 106 located on both sides thereof, that is, image 3 The middle polysilicon gate structure covers the body region 105 to the left and the isolat...

Embodiment 2

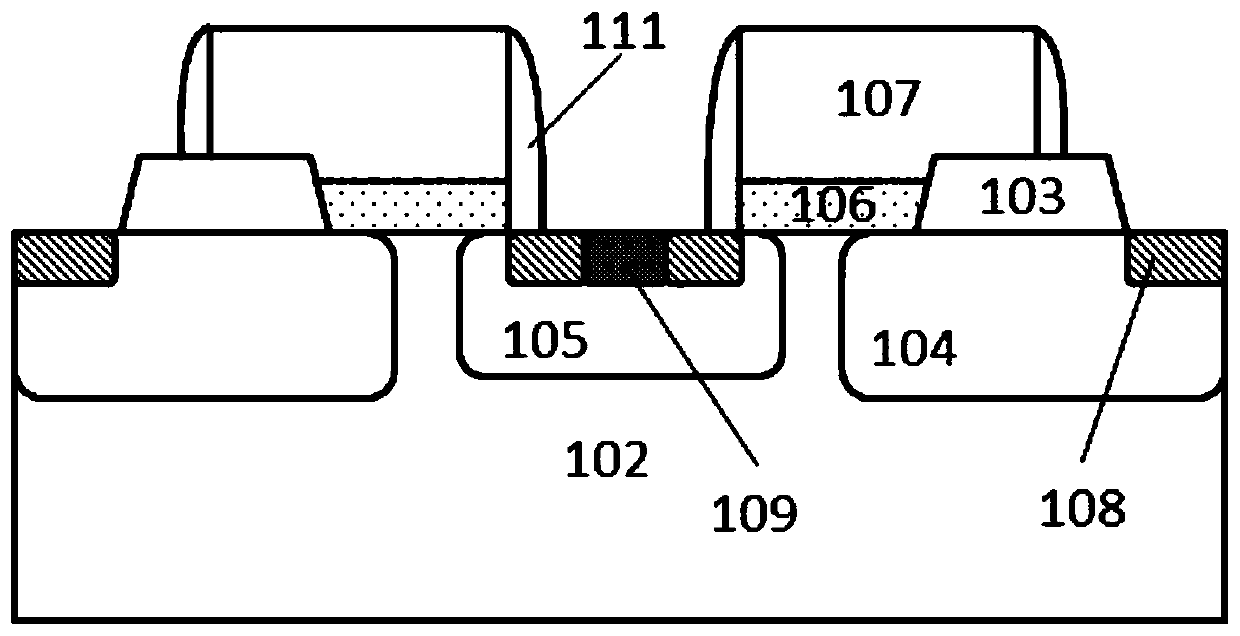

[0078] Another LDMOS device provided by the present invention, such as Figure 7 As shown, its main structure is roughly the same as that of the first embodiment, and will not be repeated. The difference from the first embodiment is that the isolation silicon oxide layer 103 is located on the surface of the substrate, and the structure of the first embodiment is An isolation silicon oxide layer 103 is embedded in the substrate.

[0079] One side of the isolation silicon oxide layer 103 extends below the polysilicon gate structure and is connected to the gate dielectric layer, that is, embedded in the polysilicon gate, and the other side is connected to the N-type dopant in the N-type drift region. The nearest side of the miscellaneous region 108 is aligned.

[0080] The isolation silicon oxide layer 103 also has a metal silicidation reaction blocking silicon oxide layer 101 .

[0081] The thickness of the isolation silicon oxide layer 103 is defined as the thickness of the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com