A kind of manufacturing method of split gate mosfet

A fabrication method and separation gate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor insulation, poor source and gate insulation, large overlapping area, etc., and achieve the reduction of precision requirements. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

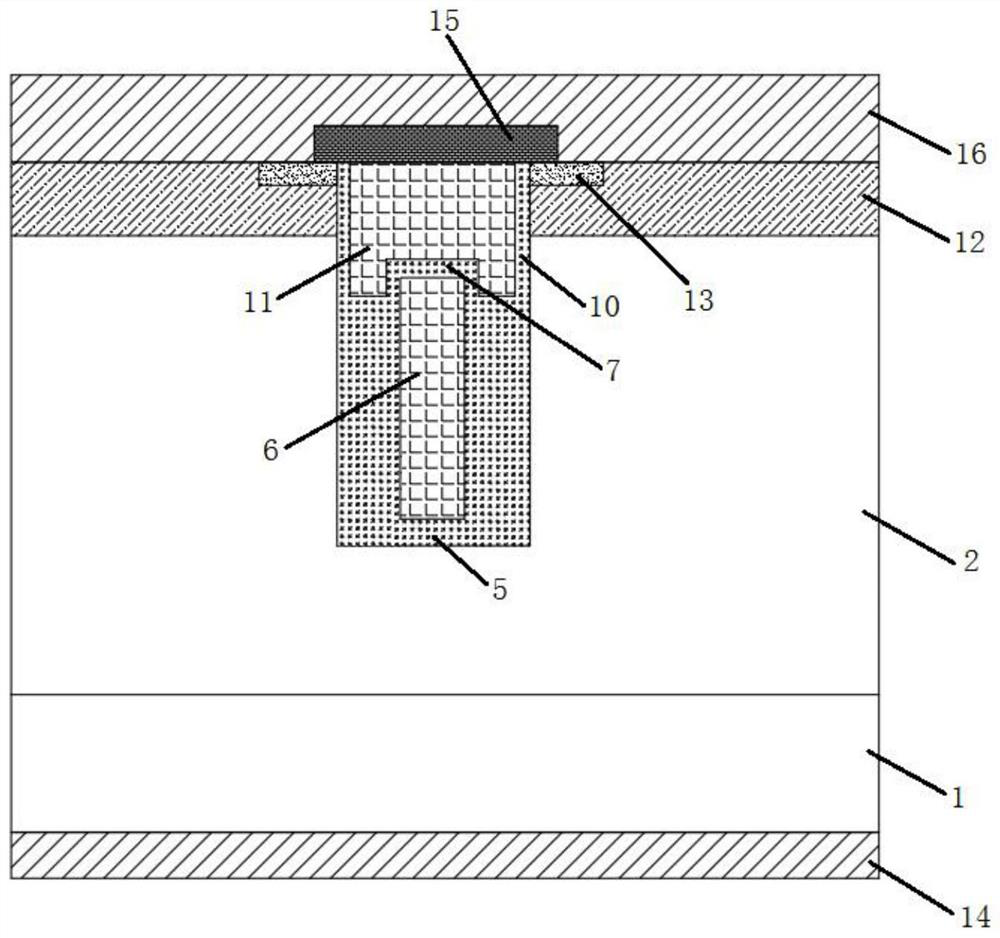

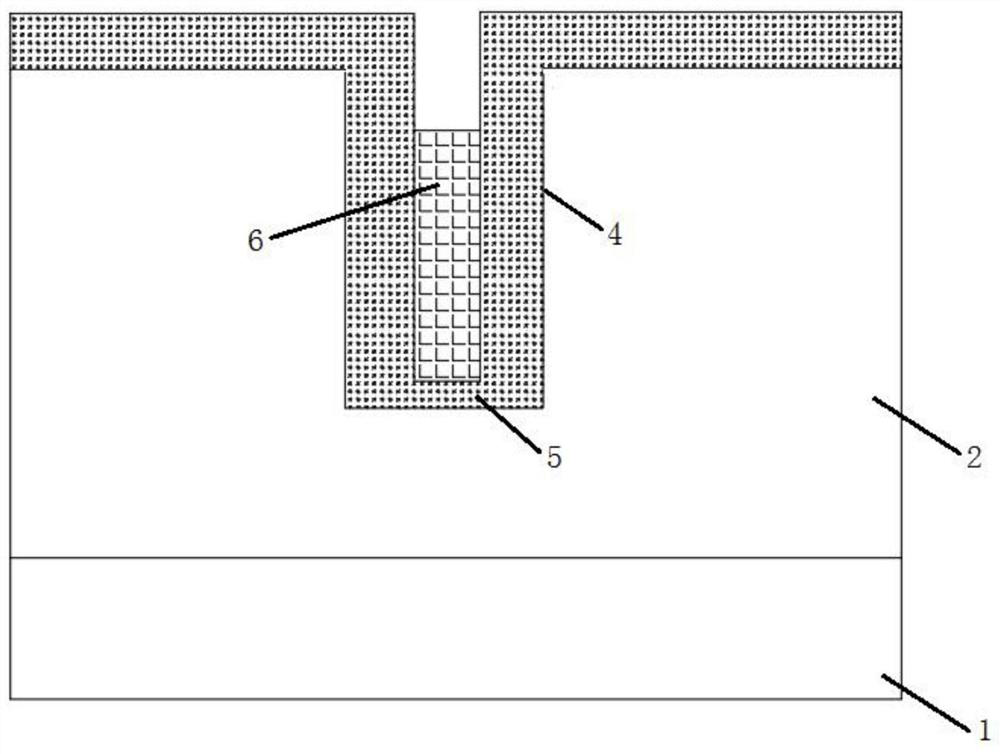

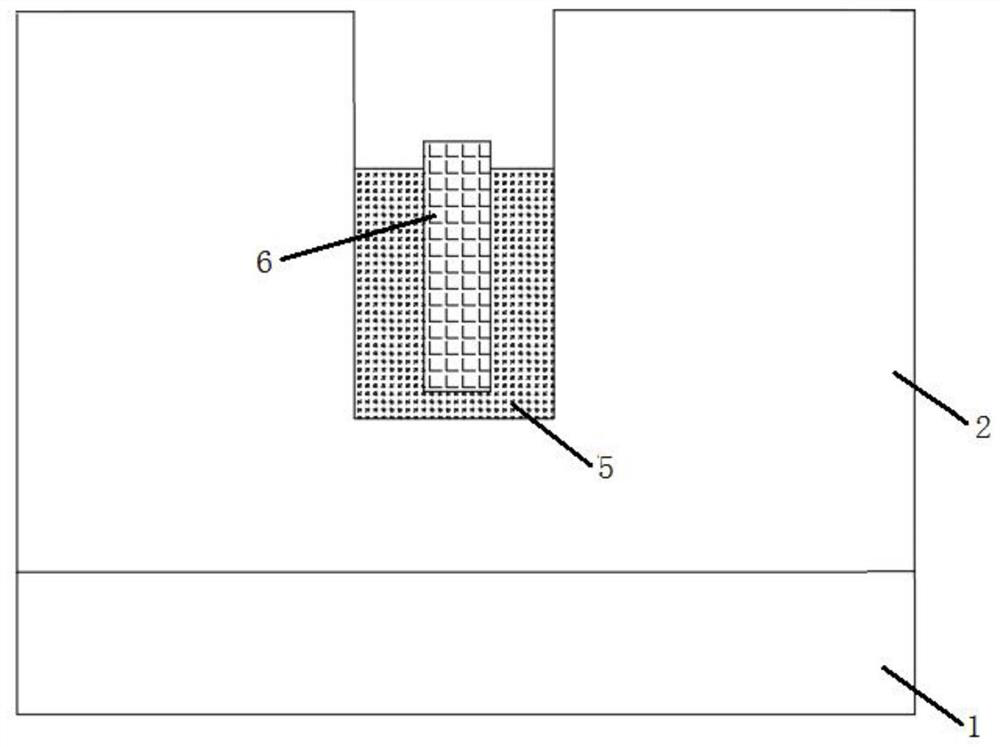

[0050] like Figures 3A to 3L As shown, it is a schematic diagram of the device structure of each step of the method according to the first embodiment of the present invention. Taking an N-type device as an example, the manufacturing method of a split-gate MOSFET according to the embodiment of the present invention includes the following steps:

[0051] Step one, as Figure 3A As shown, a lightly doped N-type epitaxial layer 2 is formed on a heavily doped N-type substrate 1, the upper surface of the N-type epitaxial layer 2 is the first main surface 001, and the N-type substrate The lower surface of 1 is the second main surface 002 .

[0052] Step two, as Figure 3B As shown, a first oxide layer 3 is deposited on the first main surface 001; the thickness of the first oxide layer 3 can be adjusted as required, and preferably, the first oxide layer 3 is silicon oxide.

[0053] Step three, as Figure 3C As shown, the first oxide layer 3 and the epitaxial layer 2 are etched to...

no. 2 example

[0069] The difference between this embodiment and the first embodiment is that, as Figure 5 As shown, in this embodiment, the seventh step is to grow an oxide layer in the trench 4 by thermal oxidation, and form an inter-polysilicon isolation oxide layer 7 on the separation gate polysilicon 6 . Since the second oxide layer 5 is formed on the sidewall of the trench 4, oxygen cannot easily penetrate the second oxide layer 5 to react with the silicon in the N-type epitaxial layer 2 during thermal oxidation. Therefore, the polysilicon formed above the separation gate polysilicon 6 The thickness D1 of the isolation oxide layer 7 will be significantly greater than the increased thickness D3 of the second oxide layer 5 located on the sidewall of the trench 4 and the increased thickness D2 of the second oxide layer 5 located on the first main surface 001, and the thickness ratio can be It can reach 5:1 or more; in this step, an IPO that meets the process requirements can be formed at...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More