Silicon-based laminated solar cell with microstructure and preparation method thereof

A technology of solar cells and microstructures, which is applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of low long-wavelength photon absorption efficiency and low carrier collection efficiency, so as to improve photoelectric conversion efficiency, improve charge transmission performance, and improve The effect of utilization efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

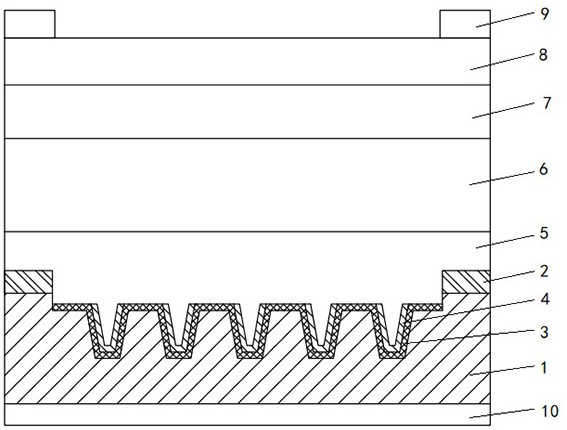

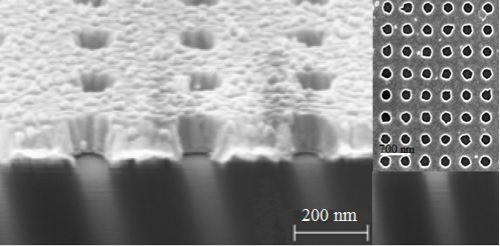

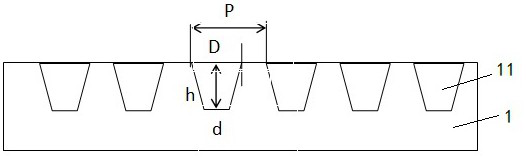

[0033] Example 1, see figure 1 , figure 2 and image 3 As shown, first, the n-type single crystal silicon substrate 1 is an n-type Czochralski single crystal silicon wafer with a size of 1 cm×1 cm, a thickness of 100 μm, and a resistivity of 1.6 Ω·cm. After cleaning, the submicron dry etching process masked by the nanoparticle self-assembled film was used to prepare an inverted nano-frustum hole 11-period array structure, using SF6 and C4F8 mixed gas, the volume flow rate was 16sccm and 18sccm, the power was 600W, and the partial The voltage is 20V, and the dry etching time is 0.3h. After forming an 11-period array of inverted nano-truncated cone holes on the surface of the silicon substrate, it was cleaned with deionized water. The period P of the formed periodic array structure of nano-frustum holes 11 is 400nm, the diameter d of the small end of the nano-frustum holes 11 is 100nm, the diameter D of the big end is 300nm, the hole depth h is 500nm, and the duty ratio is 0.7...

Embodiment 2

[0037] Example 2, please refer to Example 1. First, the n-type single crystal silicon substrate 1 is an n-type Czochralski single crystal silicon wafer with a size of 1 cm×1 cm, a thickness of 100 μm, and a resistivity of 1.6 Ω·cm. After cleaning, the submicron dry etching process masked by the nanoparticle self-assembled film was used to prepare an inverted nano-frustum hole 11-period array structure, using SF6 and C4F8 mixed gas, the volume flow rate was 16sccm and 18sccm, the power was 700W, and the partial The voltage is 30V, and the dry etching time is 0.5h. After forming an 11-period array of inverted nano-truncated cone holes on the surface of the silicon substrate, it was cleaned with deionized water. The period P of the formed periodic array structure of nano-truncated cone holes 11 is 400nm, the diameter d of the small end of the nano-truncated cone holes 11 is 100nm, the diameter D of the large end is 300nm, the hole depth h is 800nm, and the duty ratio is 0.75.

...

Embodiment 3

[0041] Example 3, please refer to Example 1. First, the n-type single crystal silicon substrate 1 is an n-type Czochralski single crystal silicon wafer with a size of 1 cm×1 cm, a thickness of 100 μm, and a resistivity of 1.6 Ω·cm. After cleaning, the submicron dry etching process masked by the nanoparticle self-assembled film was used to prepare the inverted nano-truncated cone hole 11-period array structure, using SF6 and C4F8 mixed gas, the volume flow rate was 12sccm and 22sccm, the power was 600W, and the partial The voltage is 20V, and the dry etching time is 0.3h. After forming an 11-period array of inverted nano-truncated cone holes on the surface of the silicon substrate, it was cleaned with deionized water. The period P of the formed periodic array structure of nano-frustum holes 11 is 600nm, the diameter d of the small end of the nano-frustum holes 11 is 100nm, the diameter D of the big end is 400nm, the hole depth h is 500nm, and the duty cycle is 0.66.

[0042] A...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More