Method for manufacturing semiconductor device

A semiconductor and device technology, which is applied in the field of producing miniaturized complementary semiconductor devices, can solve problems such as difficult control, increase in junction capacitance, and accelerated diffusion, and achieve the effects of suppressing increase in junction capacitance, high driving force, and suppression of short-channel effects Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0083] Figures 7A to 7I is a cross-sectional view showing each process step in the method for producing a semiconductor device according to the first embodiment of the present invention.

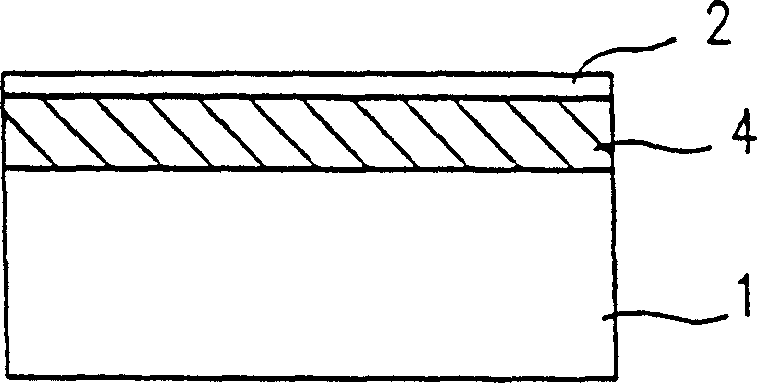

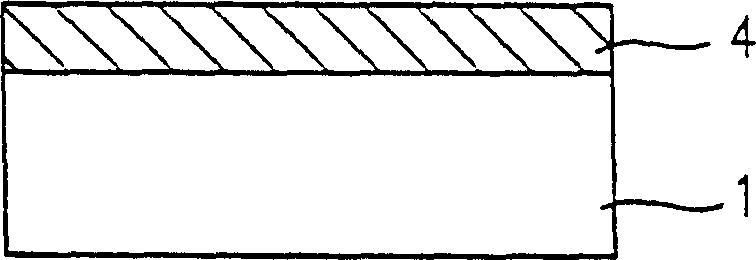

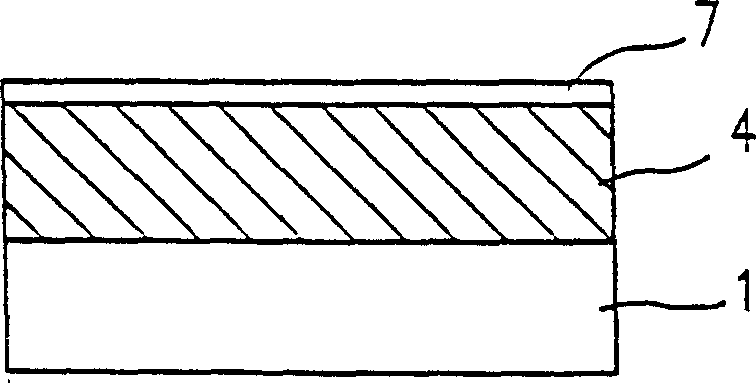

[0084] first as Figure 7A As shown, a p-type low-concentration substrate 1 is thermally oxidized to form a protective oxide film 2 for ion implantation. In the figure, reference numeral 50 denotes an insulating isolation region for device isolation.

[0085] Next as Figure 7B As shown, a mask 51 is selectively formed on the protective oxide film 2, and using the mask 51, an accelerating voltage of 400keV and 4.4×10 12 cm -2 A dose of boron is implanted, thereby forming a retrograde p-type well 3 . Also using the same mask 51, with an accelerating voltage of 160keV and 6.0×10 12 cm -2 The dose implanted boron for the formation of the channel stop layer, and with the accelerating voltage of 30keV and 4.7×10 12 cm -2 A dose of boron is implanted for forming the impurity diffusion la...

Embodiment 2

[0092] Figures 8A to 8I is a cross-sectional view showing each process step in the method for producing a semiconductor device according to the second embodiment of the present invention.

[0093] first as Figure 8A As shown, a p-type low-concentration substrate 1 is thermally oxidized to form a protective oxide film 2 for ion implantation. In the figure, reference numeral 50 denotes an insulating isolation region for device isolation.

[0094] Next as Figure 8B As shown, a mask 61 is selectively formed on the protective oxide film 2, and using the mask 61, an accelerating voltage of 400keV and 1.0×10 13 cm -2 Phosphorus is implanted at a dose of , thereby forming a retrograde n-type well 5 . Also using the same mask 61, with an accelerating voltage of 160keV and a 6.0×10 12 cm -2 The dose implanted phosphorus for forming punch-through stop layer, and with the accelerating voltage of 70keV and 6.6×10 12 cm -2 The dose implantation is used to form the BF of the impu...

Embodiment 3

[0102] Figures 9A to 9I is a sectional view showing each process step in the method for producing a semiconductor device according to the third embodiment of the present invention.

[0103] first as Figure 9A As shown, a p-type low-concentration substrate 1 is thermally oxidized to form a protective oxide film 2 for ion implantation. In the figure, reference numeral 50 denotes an insulating isolation region for device isolation.

[0104] Next as Figure 9B As shown, a mask 61 is selectively formed on the protective oxide film 2, and using the mask 61, an accelerating voltage of 400keV and 1.0×10 13 cm -2 Phosphorus is implanted at a dose of , thereby forming a retrograde n-type well 5 . Also using the same mask 61, with an accelerating voltage of 160keV and a 6.0×10 12 cm -2 The dose implanted phosphorus for forming punch-through stop layer, and with the accelerating voltage of 70keV and 6.6×10 12 cm -2 The dose implantation is used to form the BF of the impurity di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More