Double-groove silicon carbide MOSFET structure and manufacturing method

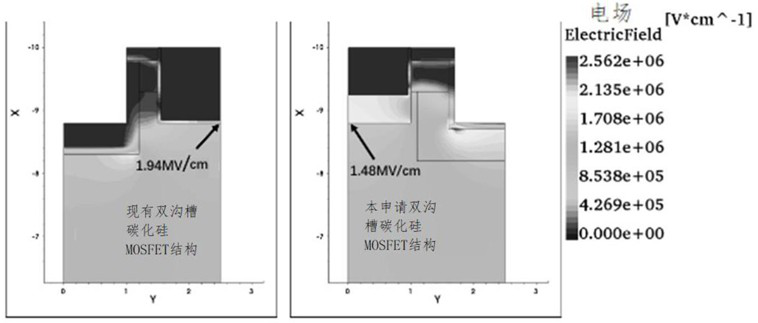

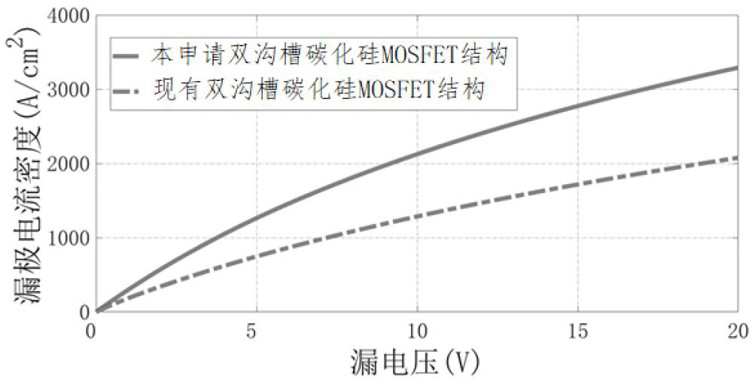

A silicon carbide and double-groove technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as limiting operating frequency and system efficiency, serious electric field concentration effect, and increased on-resistance, and achieves improved Reliability, reduced peak field strength, reduced on-resistance effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

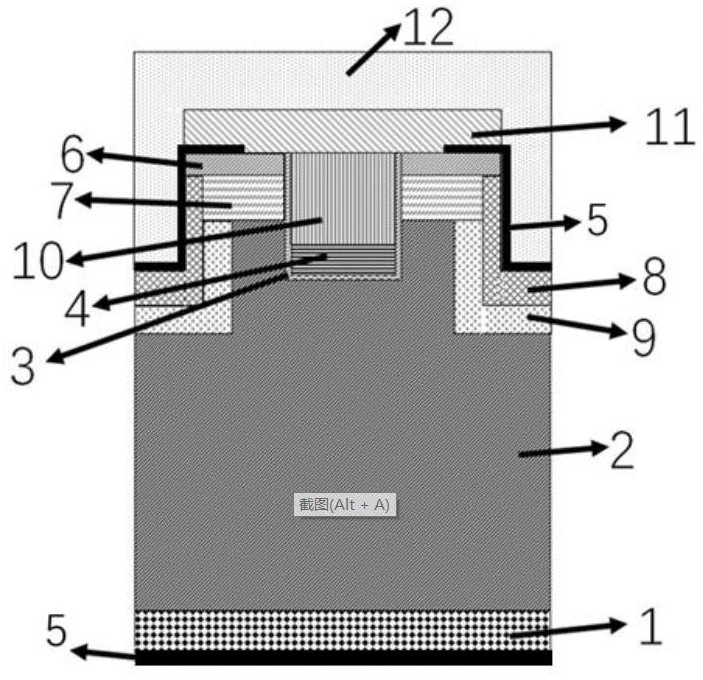

[0024] see figure 1 , the present invention discloses a double-trench silicon carbide MOSFET structure (hereinafter referred to as the structure), which is composed of a plurality of cell arrangements, each cell has an N++ type substrate 1 and an N-type drift layer 2, and in the N-type drift A gate trench and a source trench are formed on layer 2; an N-type hole blocking layer 9 and a P+ type shielding layer 8 are sequentially formed around the source trench from bottom to top, and the height of the N-type hole blocking layer 9 is not lo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More