Method for manufacturing silicon transistor with high back voltage and low negative resistance

A technology of silicon transistors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, body negative resistance effect devices, electrical components, etc., can solve the problems of high scrap rate, large dispersion of device electrical parameters, and low device withstand voltage level, etc. Achieve the effect of eliminating the generation of alloy points, reducing reverse leakage current, and uniform impurity distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

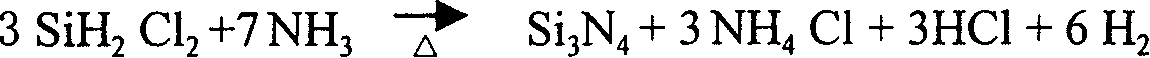

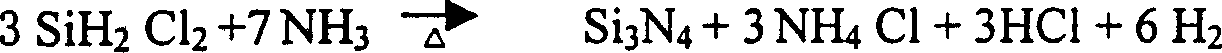

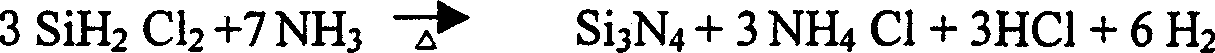

Method used

Image

Examples

Embodiment 1

[0023] Embodiment 1: 3DD202 type silicon NPN mesa high reverse voltage transistor. Specific steps are as follows:

[0024] (1) oxidation

[0025] The N-type silicon wafer with a resistivity of 40-60Ω·cm is compensated by high concentration phosphorus, thinned and polished, then cleaned, and then thermally oxidized by cold water natural drop method. The furnace temperature is 1200°C, the water temperature is room temperature, and the dripping speed is 15 drops. / min, oxidation time: dry oxygen 10min + wet oxygen 3 hours + dry oxygen 30min, oxygen flow 500ml / min.

[0026] (2) Furnace loading

[0027] will have SiO 2 The silicon wafer of the first layer is placed upright in the quartz boat, placed in the constant temperature zone of the quartz pipeline, and 0.8 grams of spectrally pure Ga 2 o 3 Put it into the quartz bowl of the inner reactor, and place it at the inlet end of the quartz pipe together.

[0028] (3) Low concentration doping

[0029] Tighten the ground caps a...

Embodiment 2

[0039] Embodiment 2: As described in Embodiment 1, the difference is that the resistivity of the N-type silicon wafer is 10-20 Ω·cm, the low-concentration doping time is 15 minutes, and the junction depth transition time is 14 hours.

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More