Method of manufacturing thin film transistor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

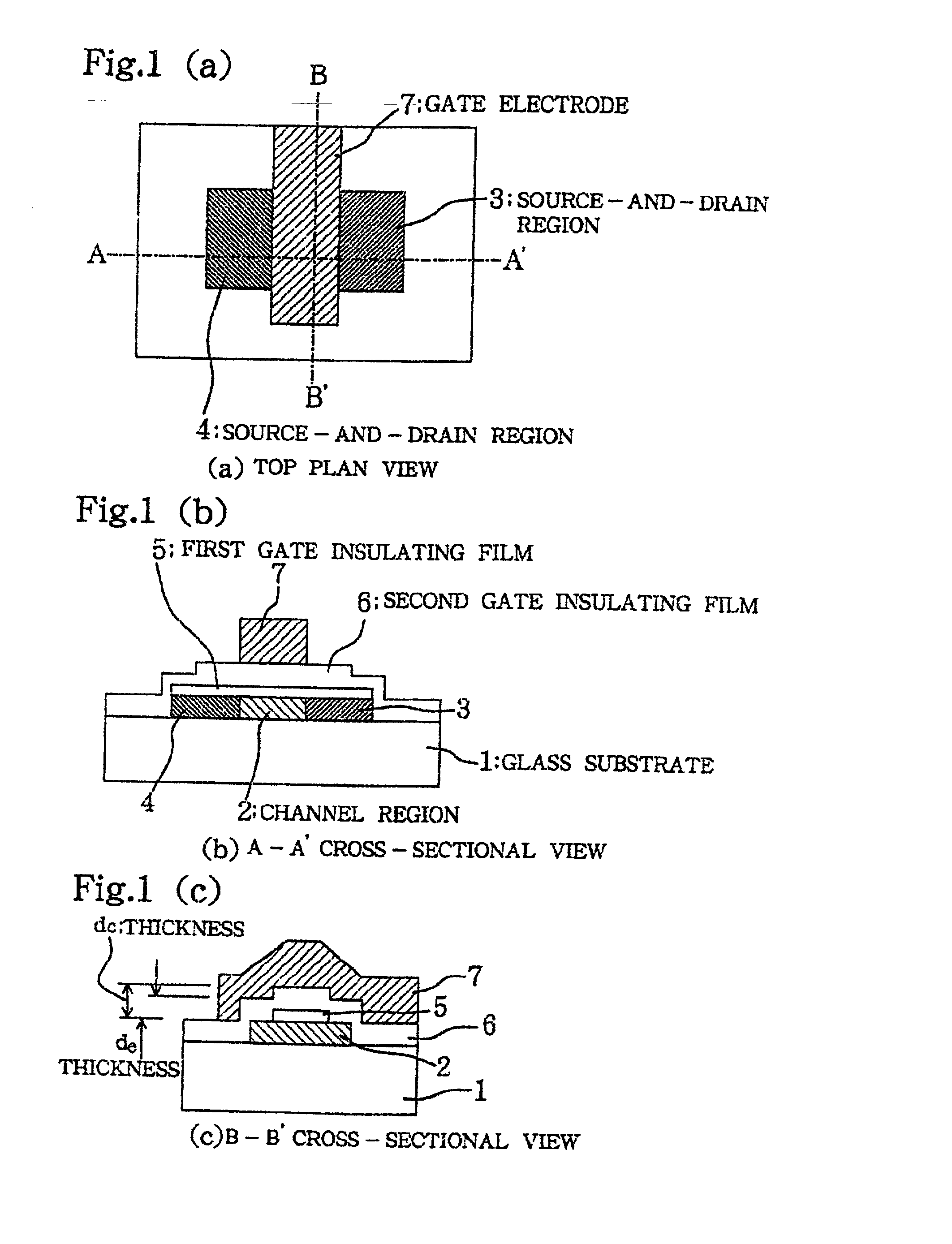

[0061] [Embodiment 1]

[0062] FIG. 1(a) is a top plan view of a thin film transistor according to a first embodiment of the invention, FIG. 1(b) is a cross-sectional view taken alone line A-A' of FIG. 1(a), and FIG. 1(c) is a cross-sectional view taken alone line B-B' of FIG. 1(a). The thin film transistor of FIGS. 1(a) to 1(c) comprises a glass substrate 1 as an insulator, and a silicon layer composed of a source-and-drain region 4, 3, and a channel region 2 and formed on the glass substrate 1 in an island shape. A first gate insulating film 5, which is formed on the island of the silicon layer, has a first width equal to the width of the silicon layer in the source-drain direction, i.e., the B-B' direction and a second width smaller than the width of the silicon layer in the gate electrode direction, i.e., in the B-B' direction. In the gate electrode direction, a below-described gate electrode extends across the first-gate insulating film 5. These regions of the silicon layer and th...

embodiment 2

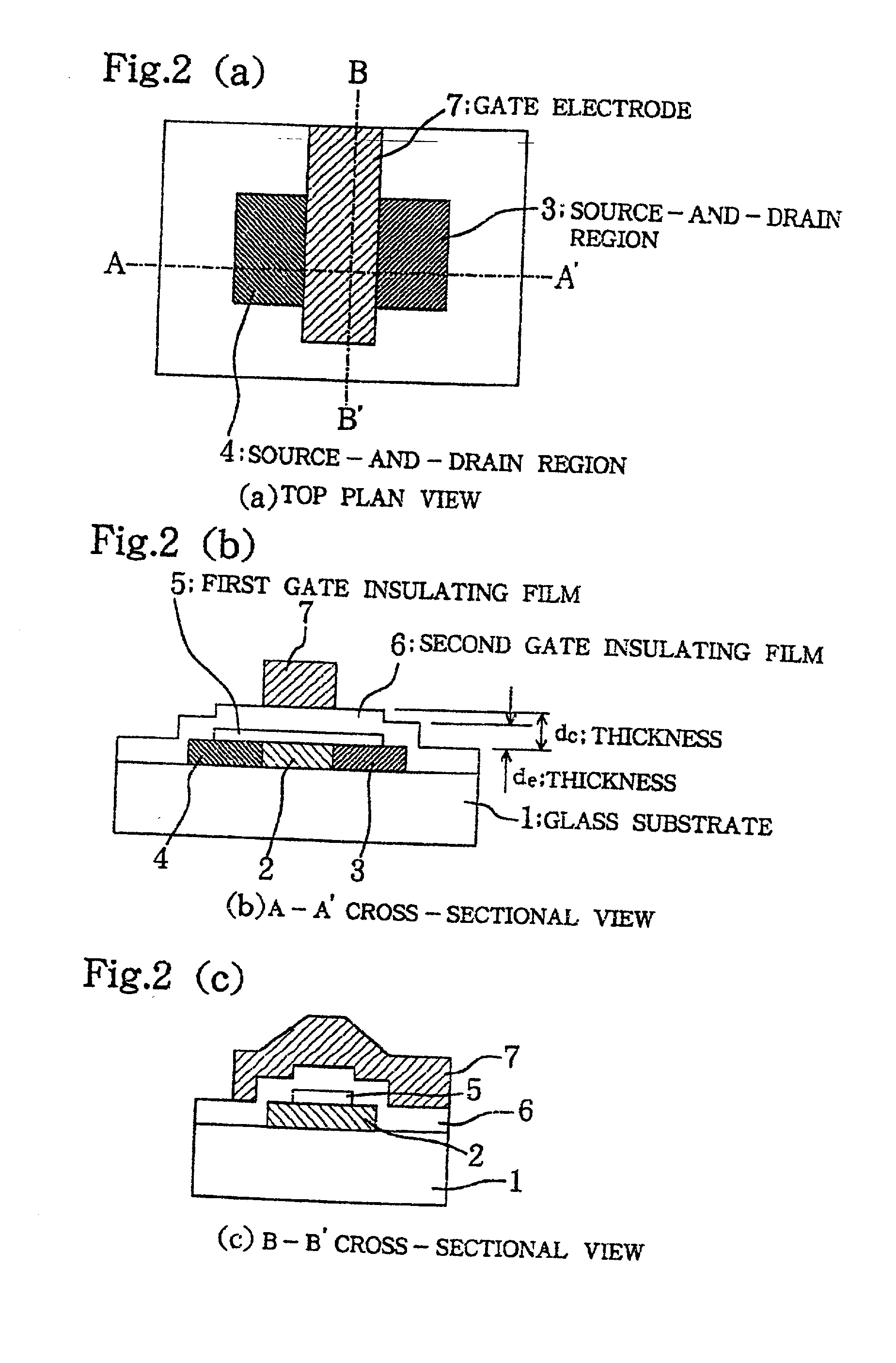

[0069] [Embodiment 2]

[0070] FIG. 2(a) is a top plan view of a thin film transistor according to a second embodiment of the present invention, FIG. 2(b) is a cross-sectional view taken alone line A-A' of FIG. 2(a), and FIG. 2(c) is a cross-sectional view taken alone line B-B' of FIG. 2 (a). The thin film transistor of FIGS. 2(a) to 2(c) comprises a glass substrate 1 as an insulator, a silicon layer, which is composed of a source-and-drain region 4, 3 and a channel region 2 and formed on the glass substrate 1 in an island shape, a first gate insulating film 5, a second gate insulating film 6, and a gate electrode (hereinafter also called the gate) 7. Because the channel region 2, the gate insulating films 5, 6 and the gate 7 constitute the so-called metal-insulator-semiconductor structure, it is possible control a drain current by controlling a voltage applied to the gate 7. The material for the first and second gate insulating films 5, 6 is exemplified by silicon dioxide, silicon nit...

embodiment 3

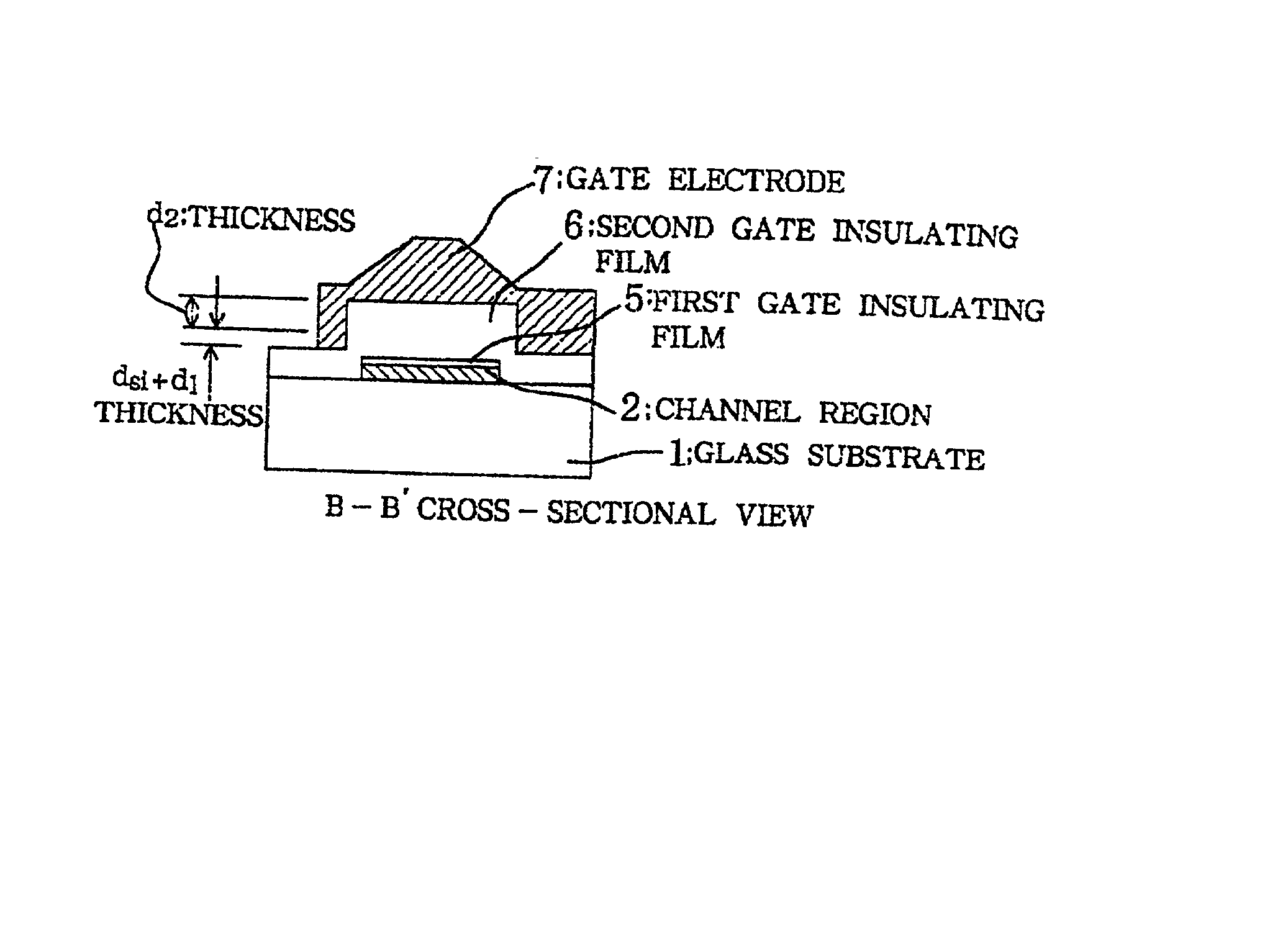

[0076] [Embodiment 3]

[0077] FIGS. 3(a) is a top plan view of a thin film transistor according to a third embodiment of the present invention, FIG. 3(b) is a cross-sectional view taken alone line A-A' of FIG. 3(a), and FIG. 3(c) is a cross-sectional view taken alone line B-B' of FIG. 3(a). The thin film transistor of FIGS. 3(a) to 3(c) comprises a glass substrate 1 as an insulator, a silicon layer, which is composed of a source-and-drain region 4, 3 and a channel region 2 and formed on the glass substrate 1 in an island shape, a first gate insulating film 5, a second gate insulating film 6, and a gate electrode 7. Because the channel region 2, the gate insulating films 5, 6 and the gate 7 constitute the so-called metal-insulator-semiconductor structure, it is possible control a drain current by controlling a voltage applied to the gate 7. The material for the first and second gate insulating films 5, 6 is exemplified by silicon dioxide, silicon nitride, aluminum oxide and tantalum ox...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More