Patents

Literature

67results about How to "Reduce defect level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

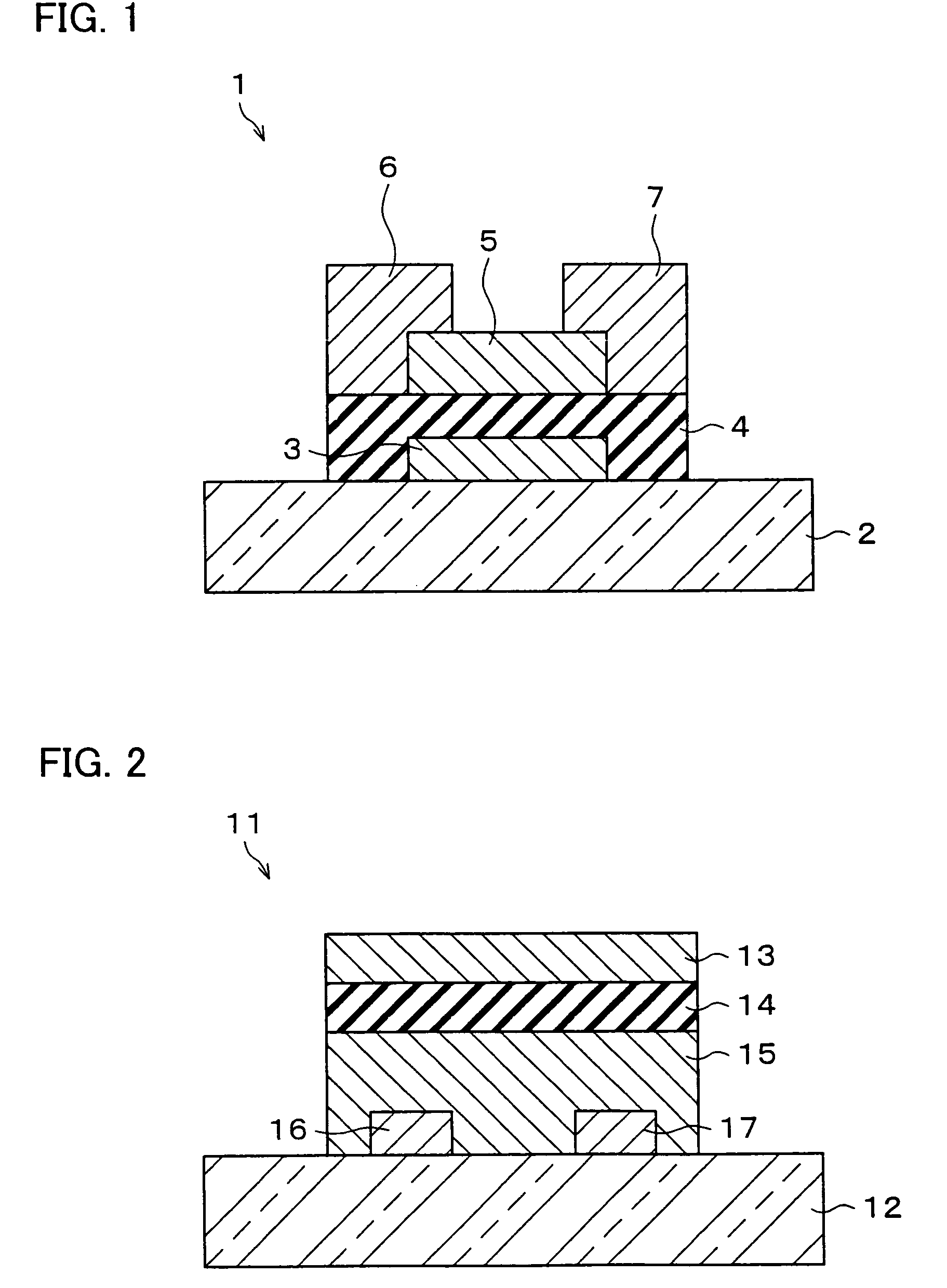

Semiconductor device and display comprising same

InactiveUS20050173734A1Improve performanceVersatile techniqueTransistorSemiconductor/solid-state device detailsMOSFETDevice material

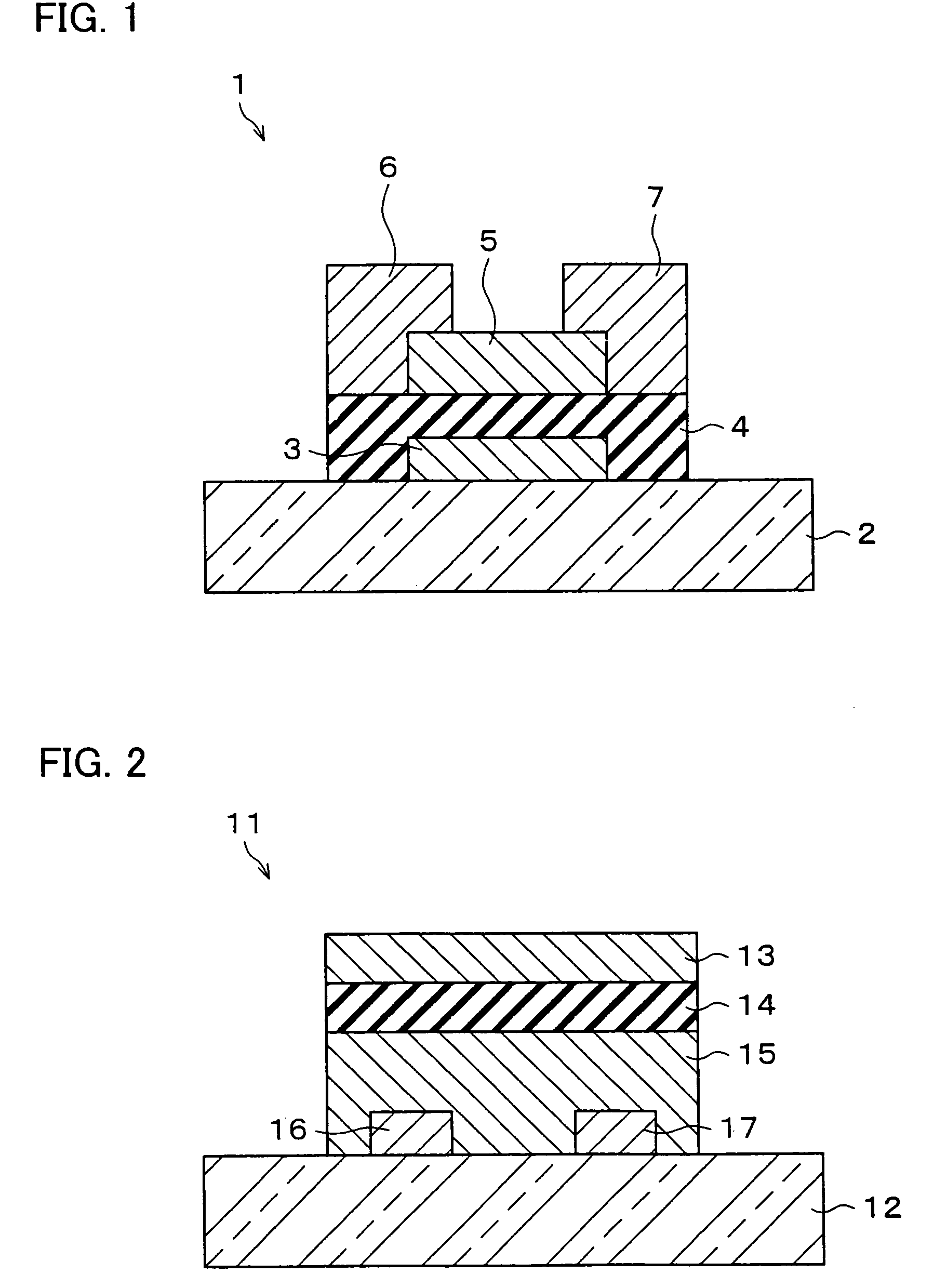

In an inverse-stagger MOSFET (1), a gate insulating layer (4) made of amorphous aluminum oxide is so formed as to face a channel layer (5) which serves as the semiconductor layer, and which is made of zinc oxide. With this arrangement, a defect level at an interface between the channel layer (5) and the gate insulating layer (4) is reduced, thereby obtaining performance equivalent to that of a semiconductor apparatus in which all the layered films are crystalline. This technique is applicable to a staggered MOSFET and the like, and has high versatility.

Owner:MASASHI KAWASAKI +2

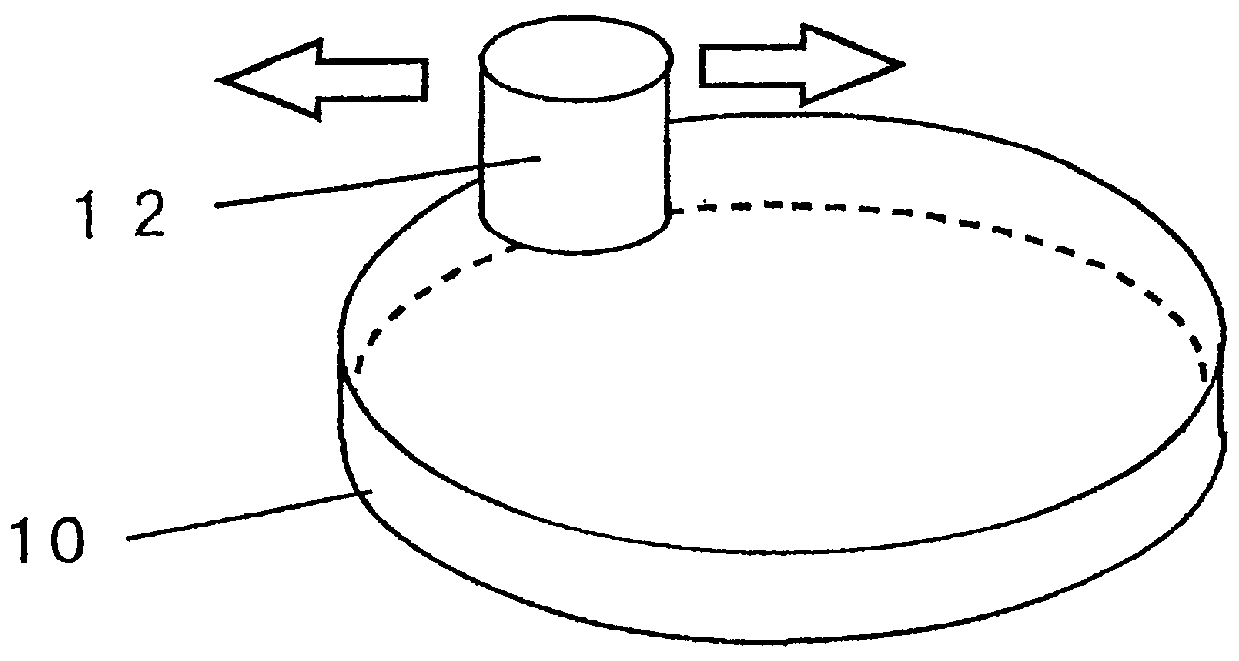

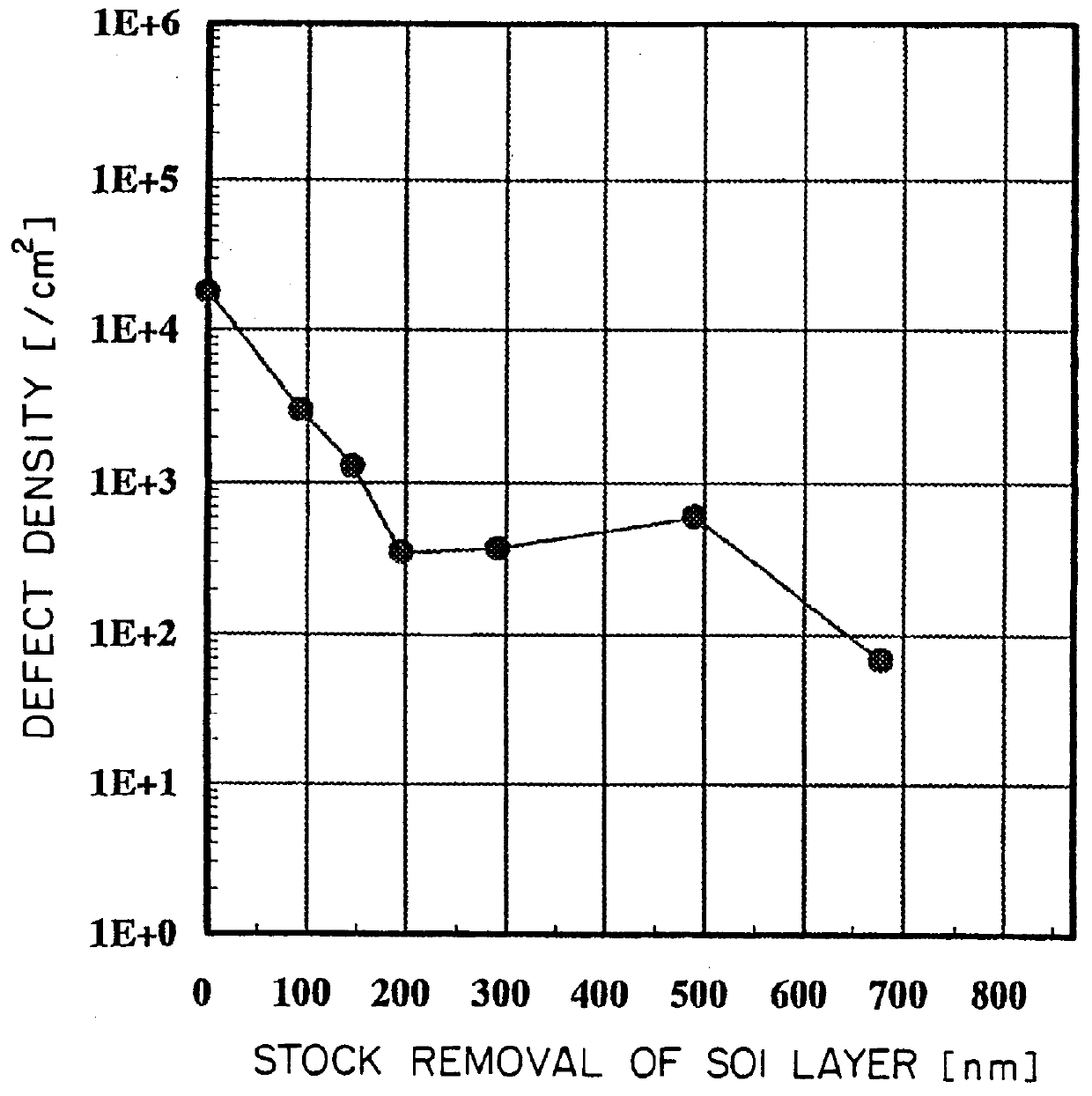

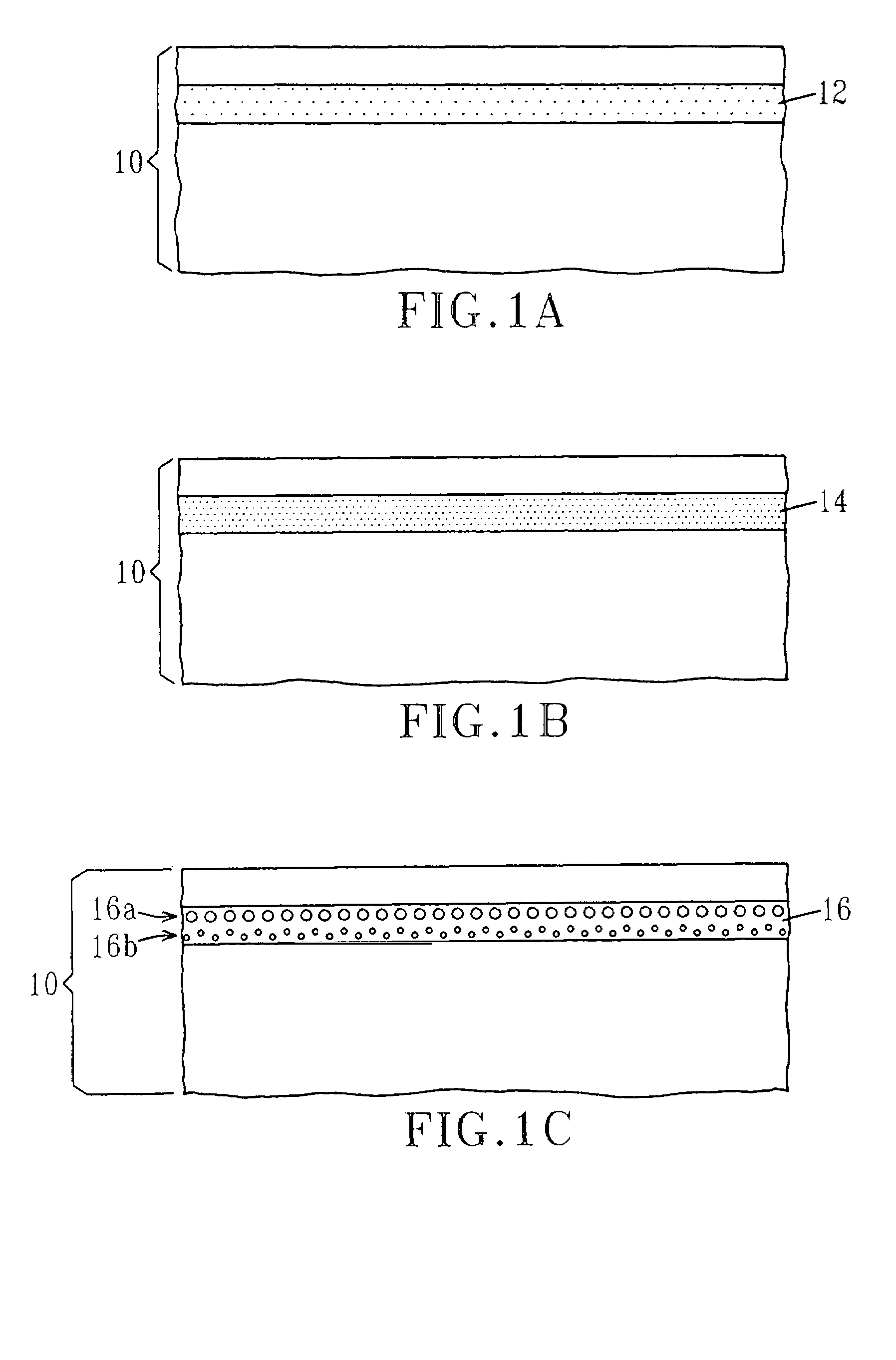

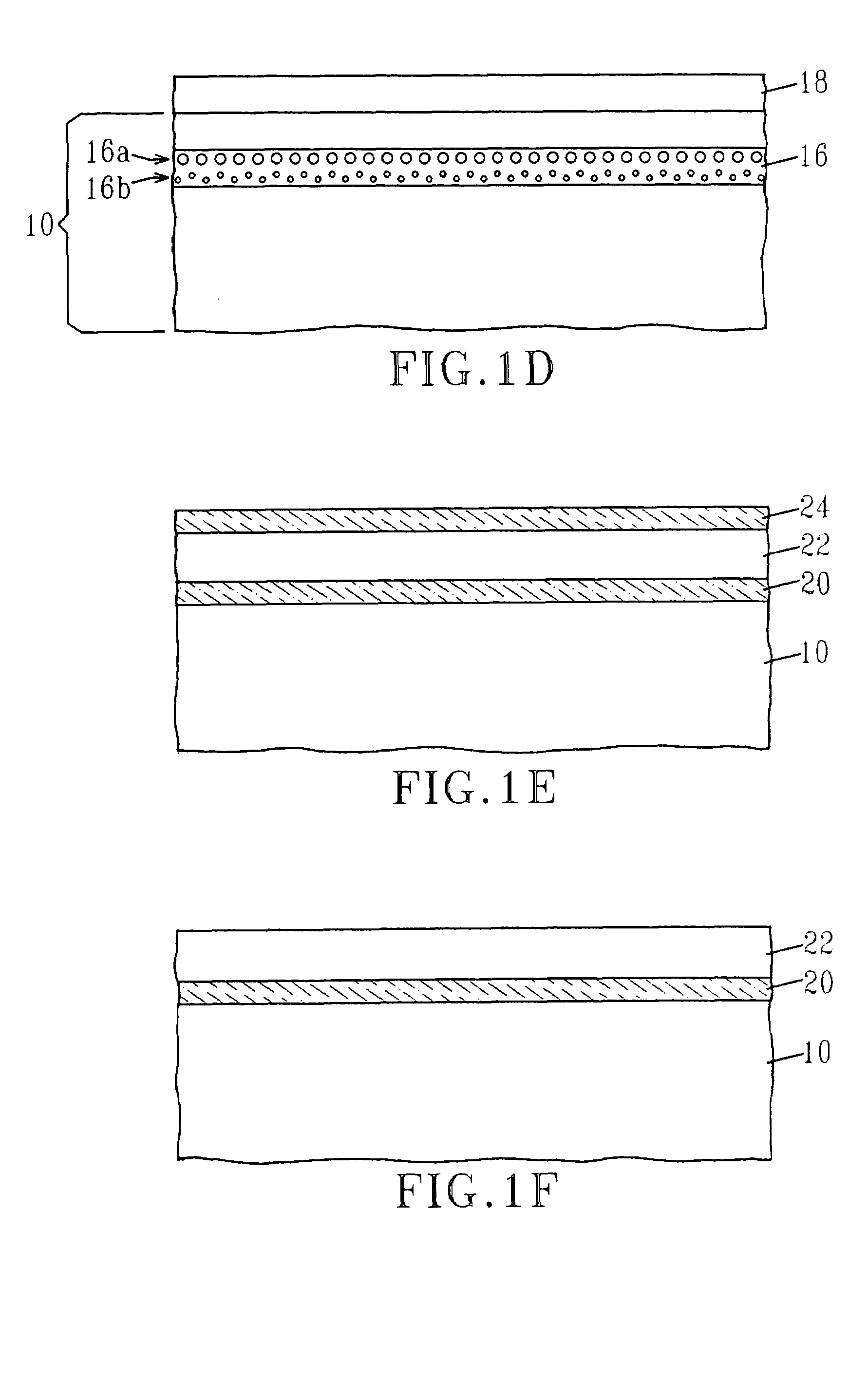

Method of fabricating an SOI wafer and SOI wafer fabricated thereby

InactiveUS6140210AReliably removedUniform thicknessSolid-state devicesSemiconductor/solid-state device manufacturingNoble gasEtching

In a method of fabricating an SOI wafer, an oxide film is formed on the surface of at least one of two silicon wafers; hydrogen ions or rare gas ions are implanted into the upper surface of one of the two silicon wafers in order to form a fine bubble layer (enclosed layer) within the wafer; the ion-implanted silicon wafer is superposed on the other silicon wafer such that the ion-implanted surface comes into close contact with the surface of the other silicon wafer via the oxide film; heat treatment is performed in order to delaminate a portion of the ion-implanted wafer while the fine bubble layer is used as a delaminating plane, in order to form a thin film to thereby obtain an SOI wafer. In the method, a defect layer at the delaminated surface of the thus-obtained SOI wafer is removed to a depth of 200 nm or more through vapor-phase etching, and then mirror polishing is performed. Therefore, the obtained SOI wafer has an extremely low level of defects and a high thickness uniformity.

Owner:SHIN-ETSU HANDOTAI CO LTD

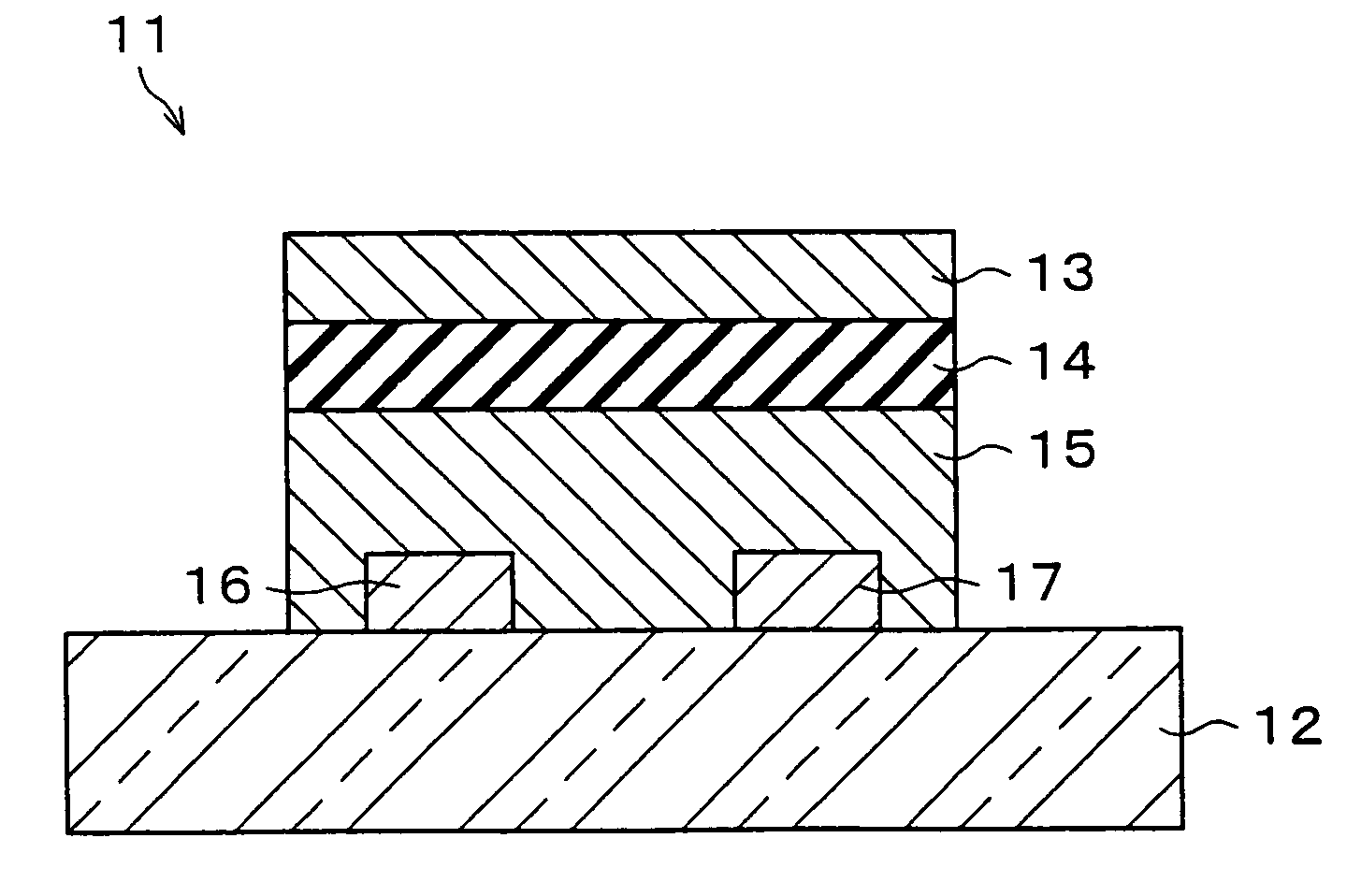

Semiconductor device and display comprising same

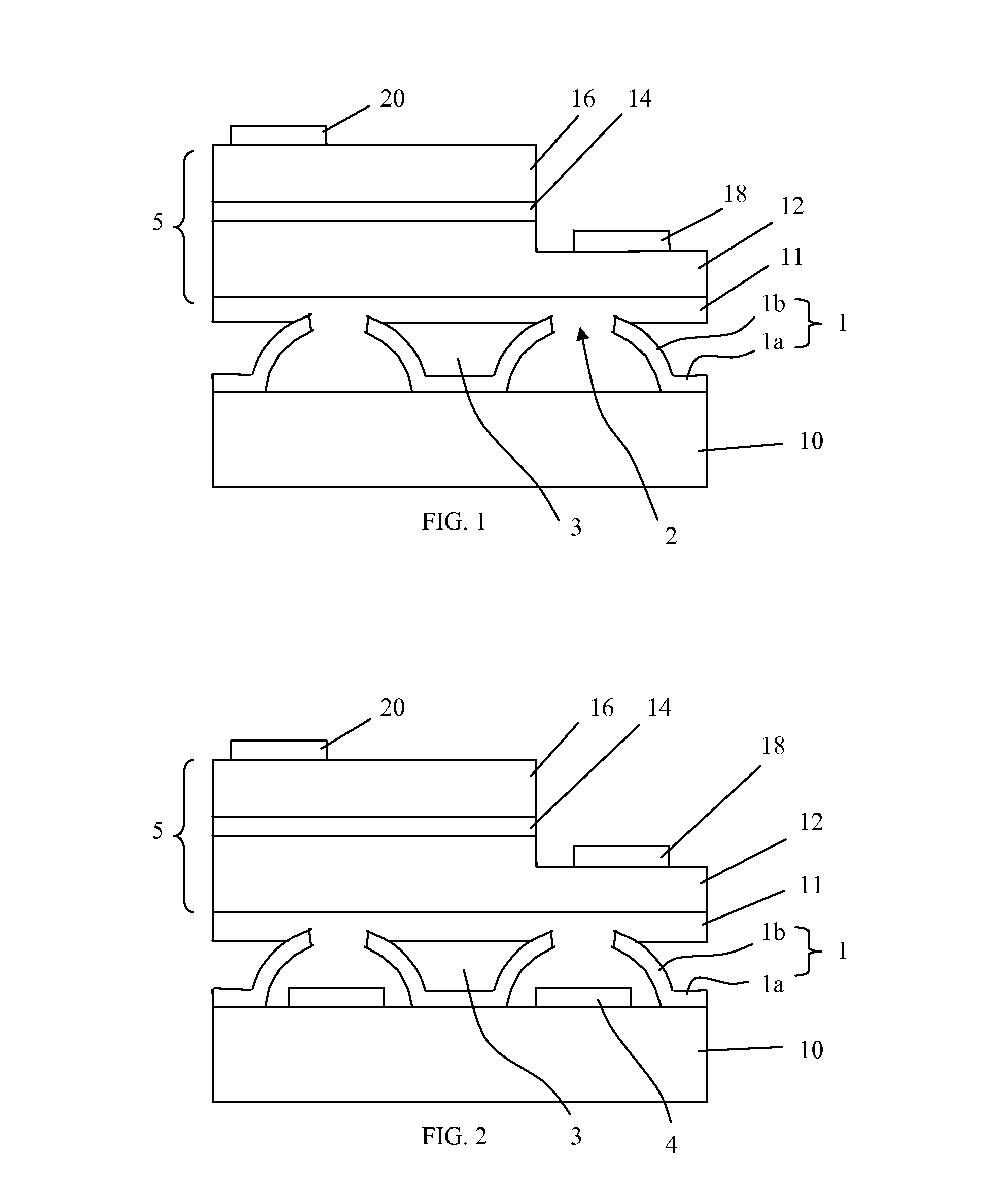

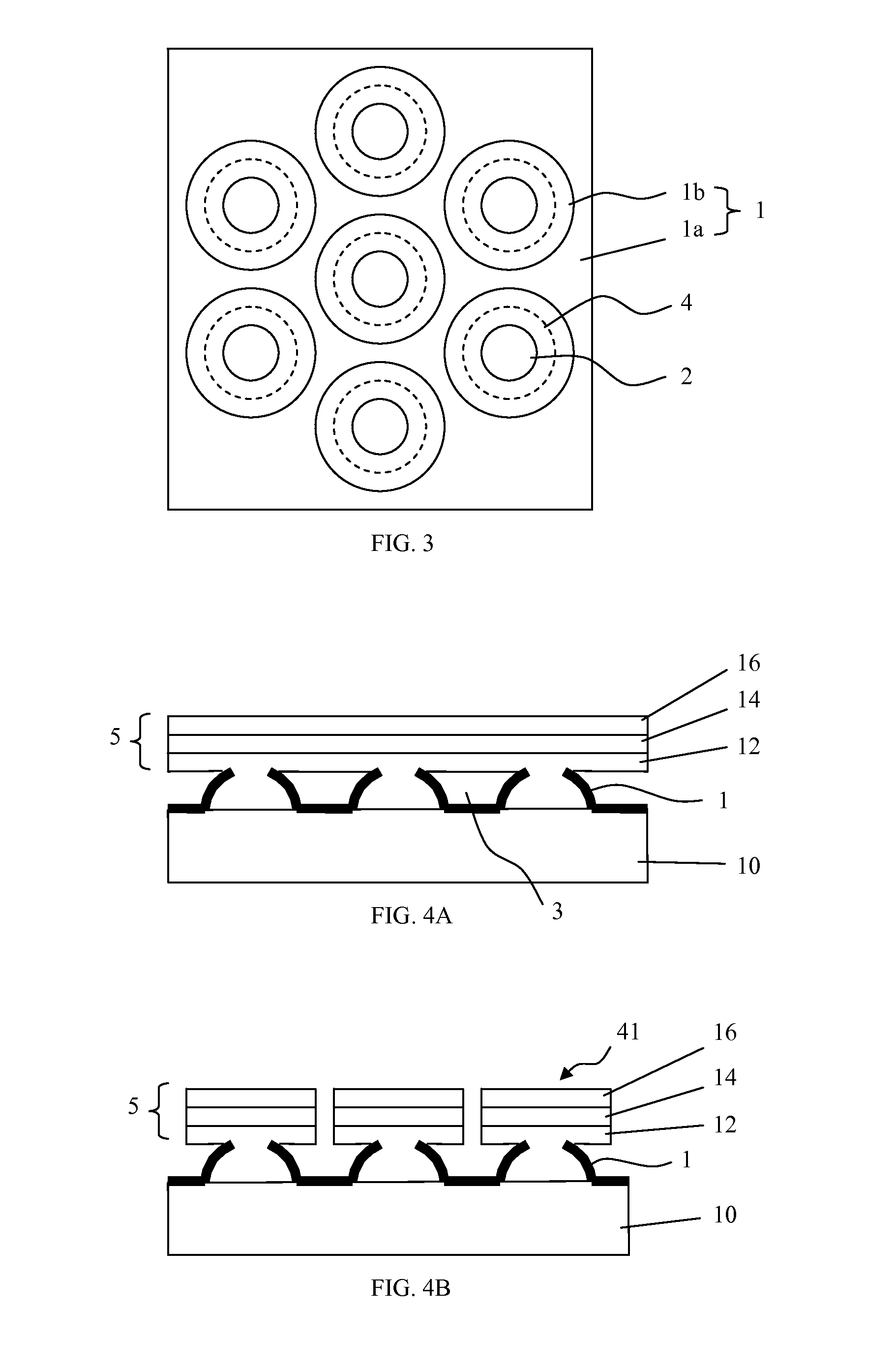

InactiveUS7205640B2Improve performanceVersatile techniqueTransistorSemiconductor/solid-state device detailsMOSFETDisplay device

In an inverse-stagger MOSFET (1), a gate insulating layer (4) made of amorphous aluminum oxide is so formed as to face a channel layer (5) which serves as the semiconductor layer, and which is made of zinc oxide. With this arrangement, a defect level at an interface between the channel layer (5) and the gate insulating layer (4) is reduced, thereby obtaining performance equivalent to that of a semiconductor apparatus in which all the layered films are crystalline. This technique is applicable to a staggered MOSFET and the like, and has high versatility.

Owner:MASASHI KAWASAKI +2

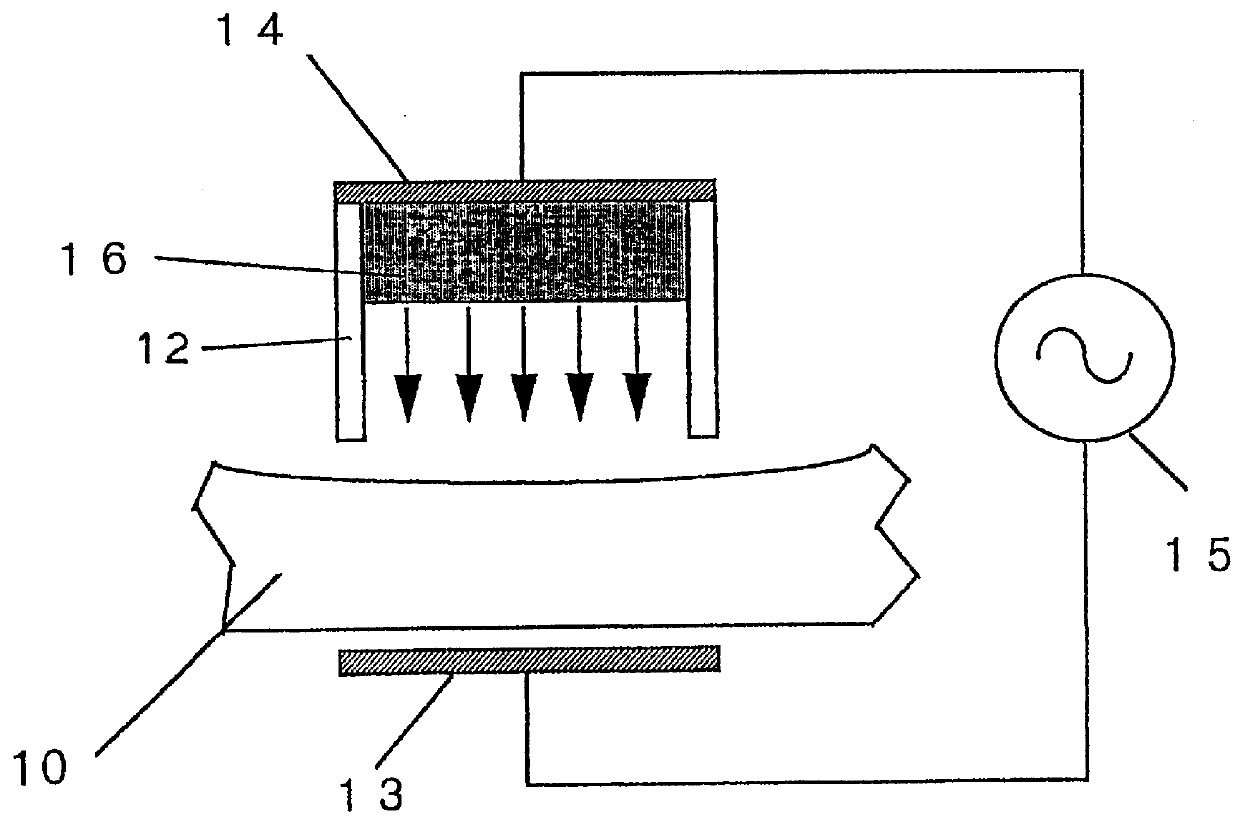

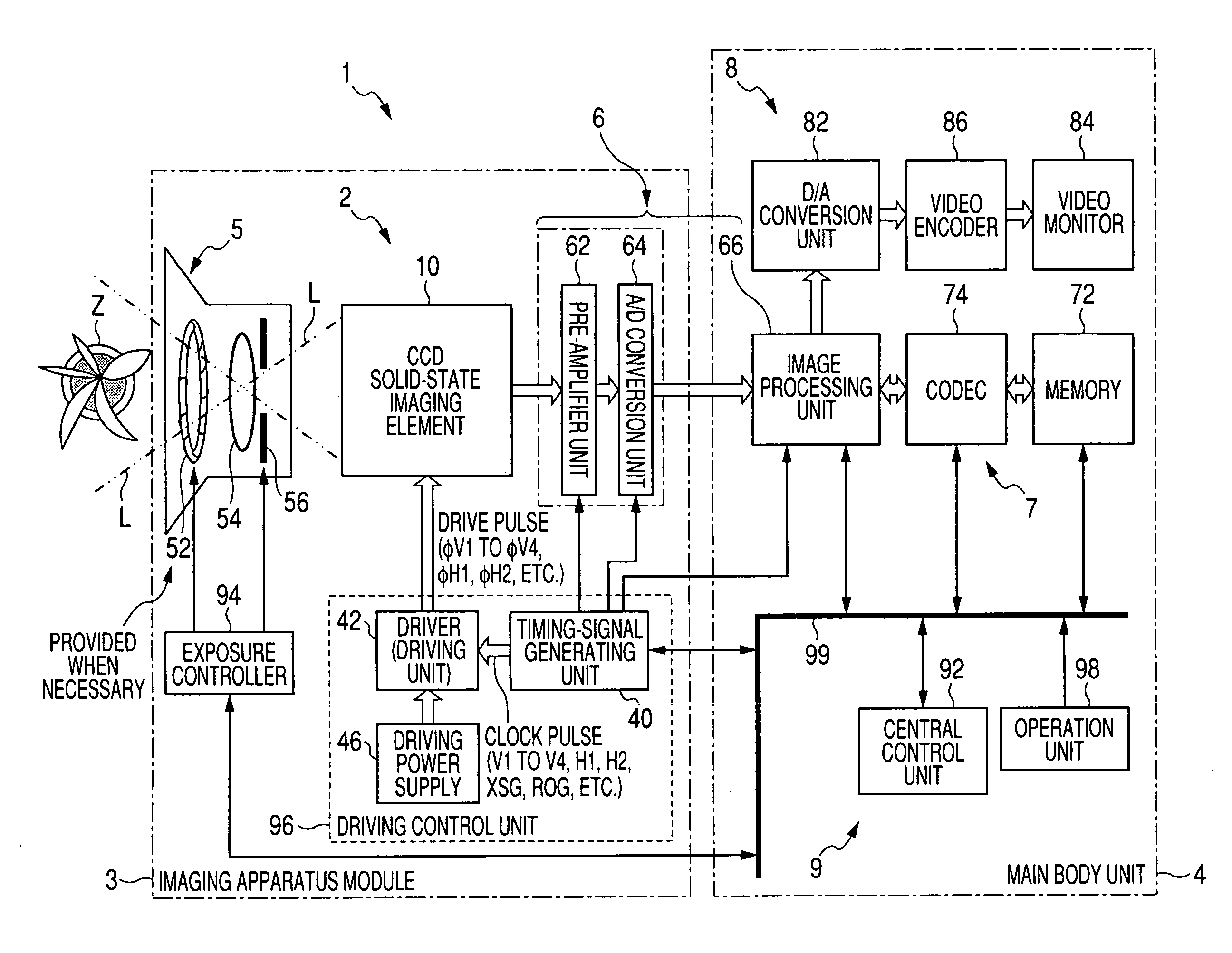

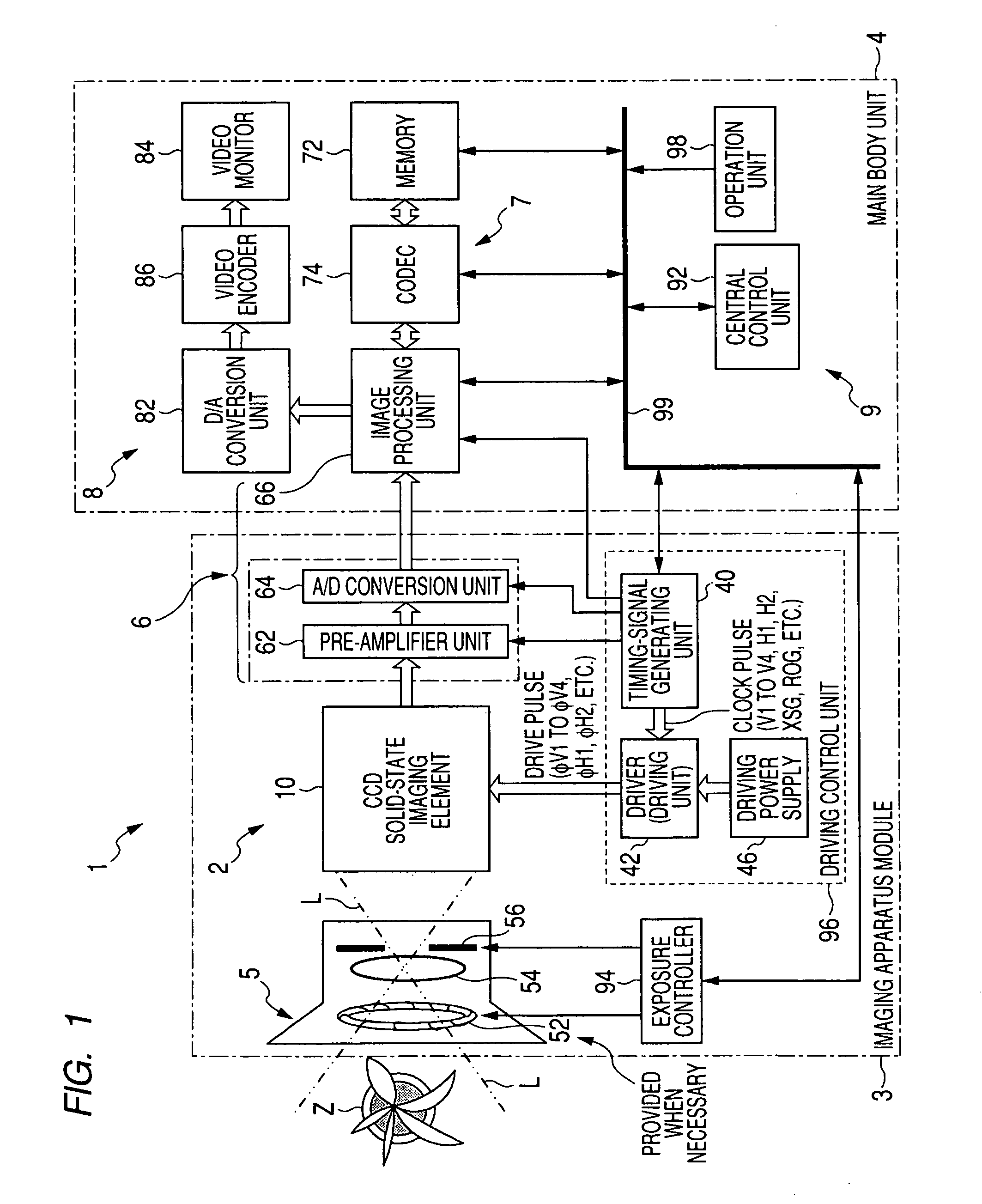

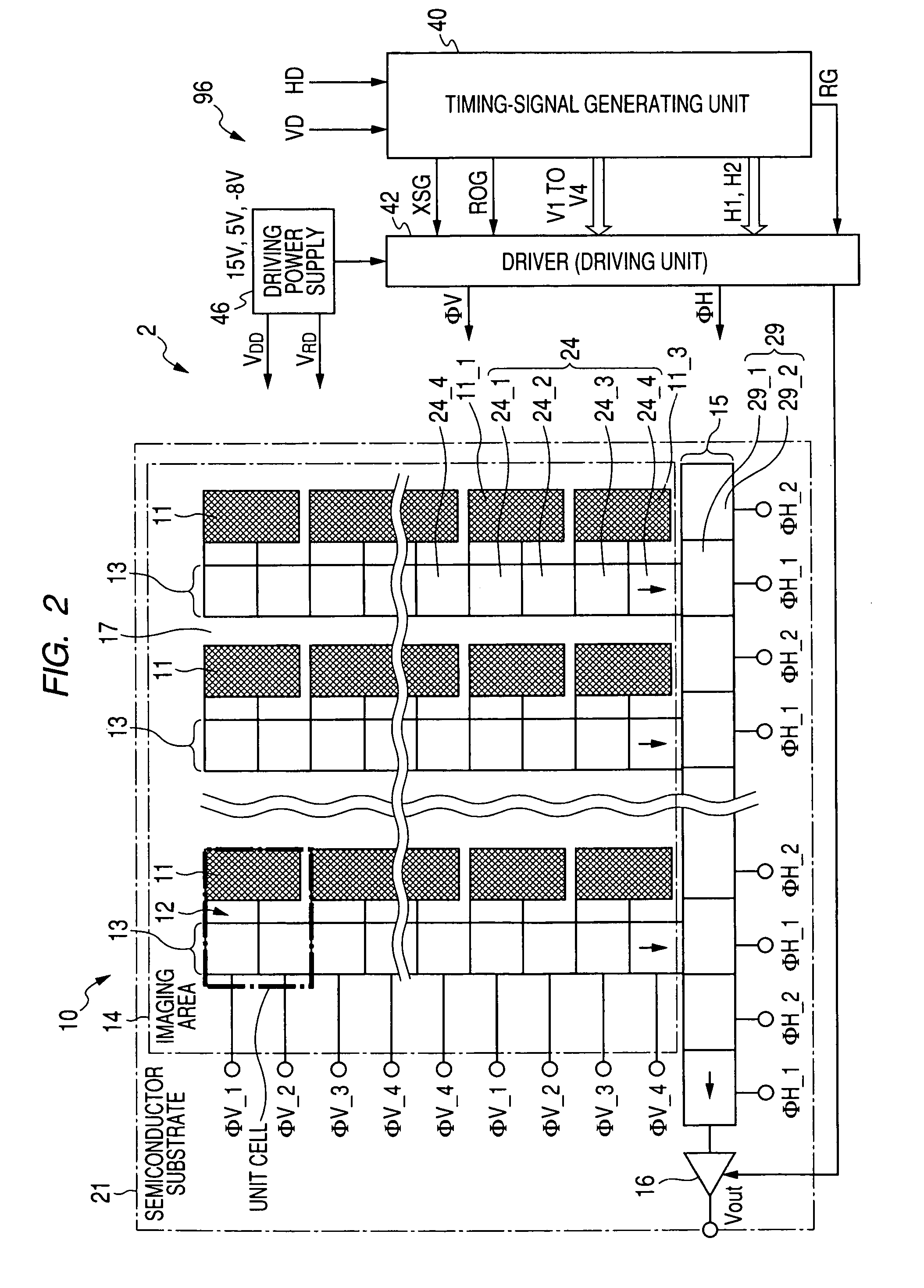

Imaging method, imaging apparatus, and driving device

InactiveUS20080218598A1Total current dropReduce defect levelTelevision system detailsRadiation controlled devicesPhysicsImaging equipment

A driving device includes a driving control unit that reads out the signal charge generated by at least the charge generating section for a low-sensitivity pixel signal to the charge transfer section, after the predetermined timing, continues incidence of the electromagnetic wave and, after continuing the incidence of the electromagnetic wave, reads out the signal charge generated by at least the charge generating section for a high-sensitivity pixel signal to the charge transfer section, transfers the signal charge read out to the charge transfer section through the charge transfer section, and, concerning at least one of the signal charges for the high-sensitivity pixel signal and the low-sensitivity pixel signal, every time the signal charge is read out to the charge transfer section, transfers the signal charge read out to the charge transfer section through the charge transfer section without retaining the signal charge in the charge transfer section.

Owner:SONY CORP

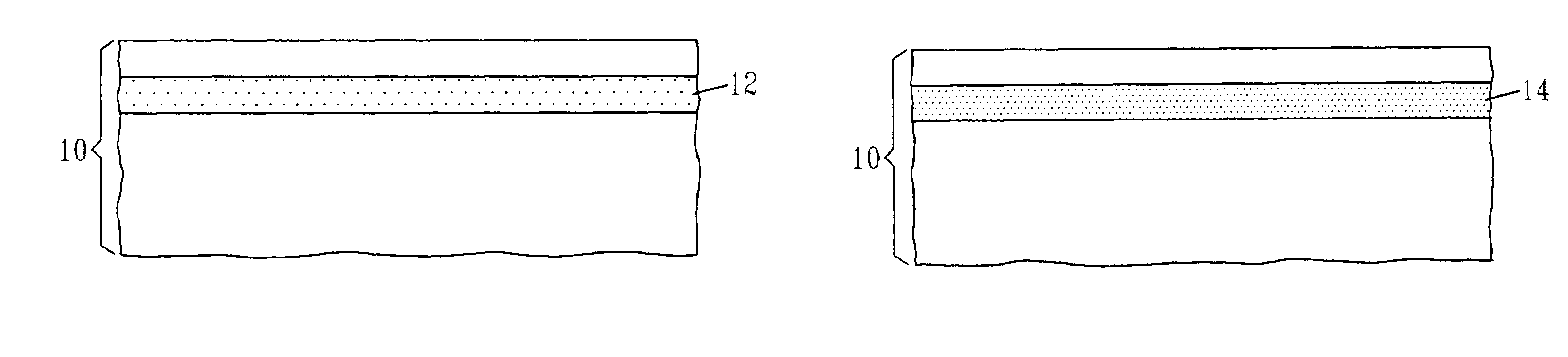

SOI by oxidation of porous silicon

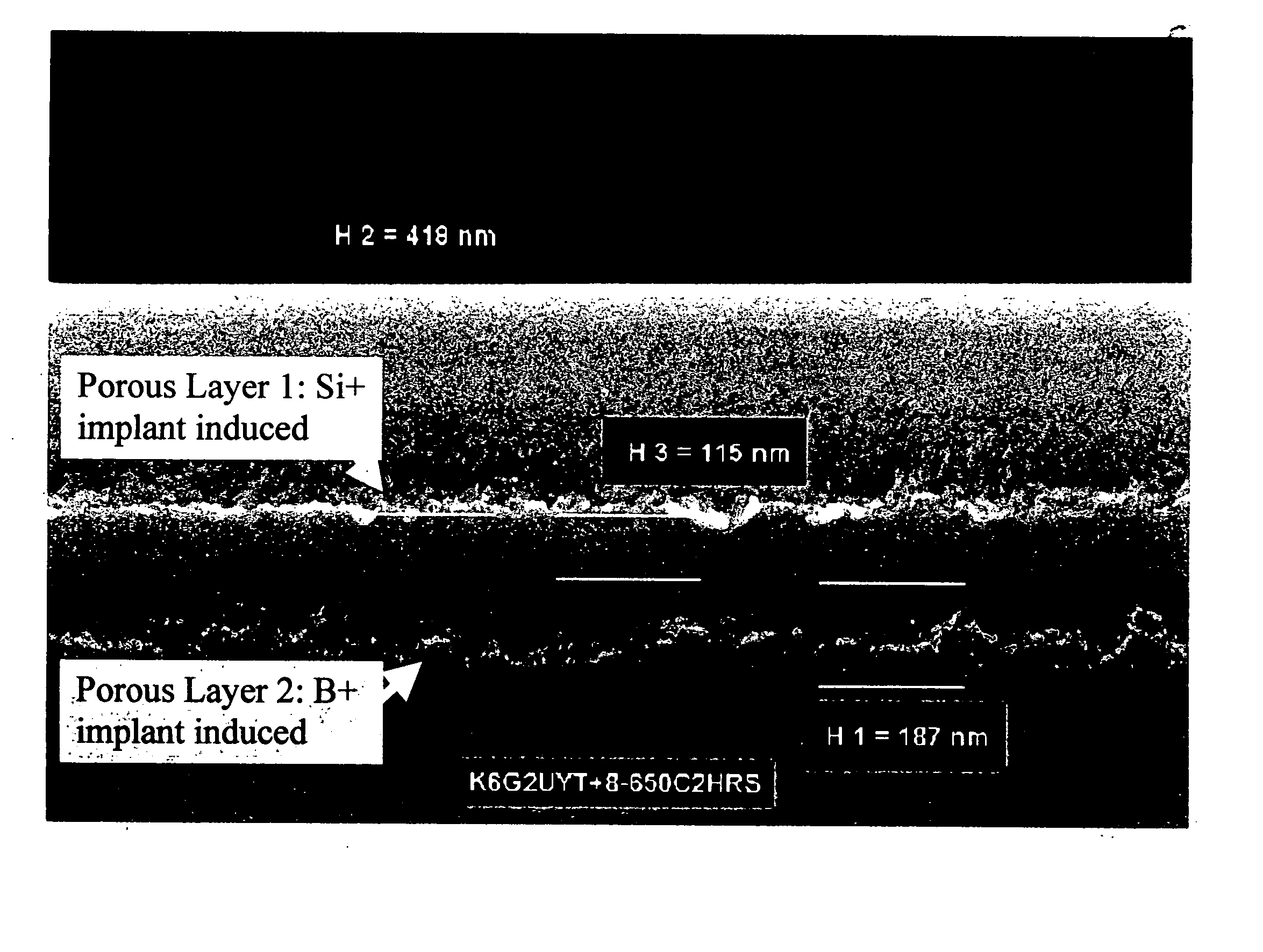

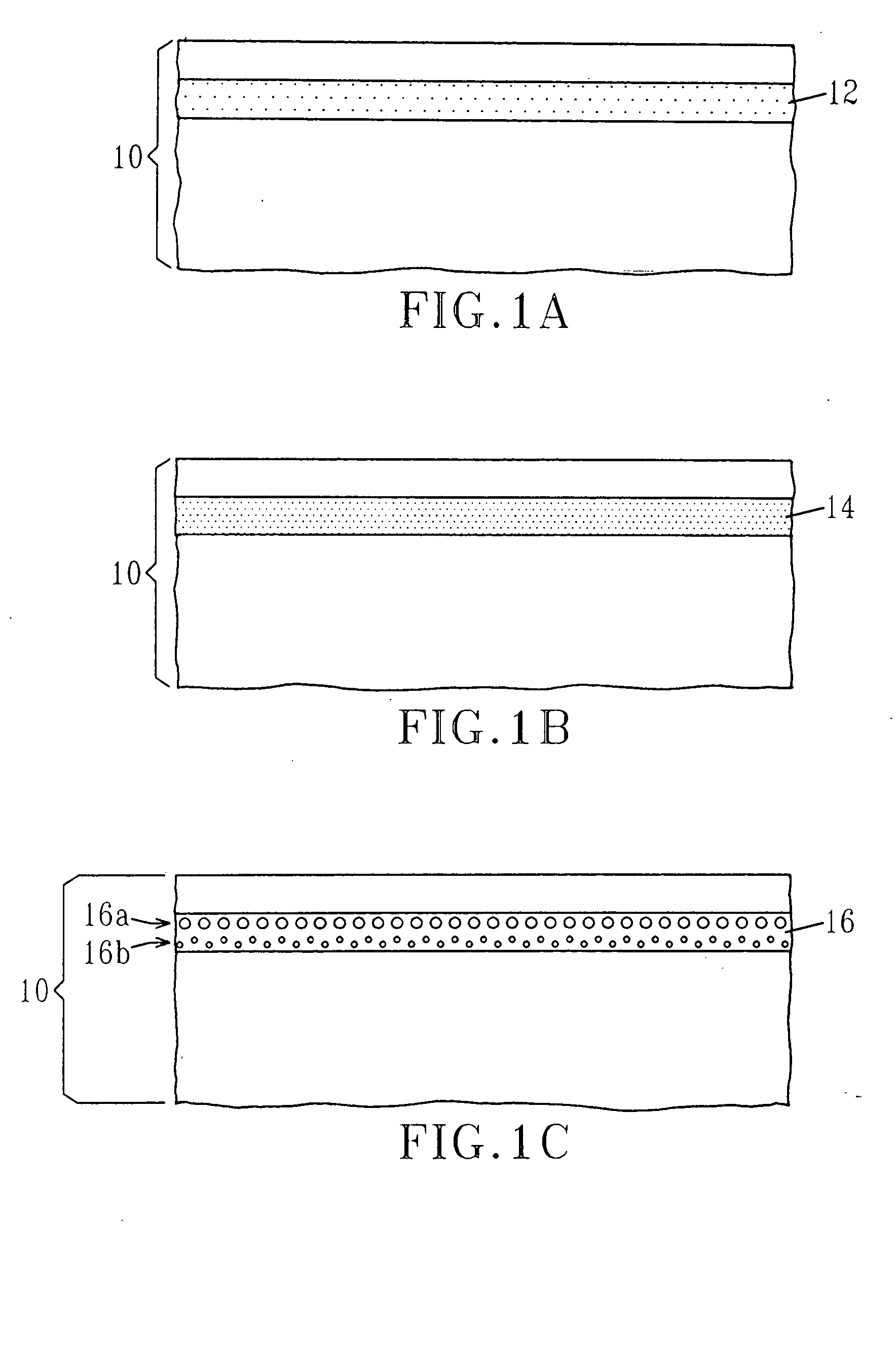

InactiveUS20050067294A1Simple and cost-effectiveReduce defect levelAnodisationVacuum evaporation coatingDopantPorous layer

A method in which a SOI substrate structure is fabricated by oxidation of graded porous Si is provided. The graded porous Si is formed by first implanting a dopant (p- or n-type) into a Si-containing substrate, activating the dopant using an activation anneal step and then anodizing the implanted and activated dopant region in a HF-containing solution. The graded porous Si has a relatively coarse top layer and a fine porous layer that is buried beneath the top layer. Upon a subsequent oxidation step, the fine buried porous layer is converted into a buried oxide, while the coarse top layer coalesces into a solid Si-containing over-layer by surface migration of Si atoms.

Owner:GLOBALFOUNDRIES INC

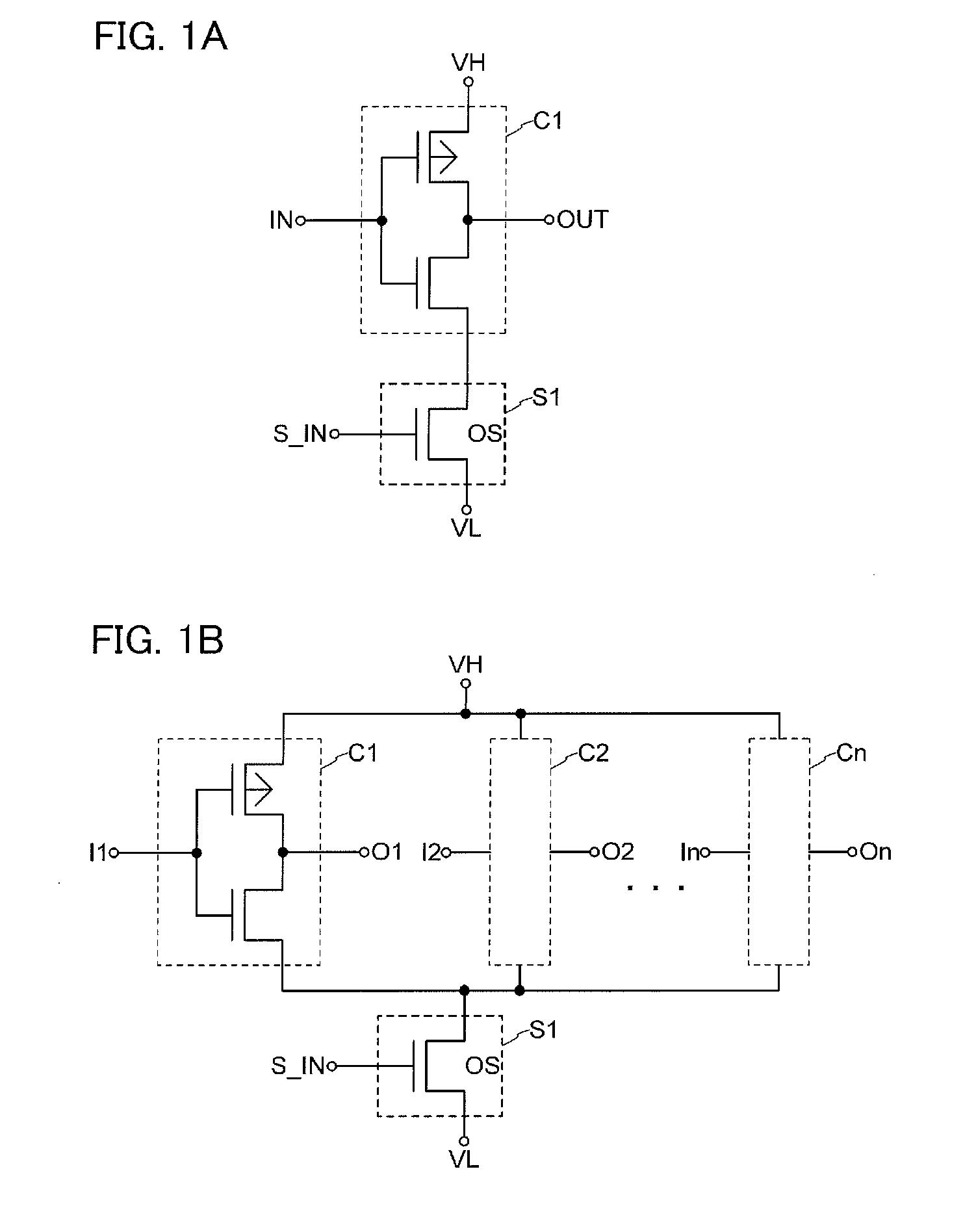

Semiconductor device

InactiveUS20110140099A1Reduce standby powerGood effectTransistorSemiconductor/solid-state device detailsPower semiconductor deviceElectricity

One object is to provide a new semiconductor device whose standby power is sufficiently reduced. The semiconductor device includes a first power supply terminal, a second power supply terminal, a switching transistor using an oxide semiconductor material and an integrated circuit. The first power supply terminal is electrically connected to one of a source terminal and a drain terminal of the switching transistor. The other of the source terminal and the drain terminal of the switching transistor is electrically connected to one terminal of the integrated circuit. The other terminal of the integrated circuit is electrically connected to the second power supply terminal.

Owner:SEMICON ENERGY LAB CO LTD

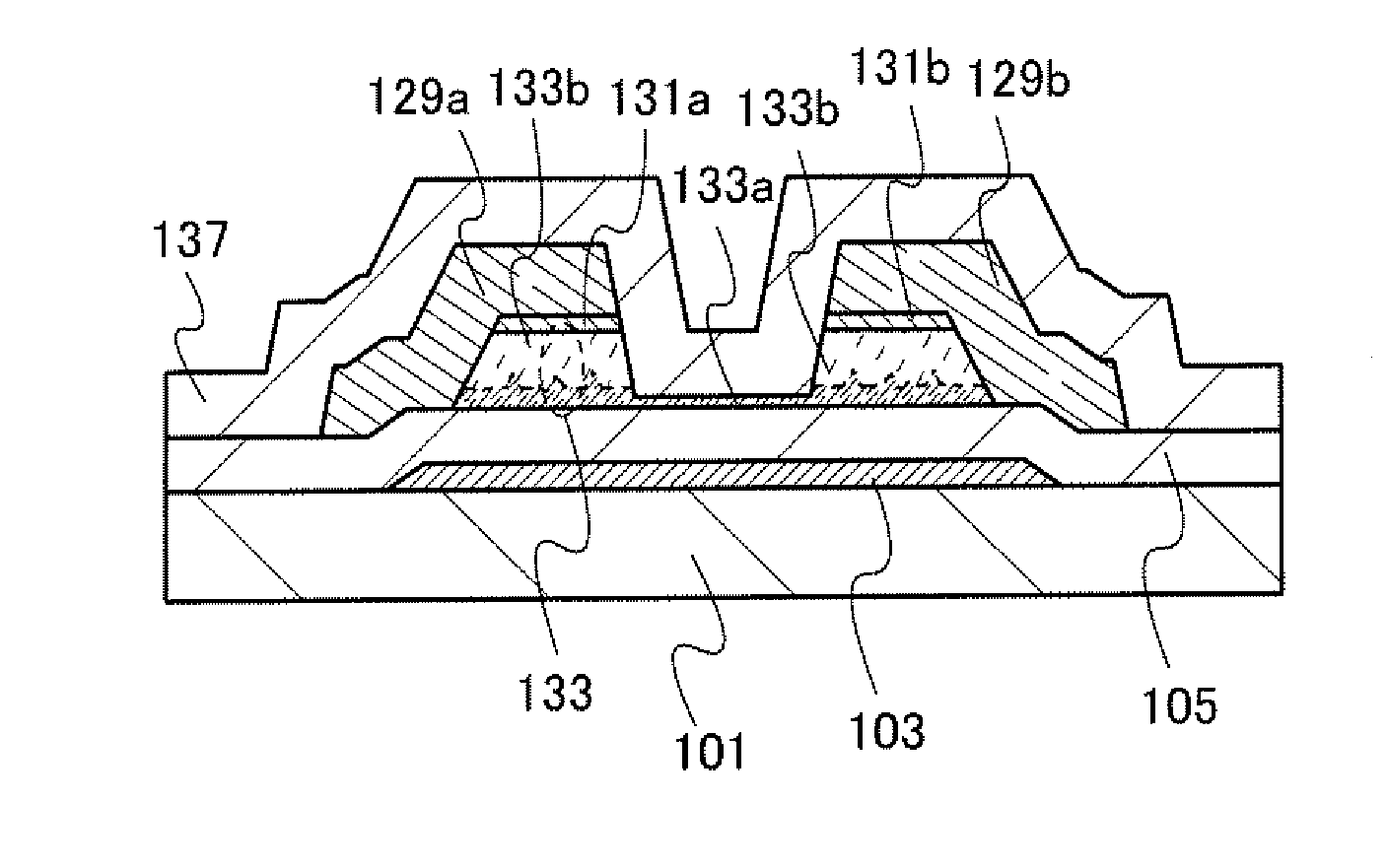

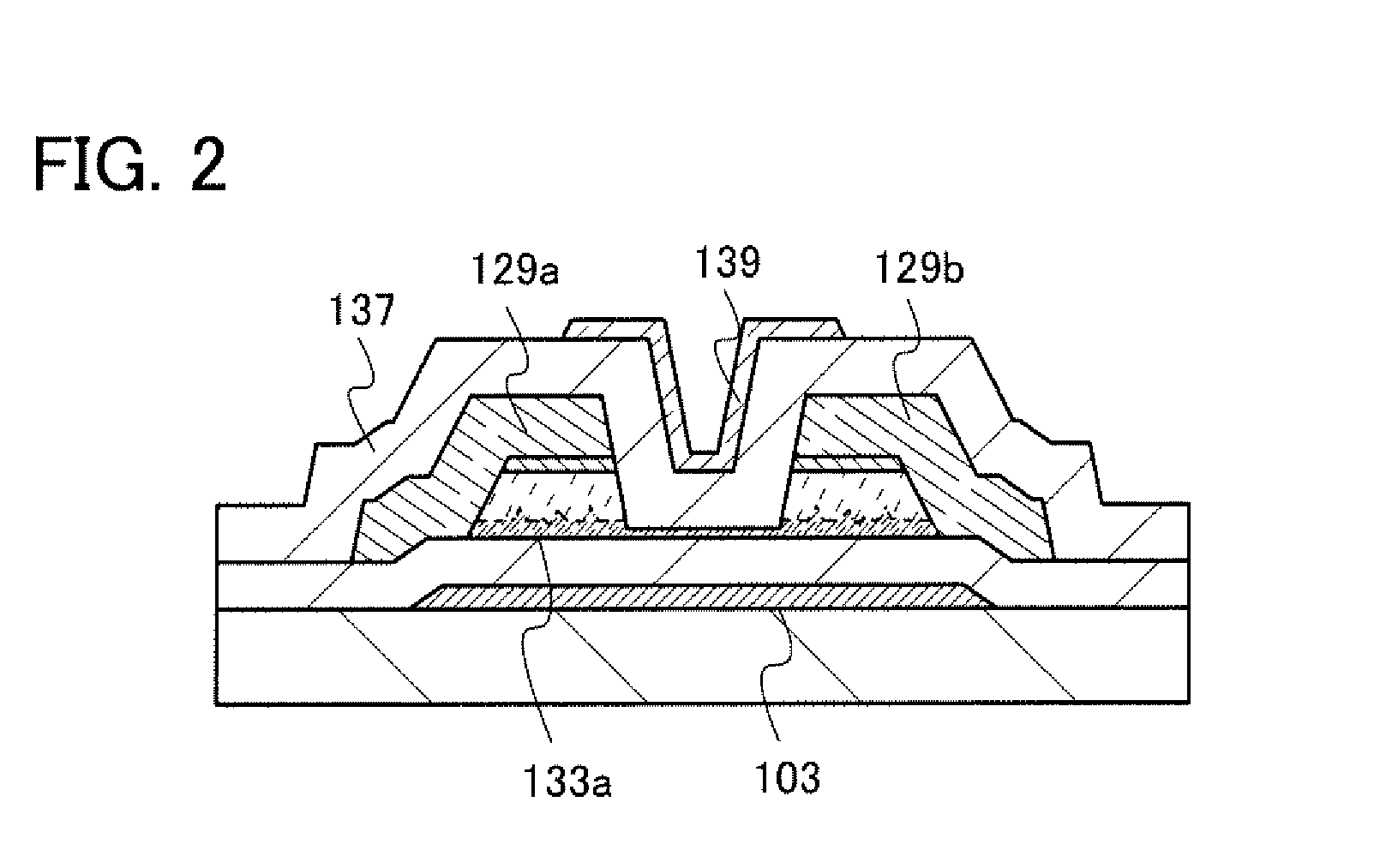

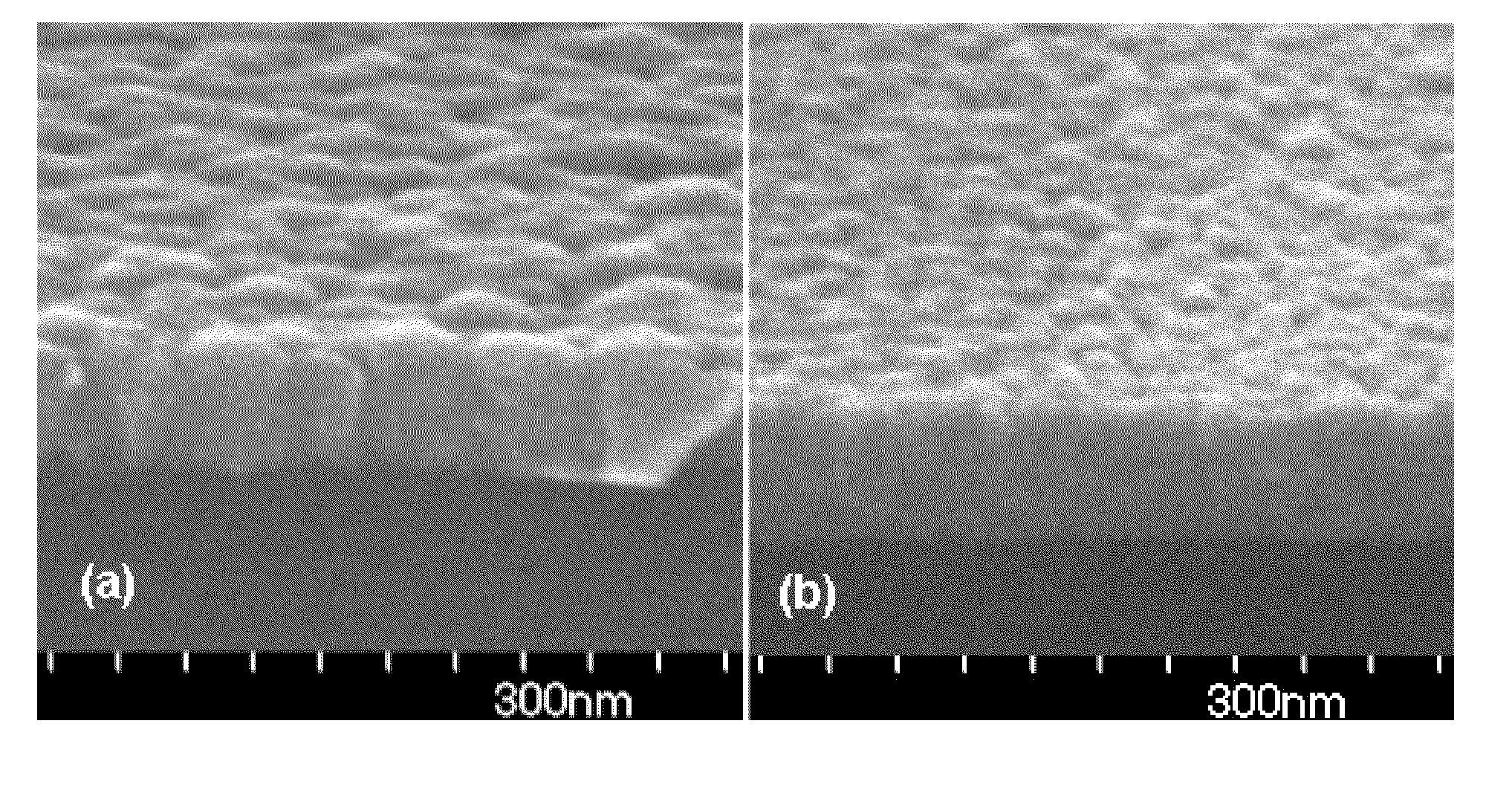

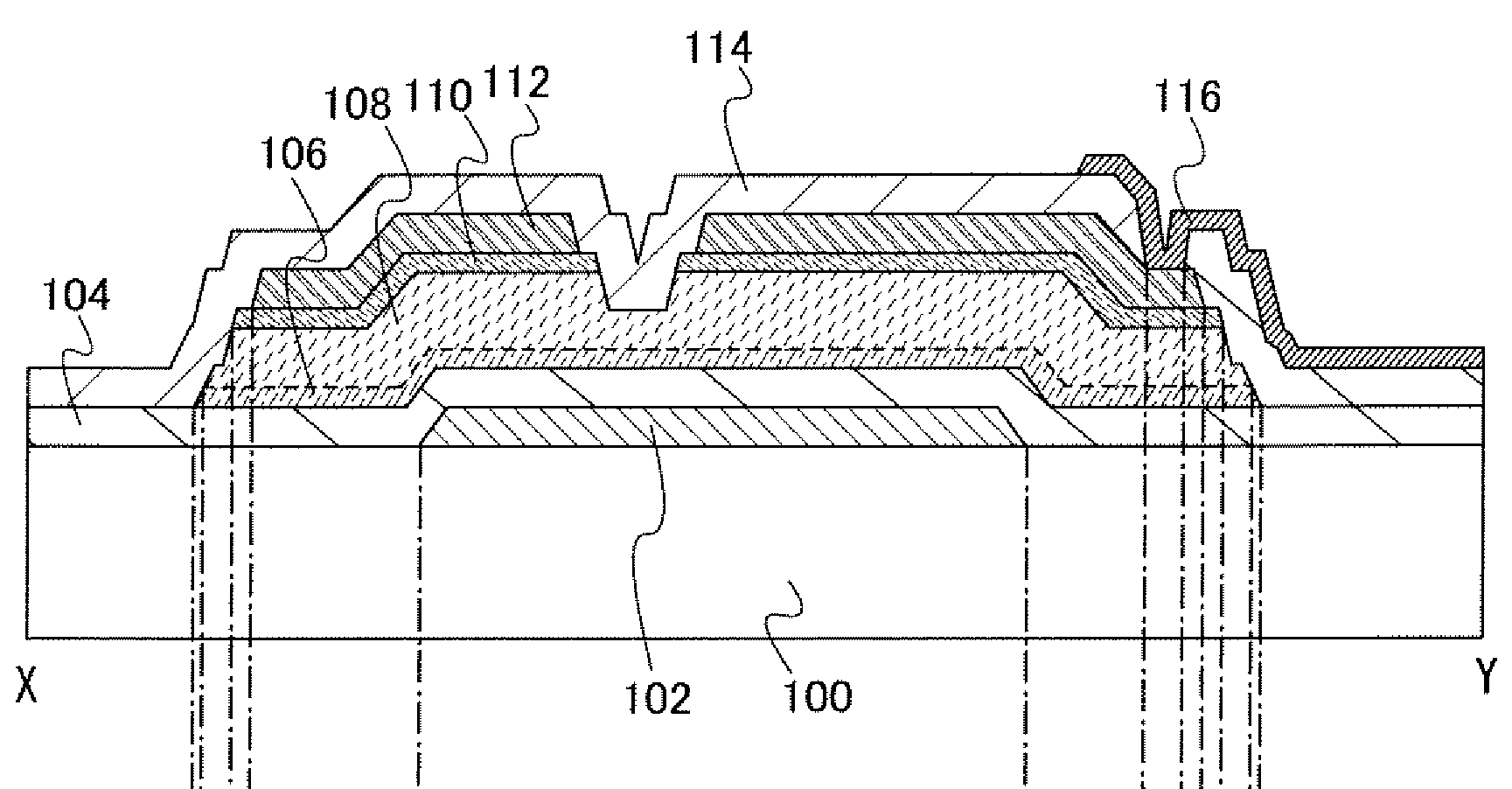

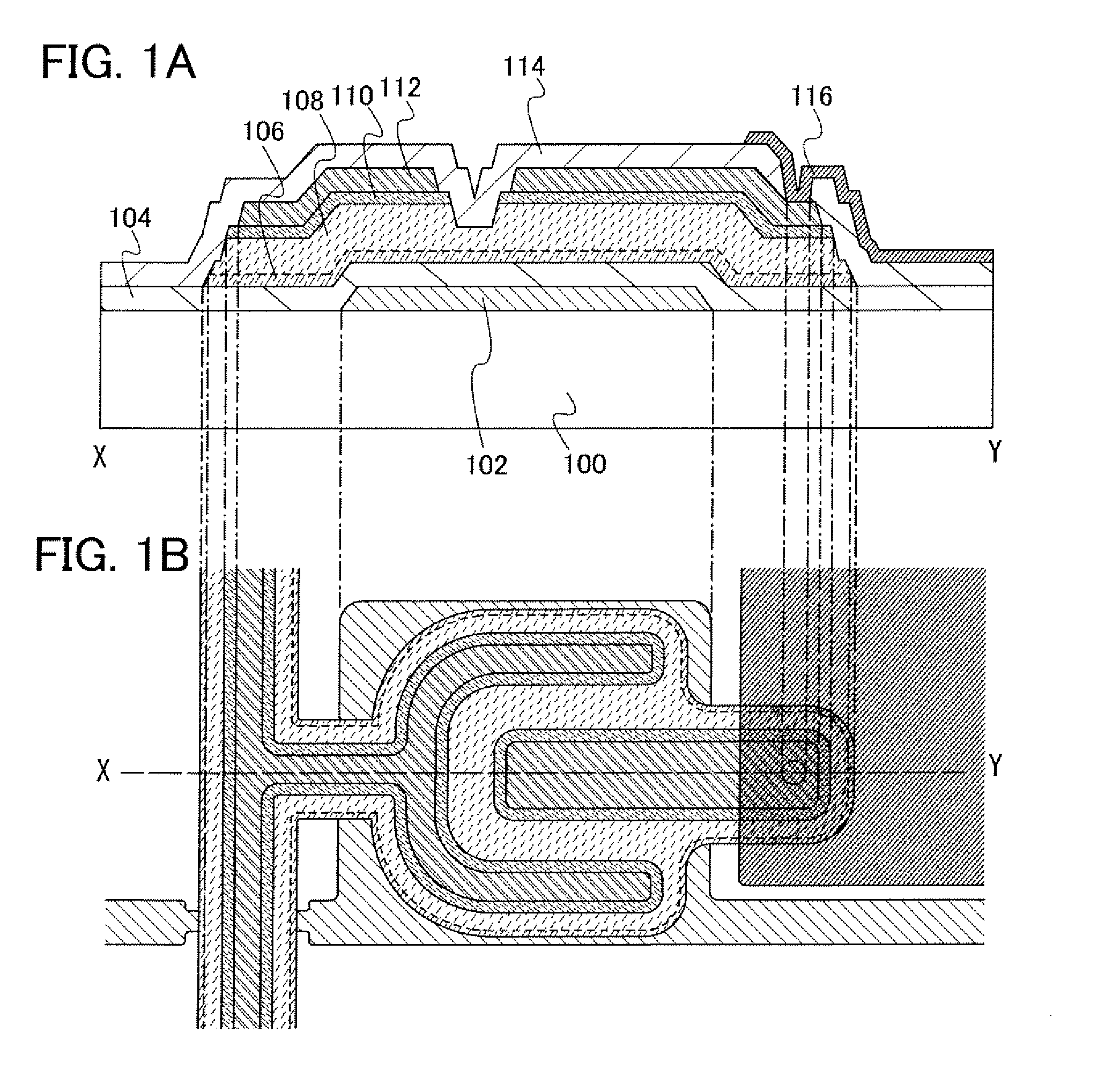

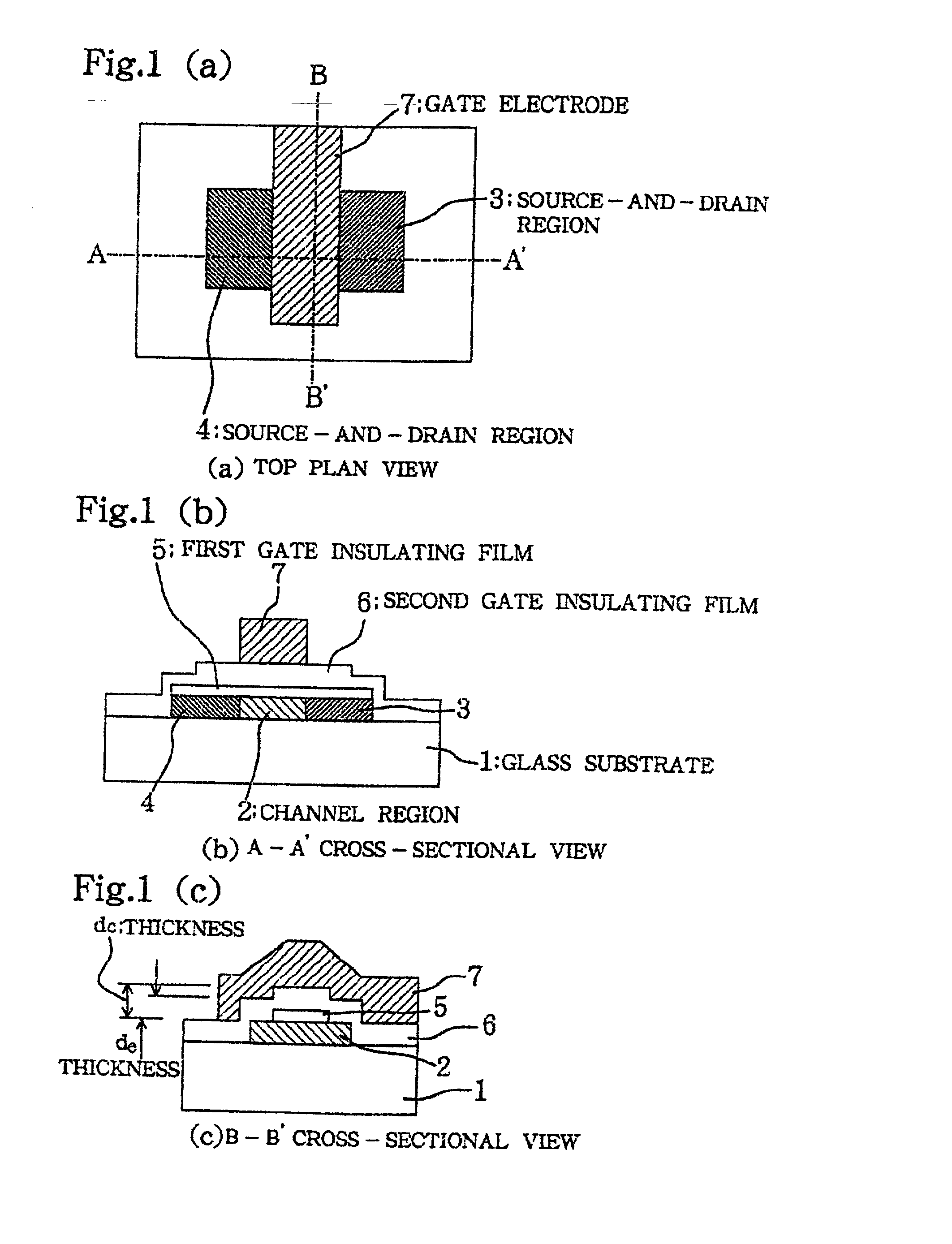

Thin film transistor and manufacturing method thereof

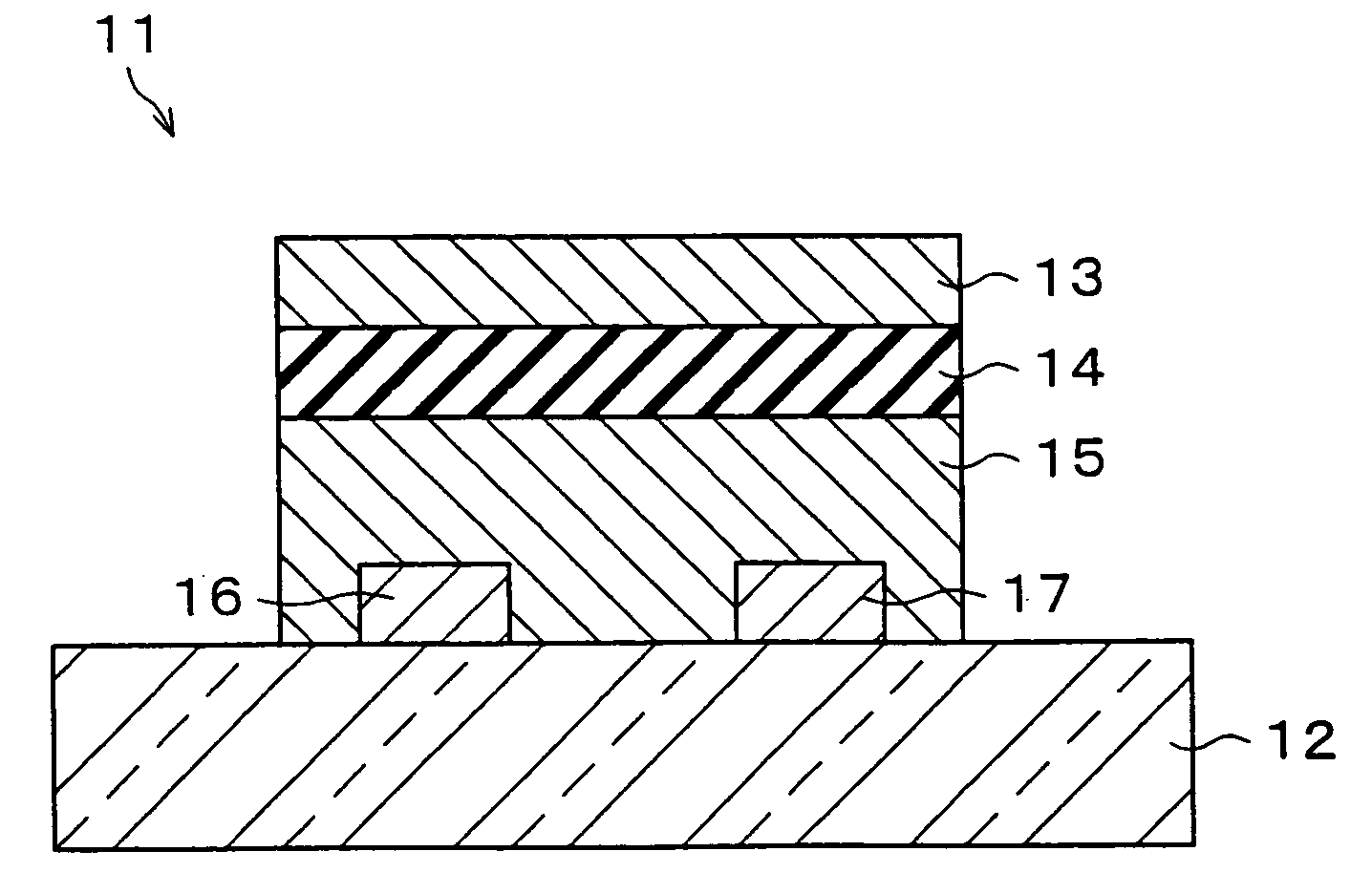

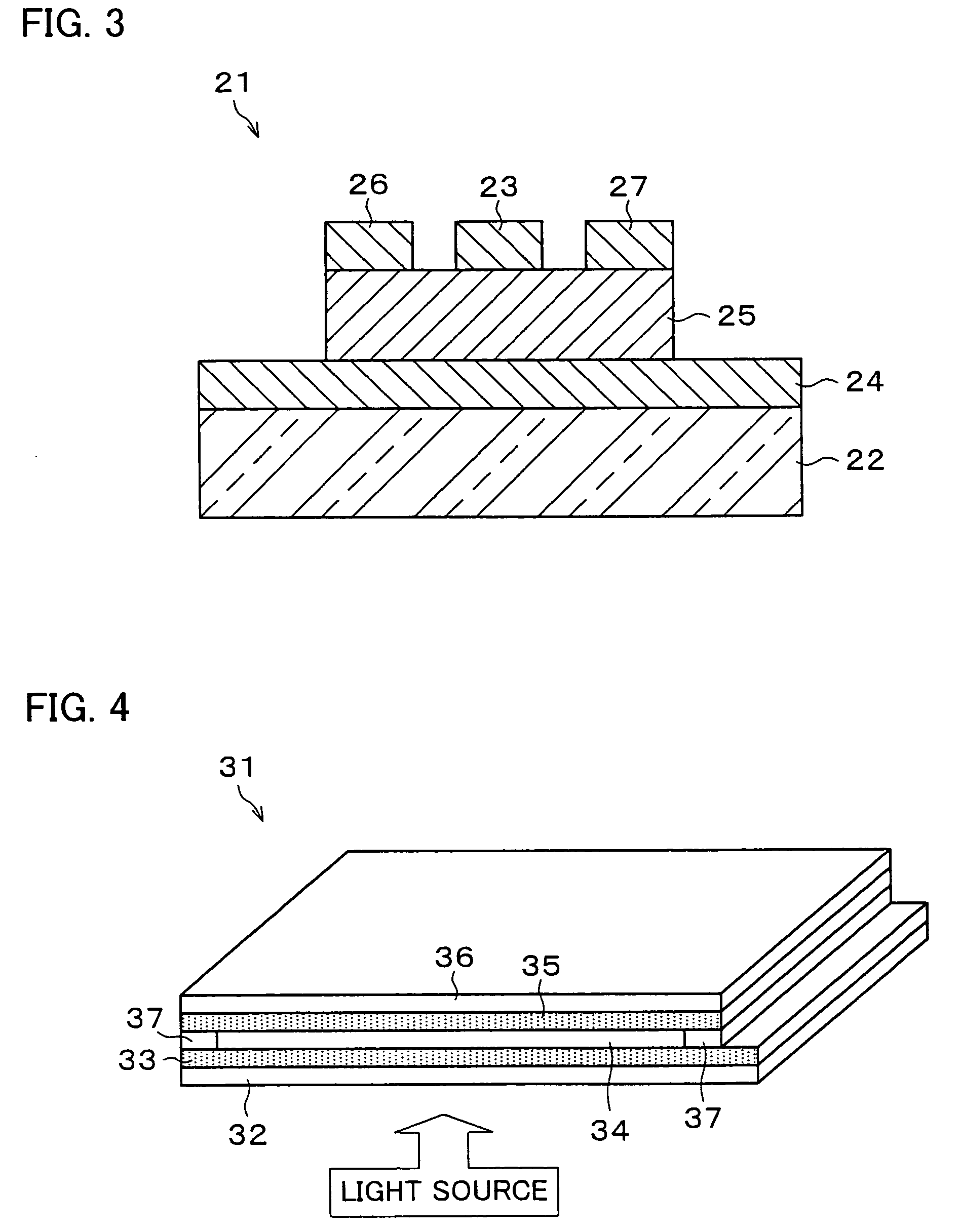

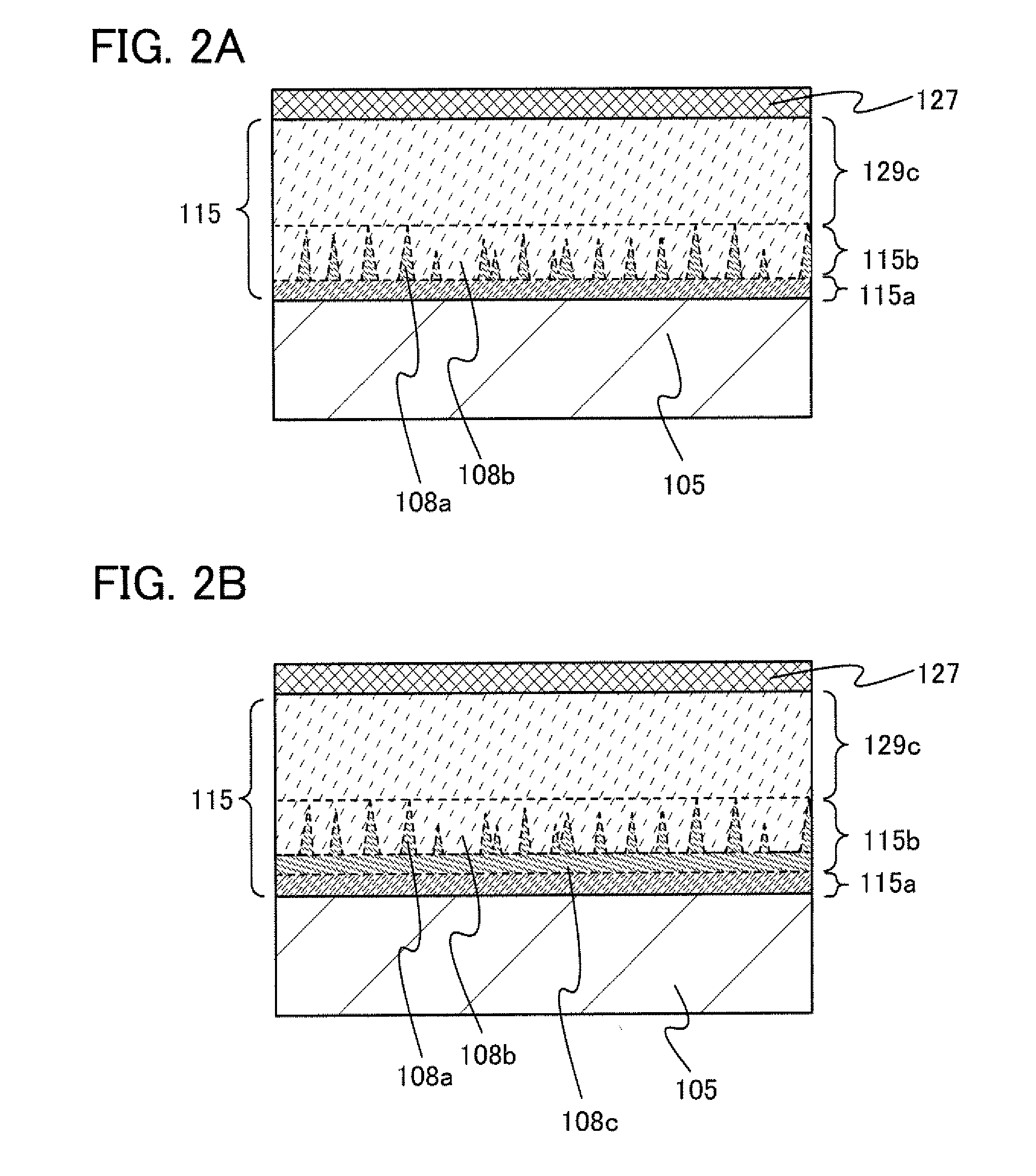

InactiveUS20110147754A1High currentLower average currentTransistorSolid-state devicesMicrocrystalline siliconImpurity

Disclosed is a thin film transistor including: a gate insulating layer covering a gate electrode; a microcrystalline semiconductor region over the gate insulating layer; a pair of amorphous semiconductor region over the microcrystalline semiconductor; a pair of impurity semiconductor layers over the amorphous semiconductor regions; and wirings over the impurity semiconductor layers. The microcrystalline semiconductor region has a surface having a projection and depression on the gate insulating layer side. The microcrystalline semiconductor region includes a first microcrystalline semiconductor region which is not covered with the amorphous regions and a second microcrystalline semiconductor region which is in contact with the amorphous semiconductor regions. A thickness d1 of the first microcrystalline semiconductor region is smaller than a thickness d2 of the second microcrystalline semiconductor region and d1 is greater than or equal to 30 nm.

Owner:SEMICON ENERGY LAB CO LTD

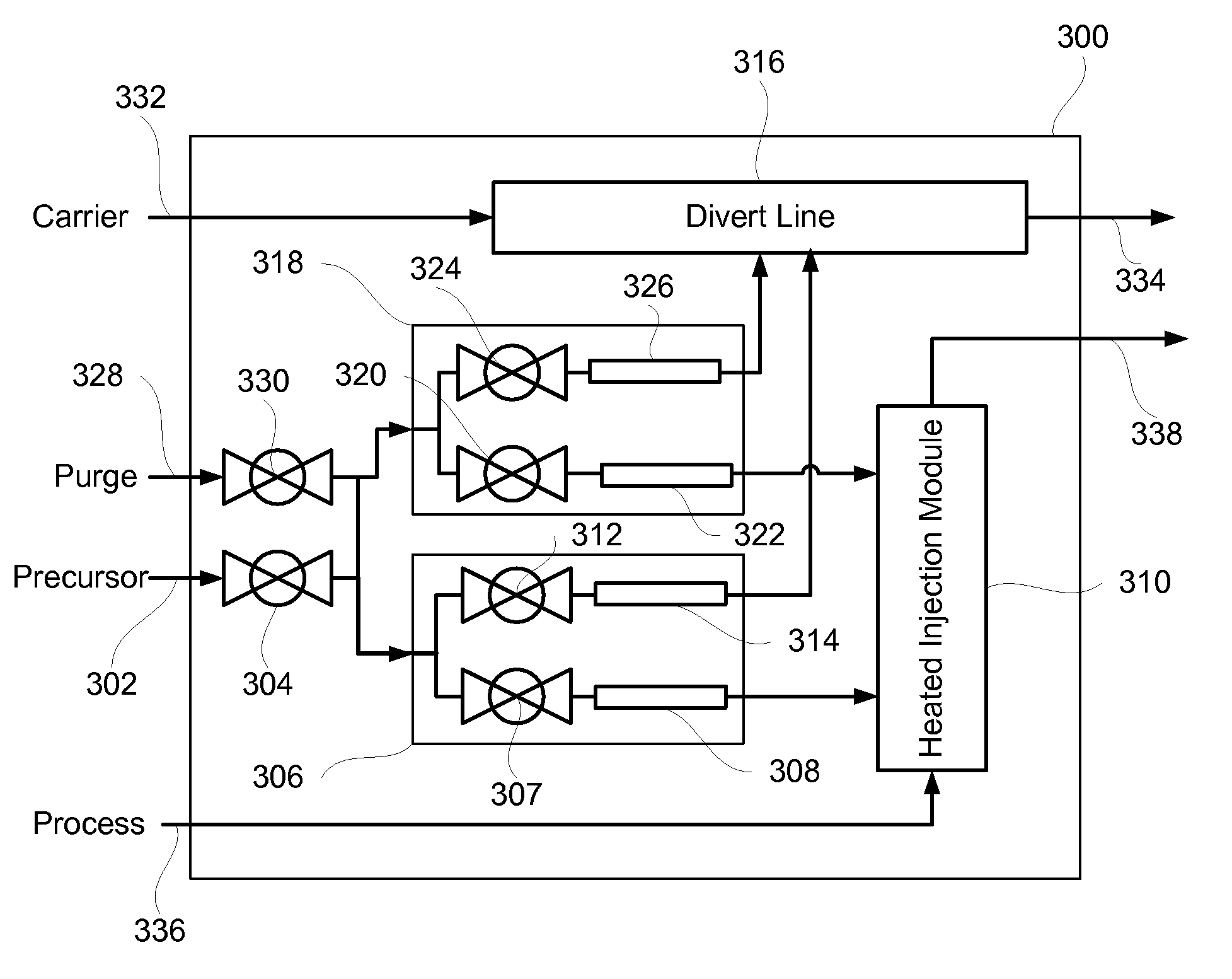

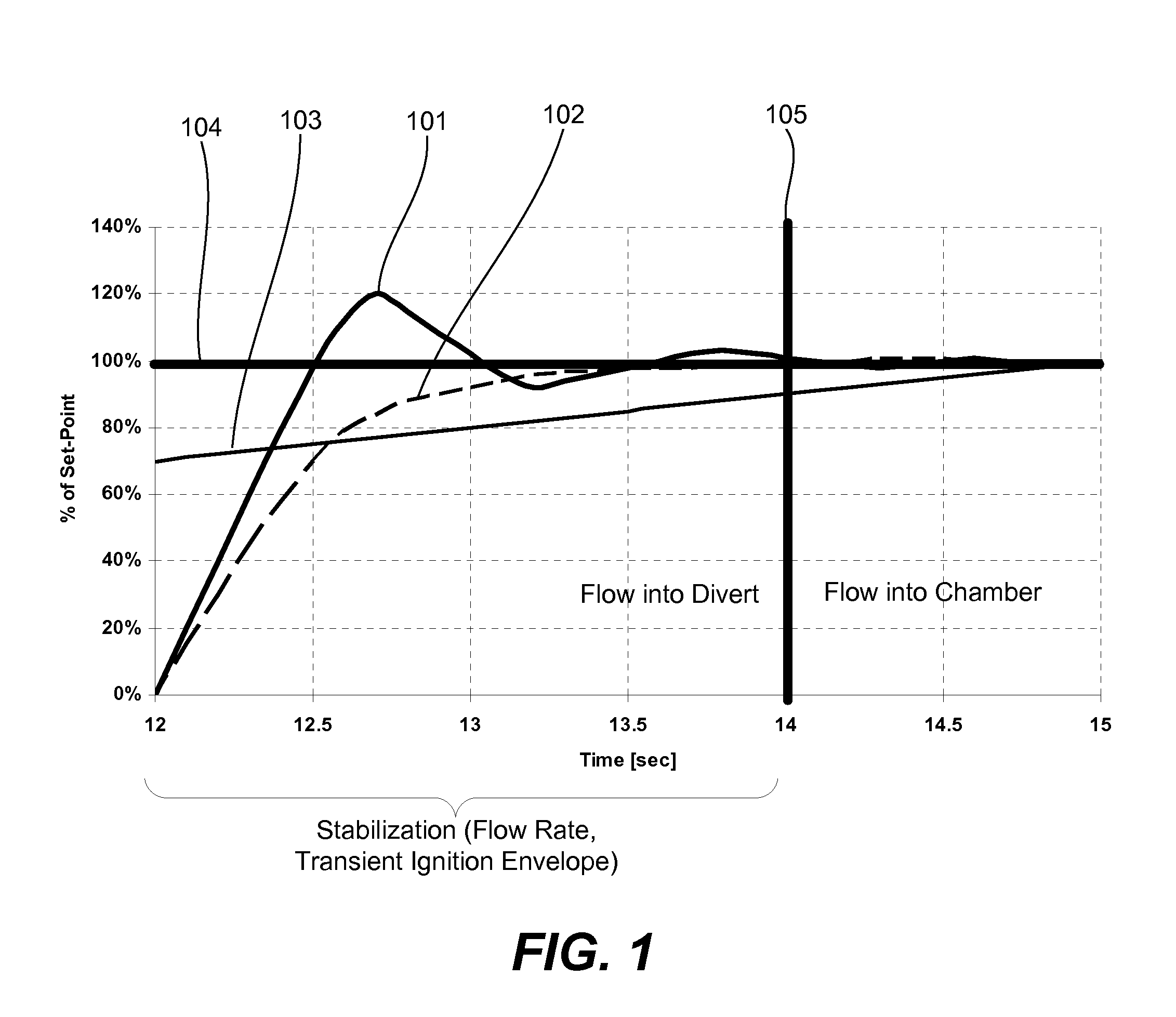

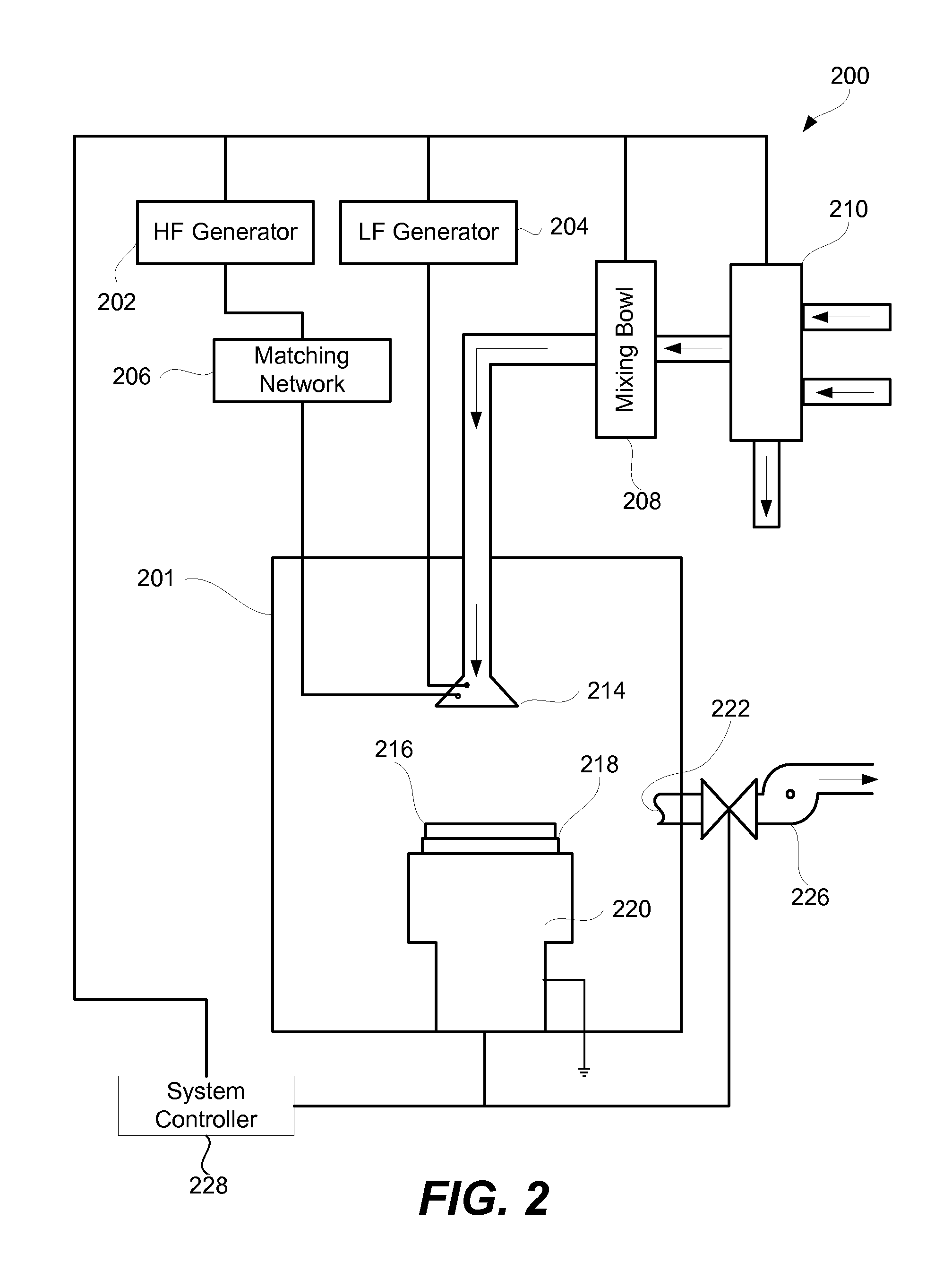

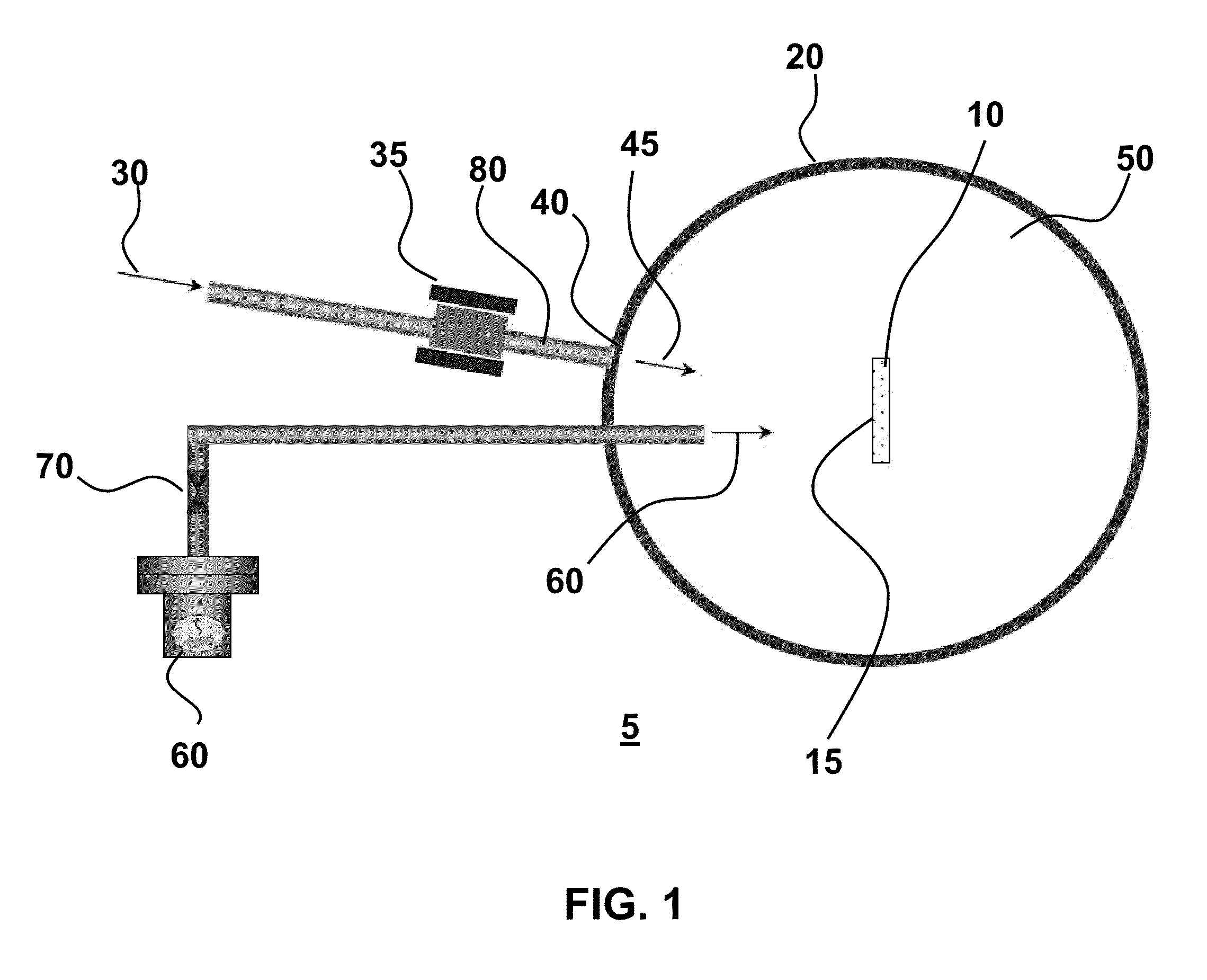

Method and apparatus to reduce defects in liquid based PECVD films

ActiveUS8017527B1Eliminate effectiveAvoid componentsFlow mixersSpace heating and ventilationLiquid basedChemistry

Apparatuses and methods for diverting a flow of a liquid precursor during flow stabilization and plasma stabilization stages during PECVD processes are effective at eliminating particle defects in PECVD films deposited using a liquid precursor.

Owner:NOVELLUS SYSTEMS

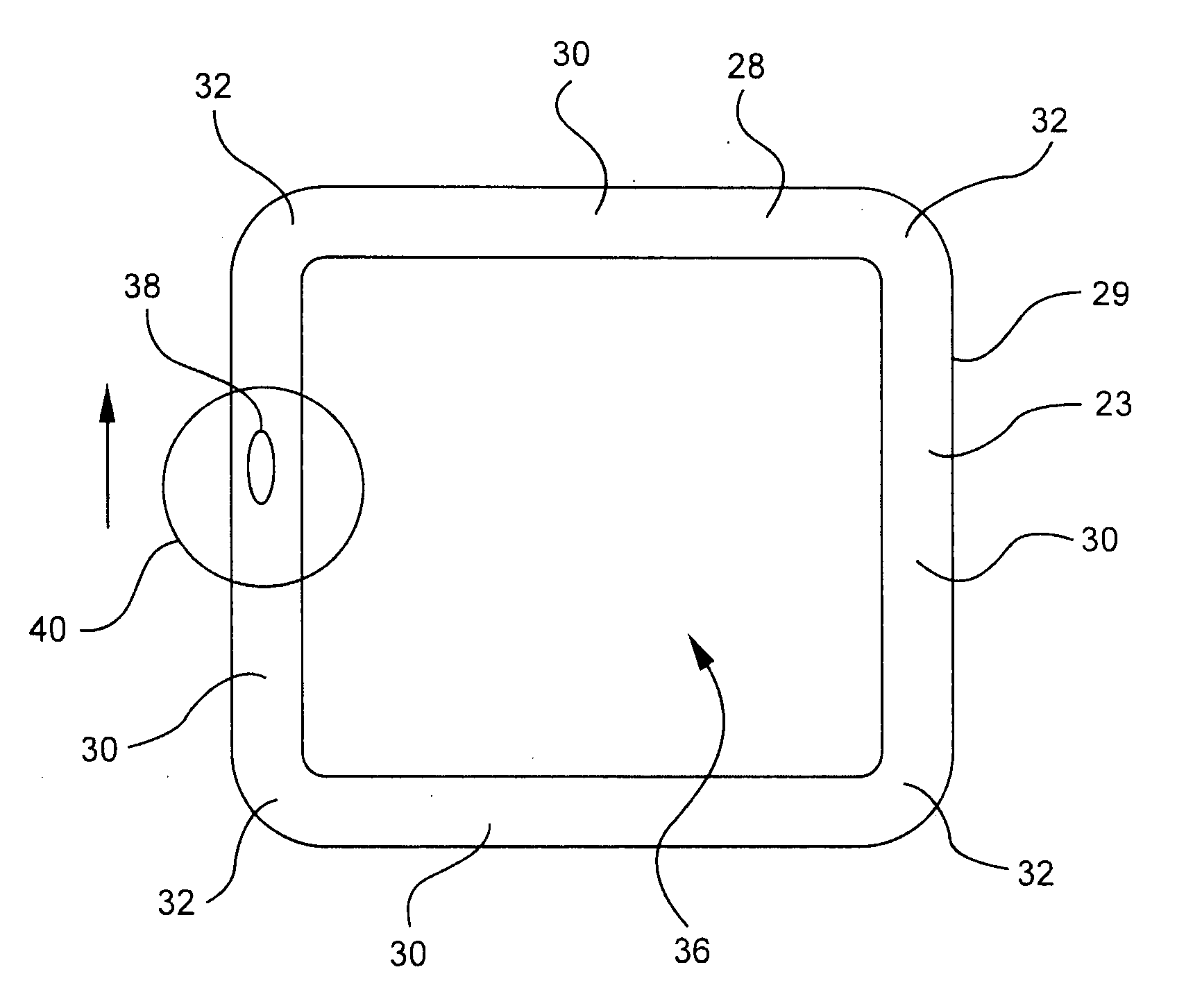

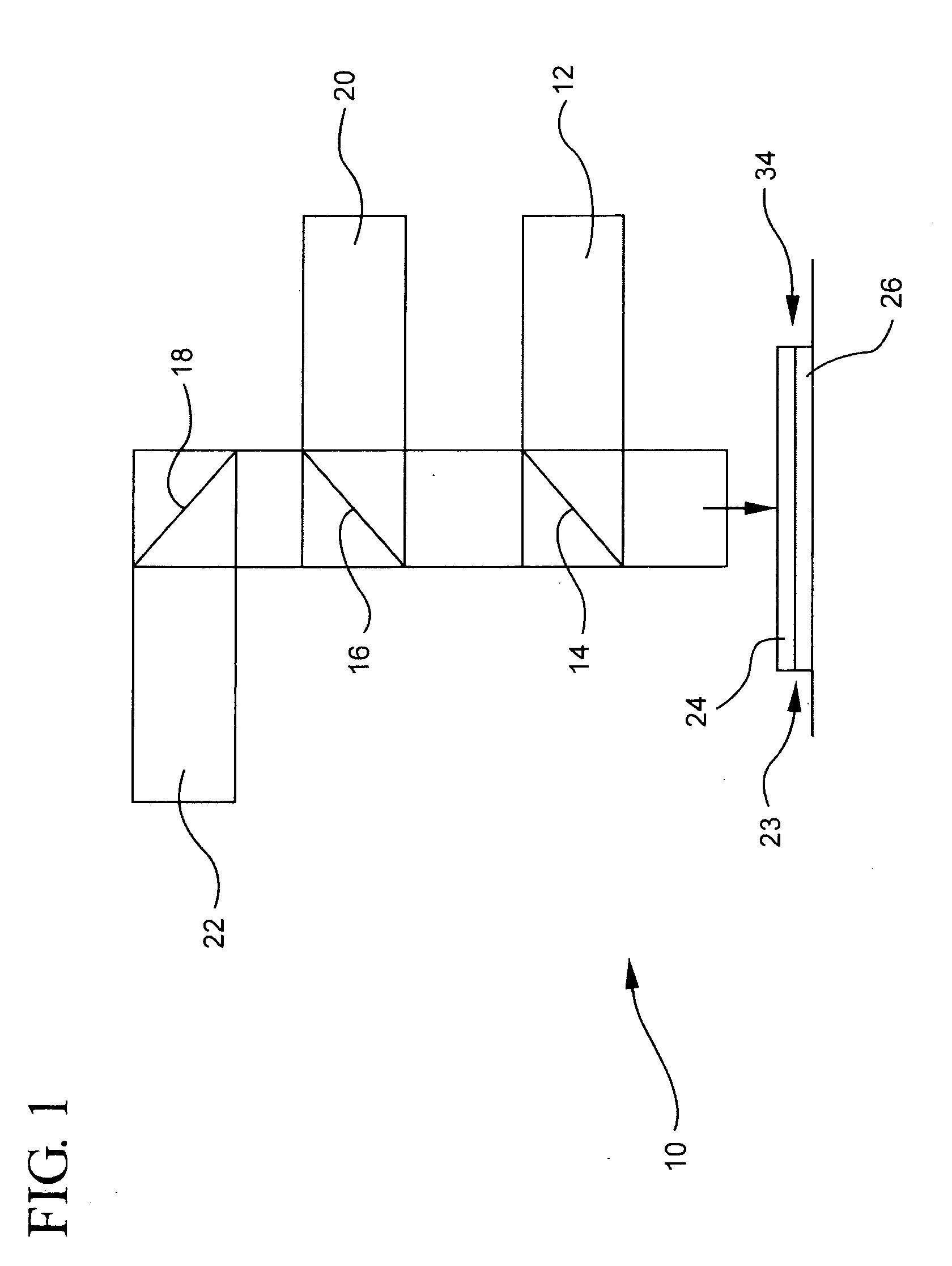

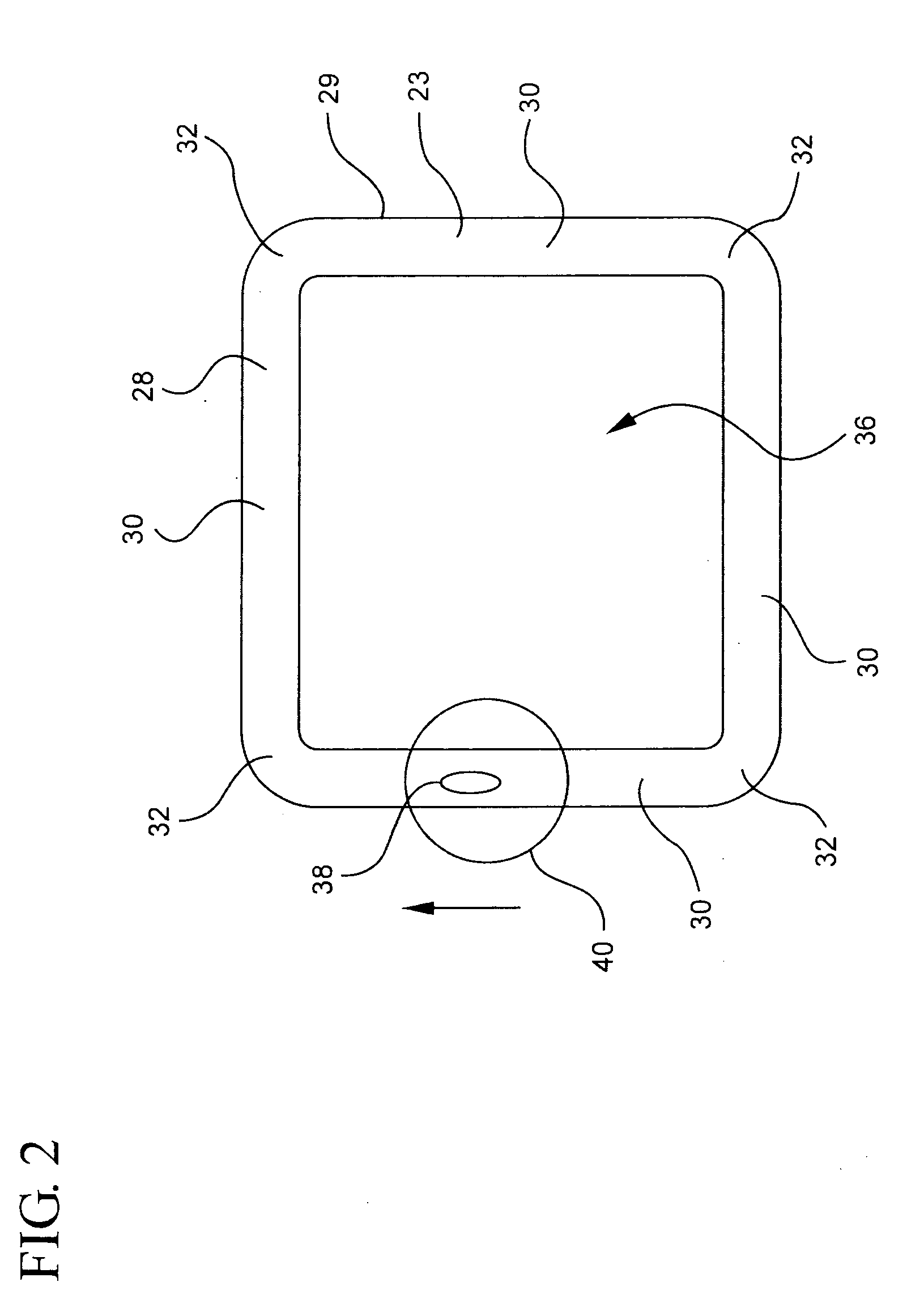

Quality control of the frit for OLED sealing

InactiveUS20100118912A1Quality improvementOptimize quantityMaterial thermal conductivitySolid-state devicesHermetic sealFrit

A method of finding defects in sealing material formed as a frame line on a glass plate includes irradiating the frame line of sealing material. A temperature of the irradiated sealing material is measured and a change of the temperature caused by a nonuniformity in sealing material is detected. Another aspect features a method of hermetically sealing a thin film device between glass plates. Sealing material is dispensed on a cover glass plate in the form of a frame line cell. The sealing material is pre-sintered onto the cover glass plate and cooled. A laser beam is moved around the frame line on the sealing material. A temperature of the sealing material contacted with the laser beam is measured. A change in the temperature (ΔT) caused by a nonuniformity in the sealing material is measured. Further aspects include a feedback process, infrared imaging and use of delta temperature data to increase sensitivity of temperature measurement data.

Owner:CORNING INC

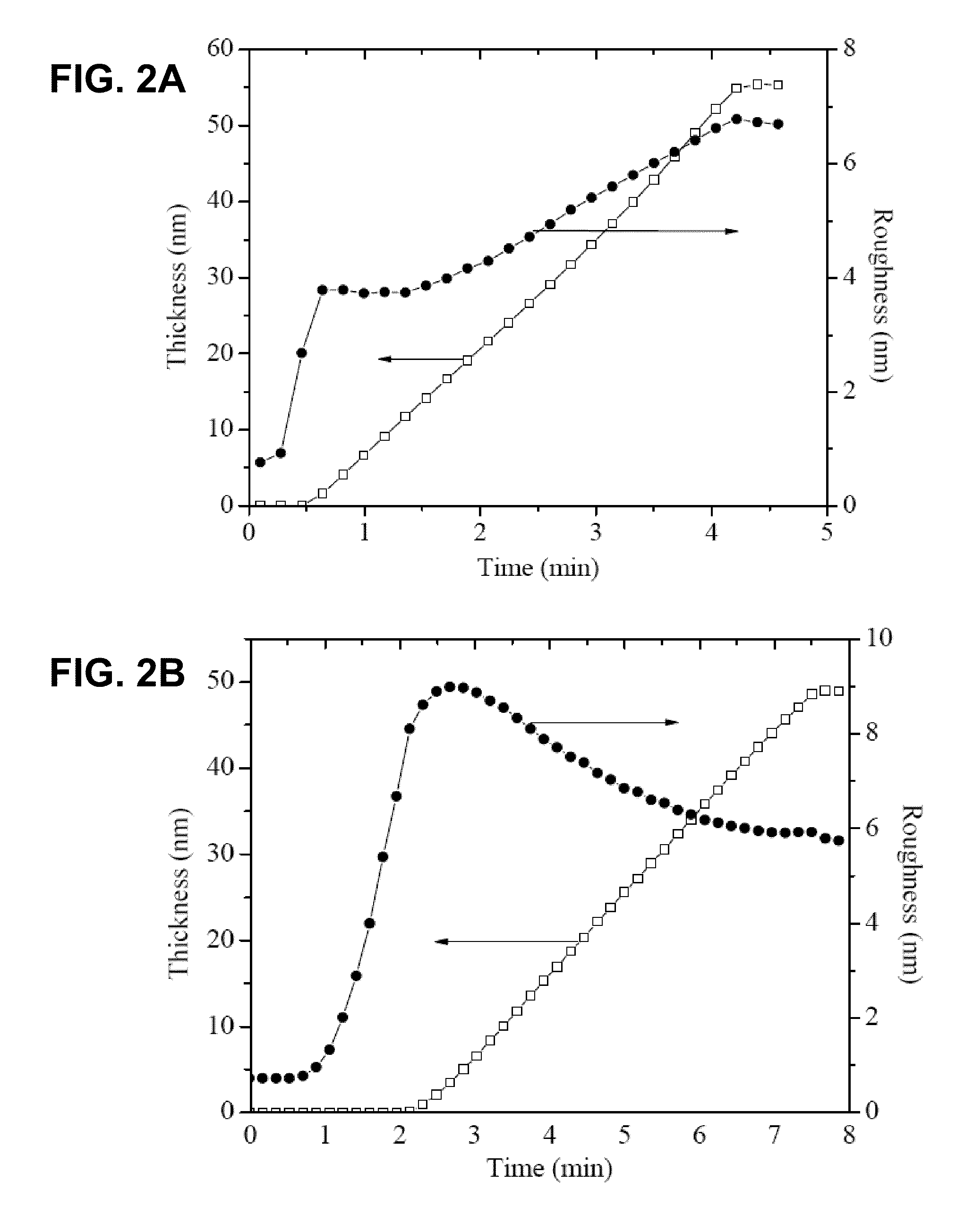

Surface preparation for thin film growth by enhanced nucleation

ActiveUS7943527B2Promote growthEnhanced nucleationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingRemote plasmaOptoelectronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

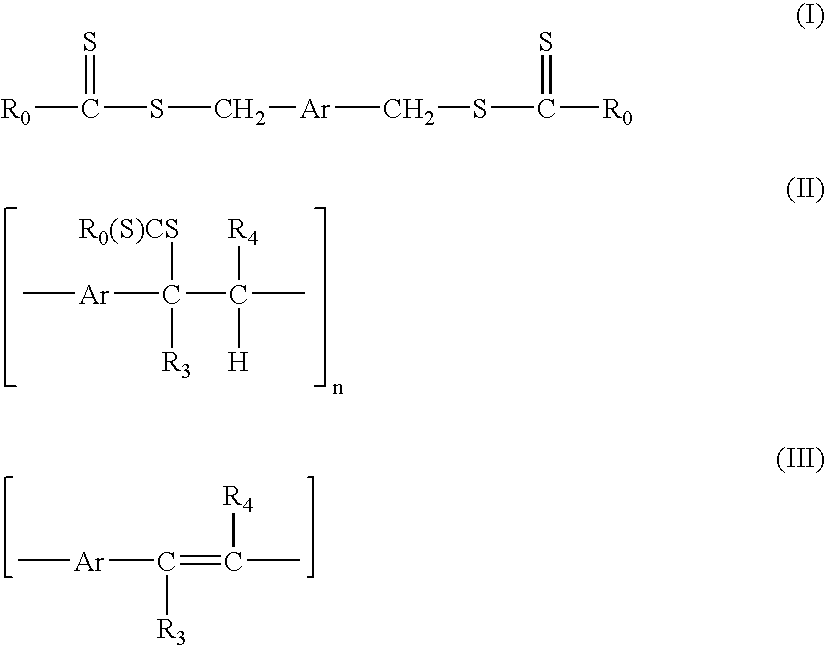

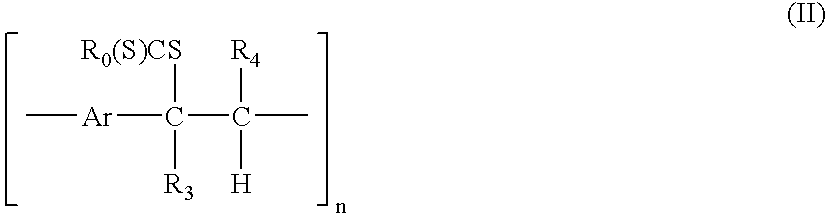

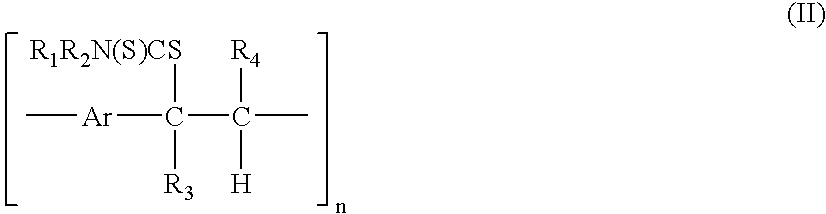

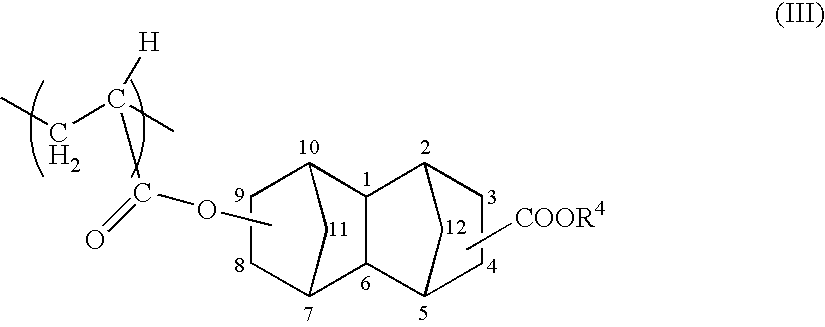

Method of preparing derivatives of polyarylene vinylene and method of preparing an electronic device including same

InactiveUS20050159581A1High yieldHigh molecular weightSolid-state devicesDomestic articlesPolymer scienceLeaving group

A technique is described for the preparation of polymers according to a process in which the starting compound of formula (I) is polymerized in the presence of a base in an organic solvent. No end chain controlling agents are required during the polymerisation to obtain soluble precursor polymers. The precursor polymer such obtained comprises structural units of the formula (II). In a next step, the precursor polymer (II) is subjected to a conversion reaction towards a soluble or insoluble conjugated polymer by thermal treatment. The arylene or heteroarylene polymer comprises structural units of the formula III. In this process the dithiocarbamate group acts as a leaving group and permits the formation of a precursor polymer of structural formula (II), which has an average molecular weight from 5000 to 1000000 Dalton and is soluble in common organic solvents. The precursor polymer with structural units of formula (II) is thermally converted to the conjugated polymer with structural formula (III).

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

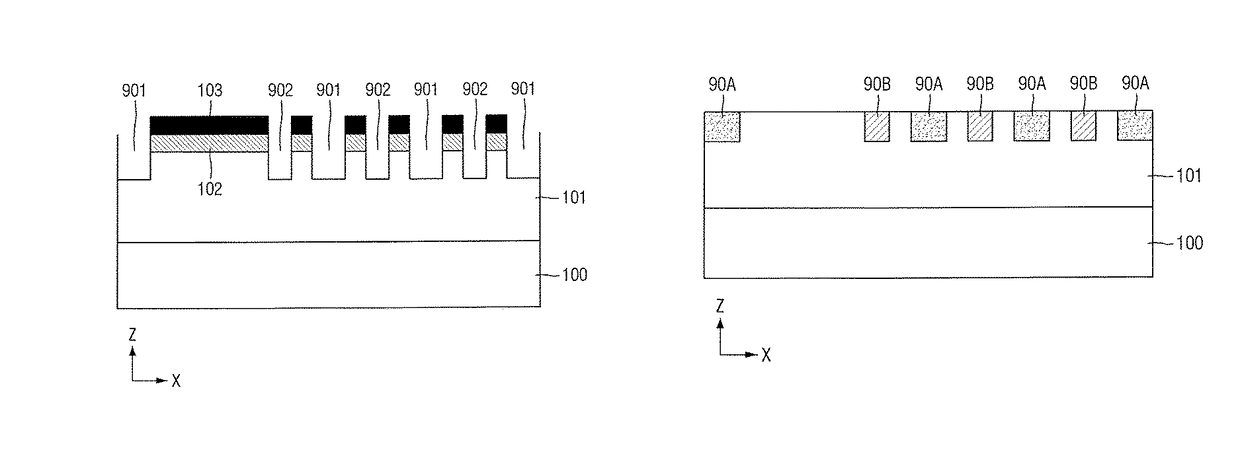

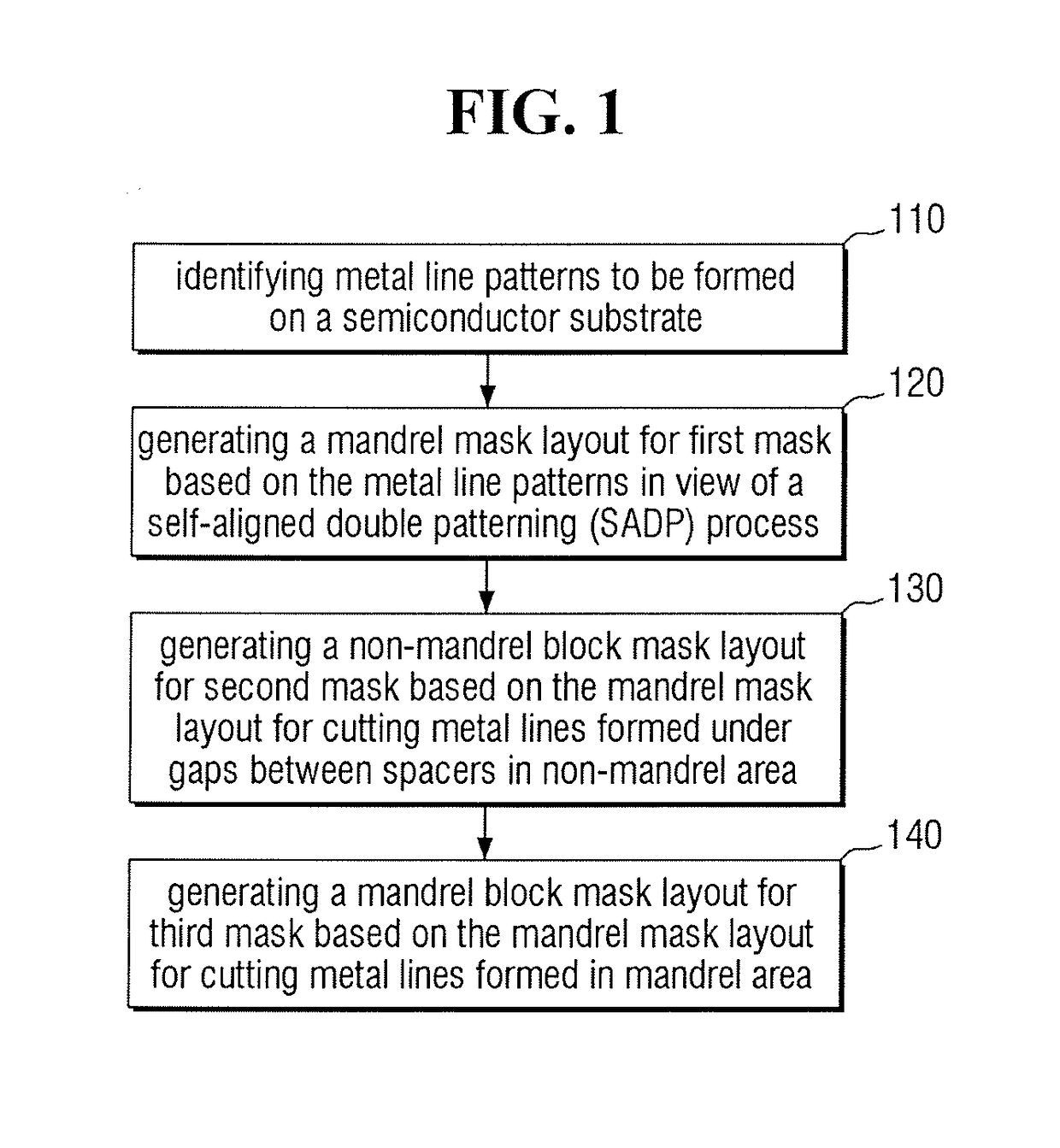

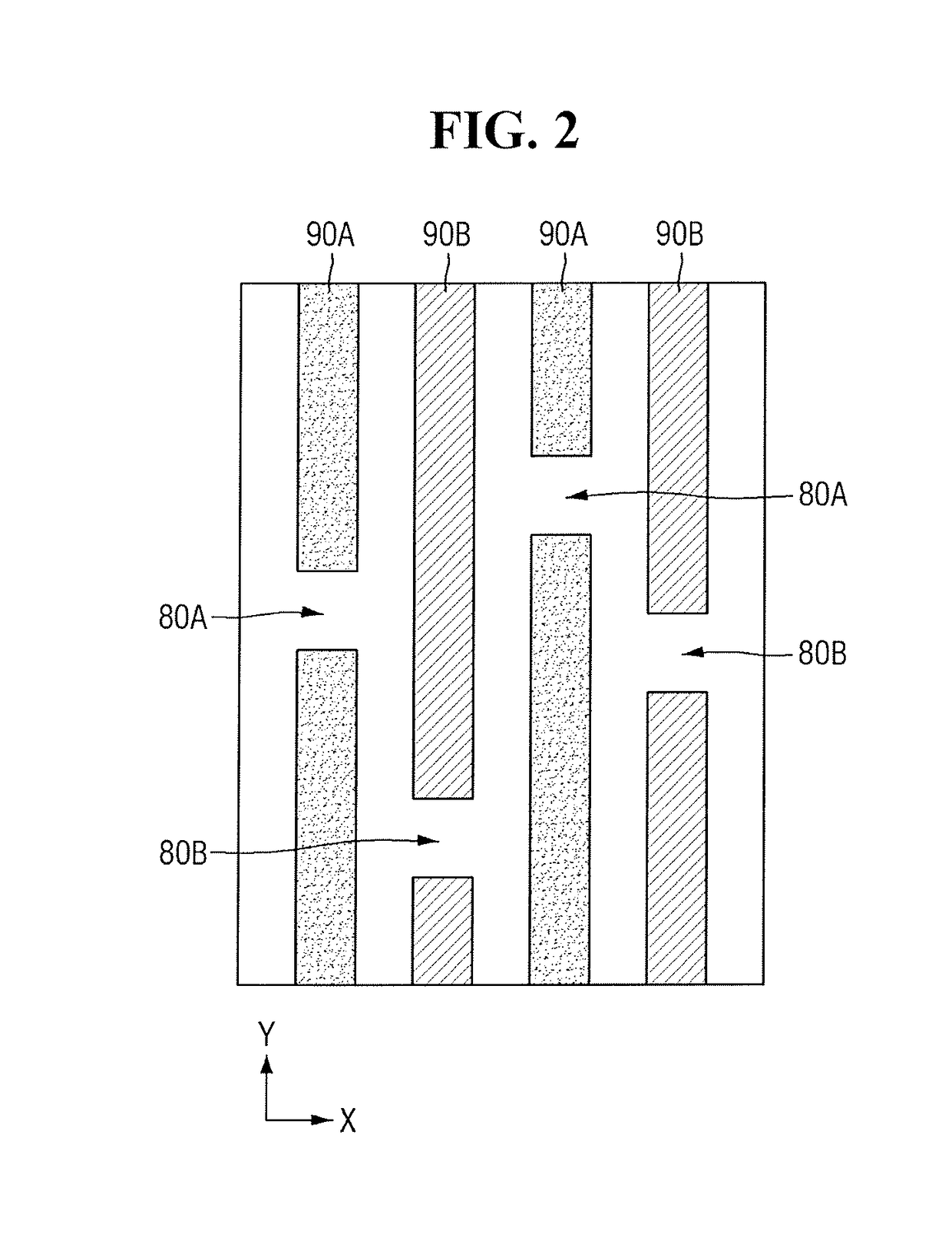

Self-aligned block patterning with density assist pattern

ActiveUS9941164B1Improve uniformityReduce defect levelSolid-state devicesPhotomechanical apparatusEngineeringSemiconductor

A method of generating mask layouts for self-aligned block patterning is provided. Metal line patterns to be formed on a semiconductor substrate is identified. A mandrel mask layout for first mask based on the metal line patterns is generated in view of a self-aligned double patterning (SADP) process for forming a plurality of mandrels on the semiconductor substrate. The mandrel mask layout may include a plurality of mandrel patterns. A non-mandrel block mask layout for second mask is generated based on the mandrel mask layout for cutting metal lines formed under gaps between spacers in non-mandrel area on the semiconductor substrate. The non-mandrel block mask layout may include a plurality of first block patterns and a plurality of first density assist patterns. A mandrel block mask layout for third mask is generated based on the mandrel mask layout for cutting metal lines formed under mandrel area on the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

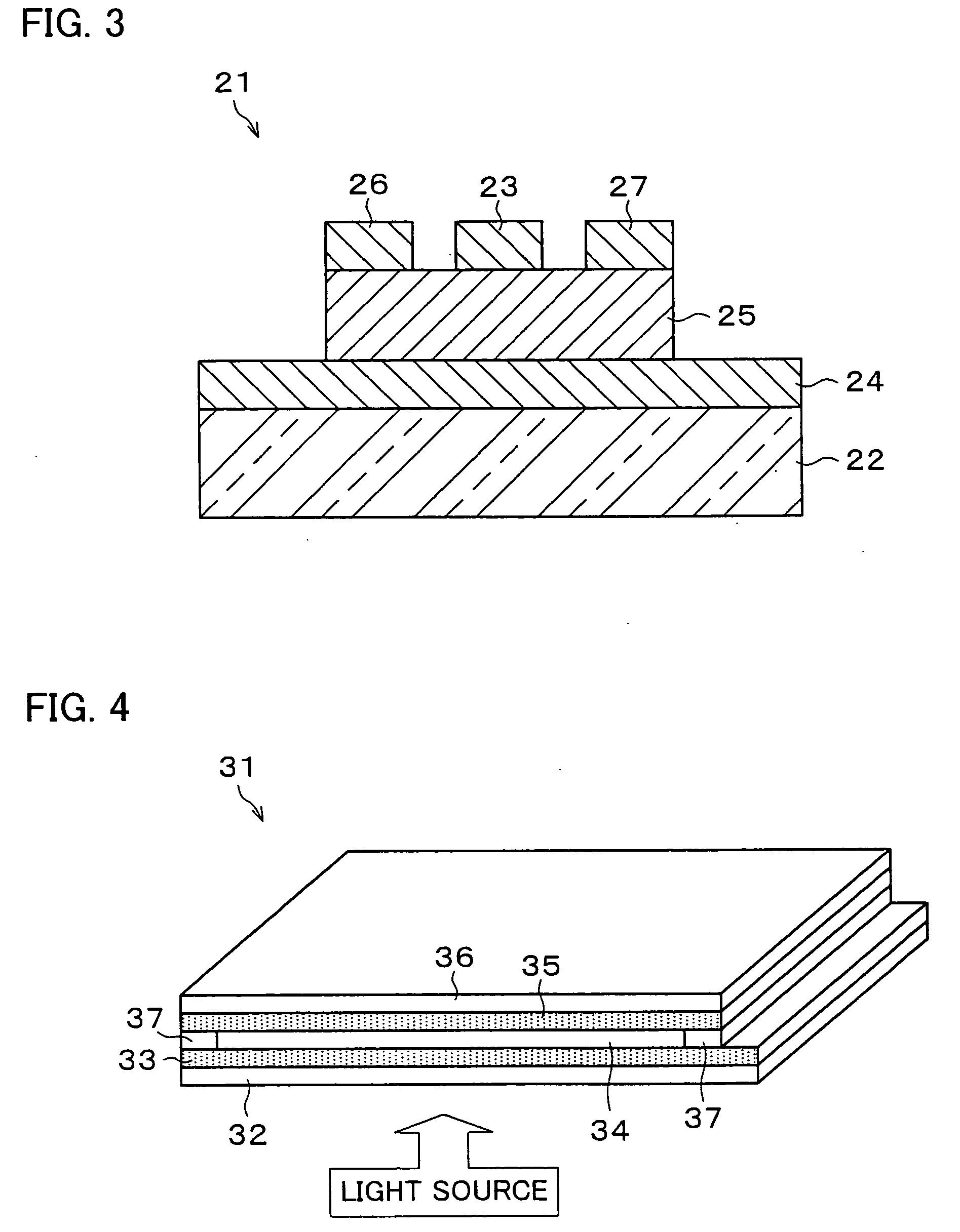

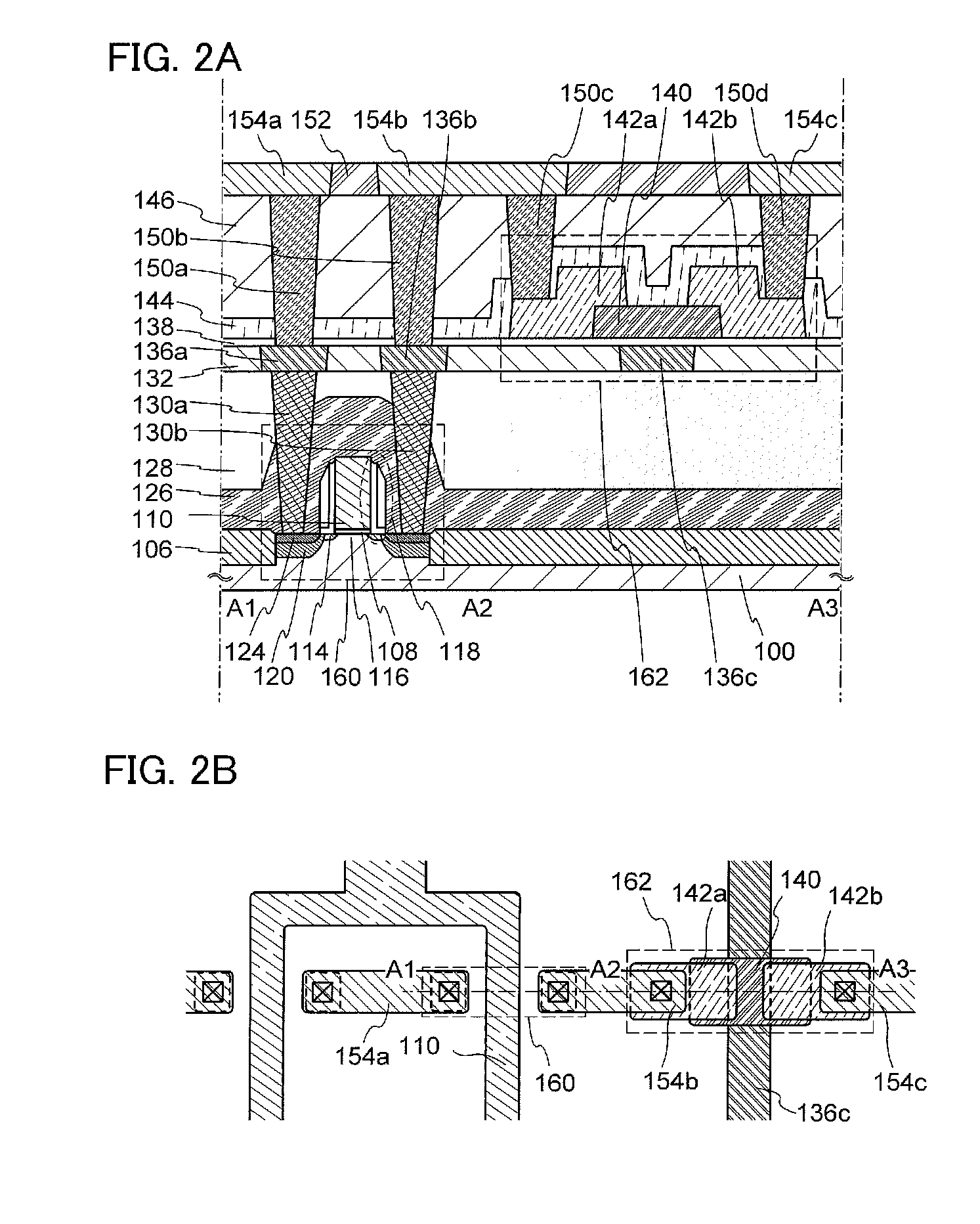

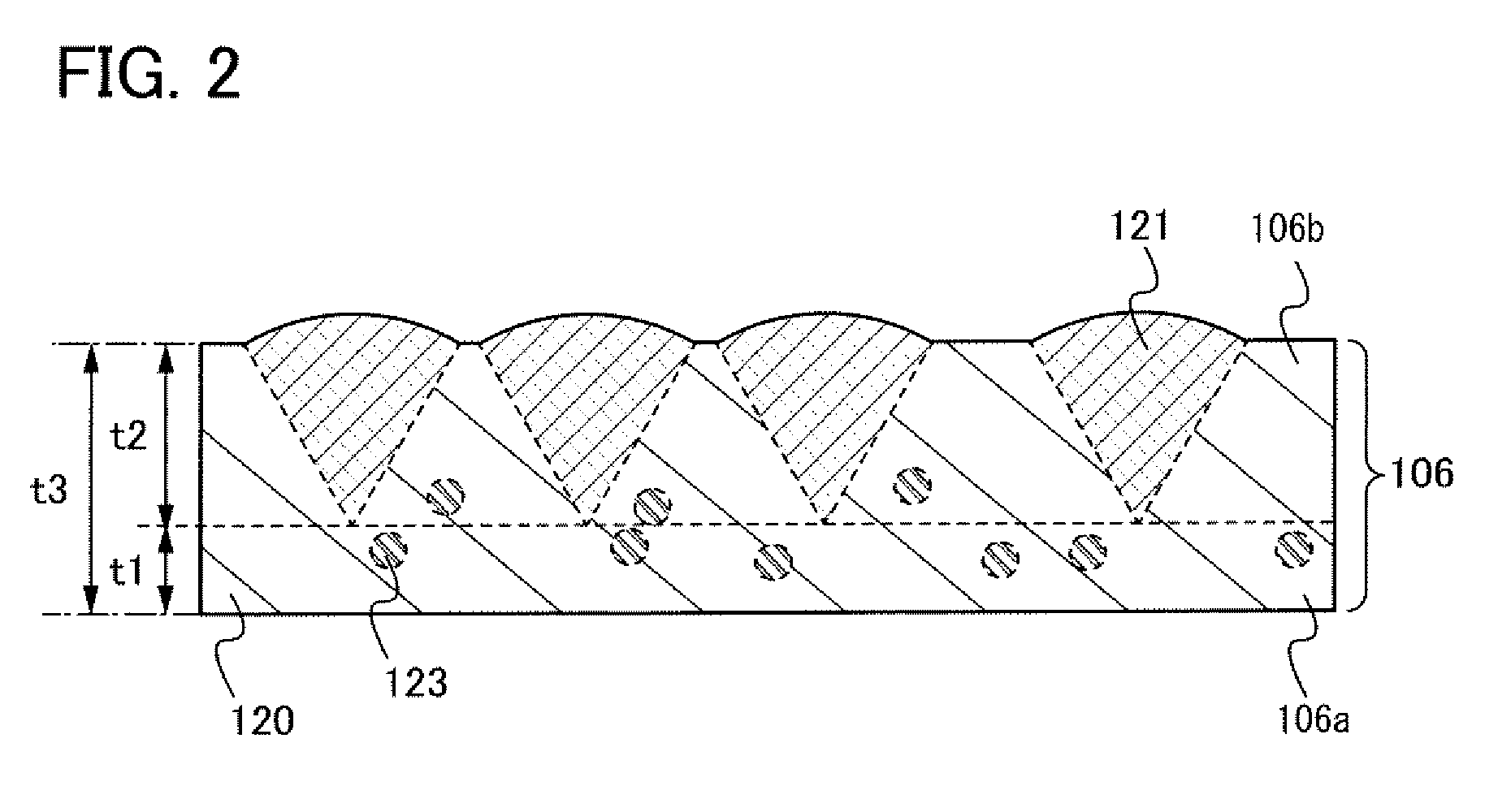

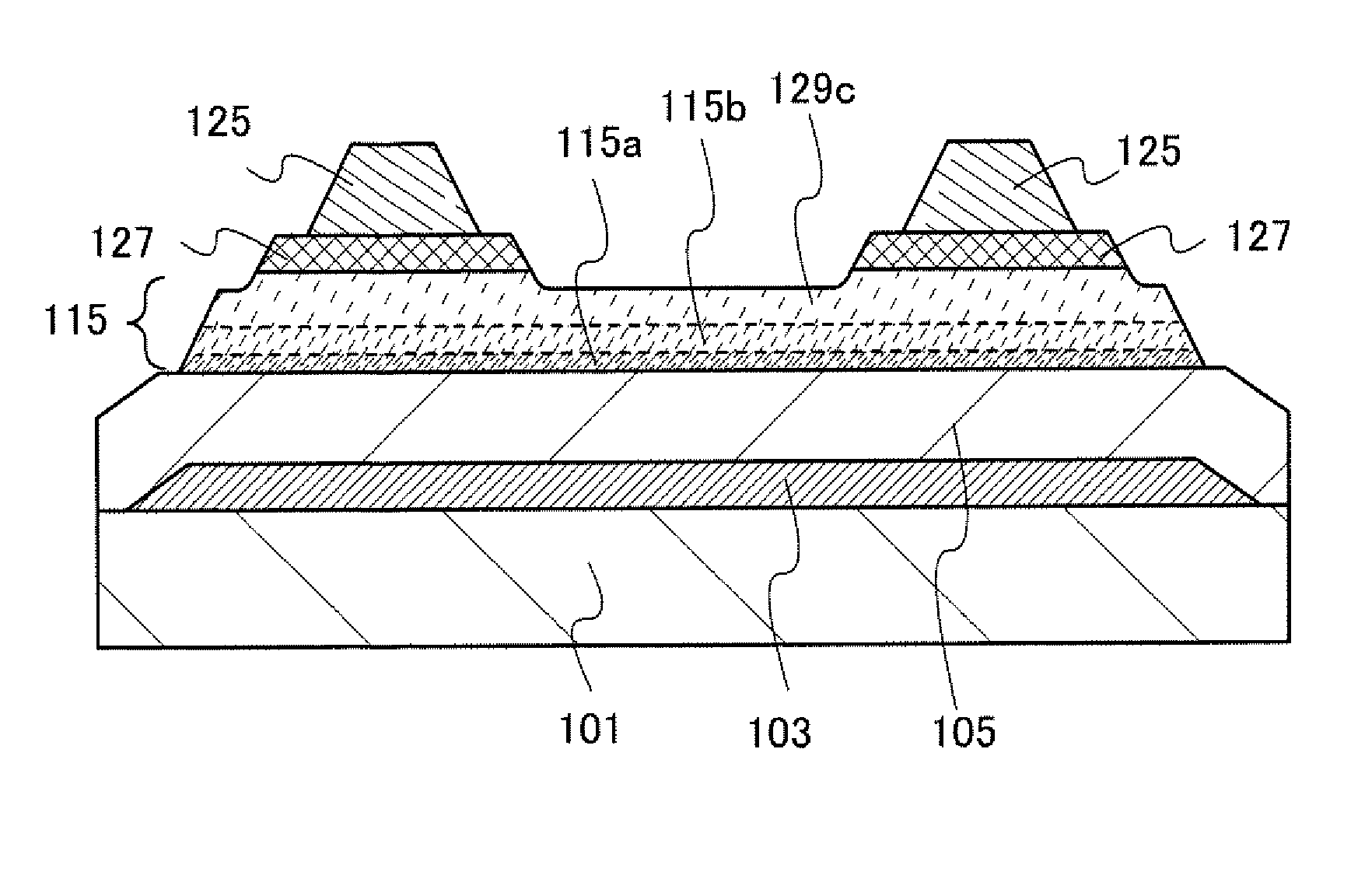

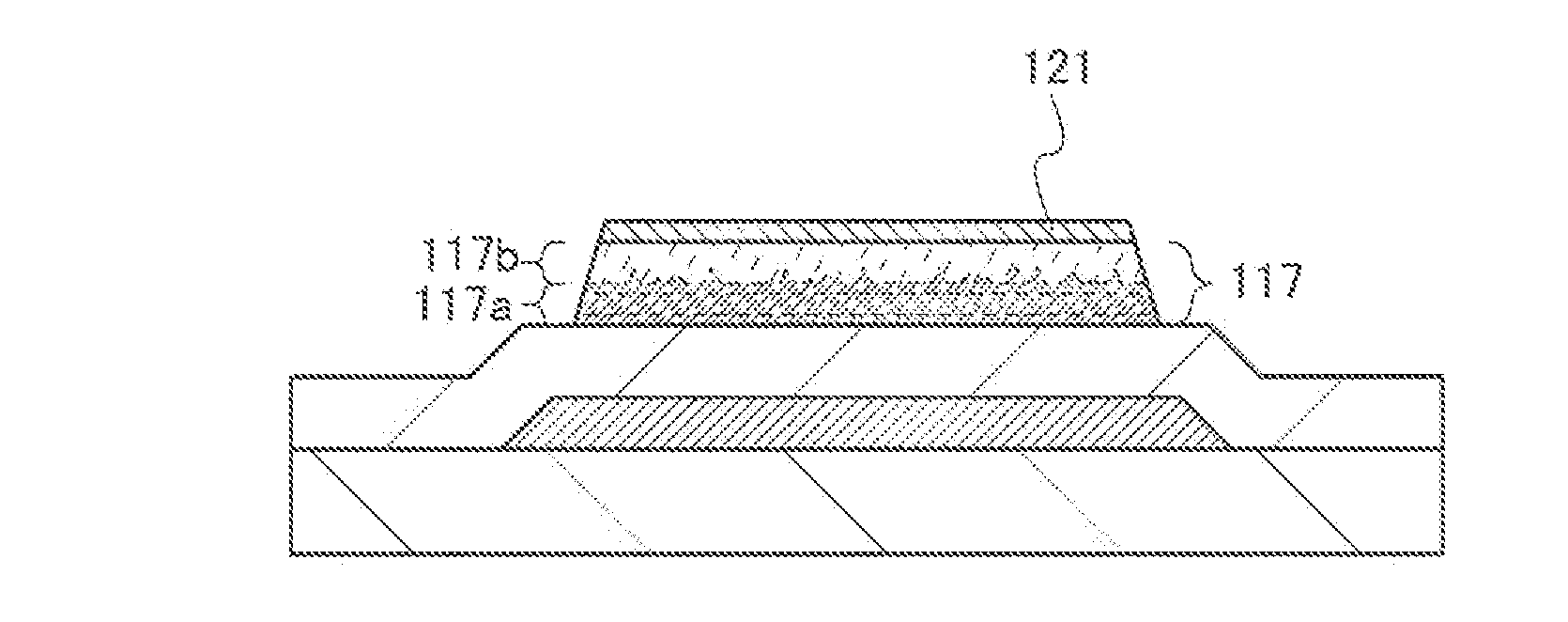

Thin film transistor

InactiveUS20090267068A1Reduce defect levelIncrease currentTransistorElectric discharge tubesSemiconductor packageImpurity

The thin film transistor includes a gate insulating layer covering a gate electrode, over a substrate having an insulating surface; a semiconductor layer forming a channel formation region, in which a plurality of crystal regions is included in an amorphous structure; an impurity semiconductor layer imparting one conductivity type which forms a source region and a drain region; and a buffer layer formed from an amorphous semiconductor, which is located between the semiconductor layer and the impurity semiconductor layer. The thin film transistor includes the crystal region which includes minute crystal grains and inverted conical or inverted pyramidal grain each of which grows approximately radially from a position away from an interface between the gate insulating layer and the semiconductor layer toward a direction in which the semiconductor layer is deposited in a region which does not reach the impurity semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

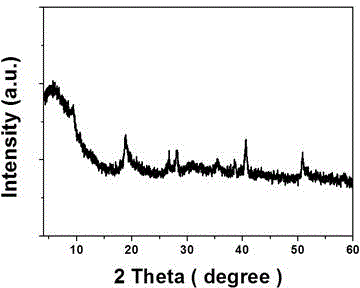

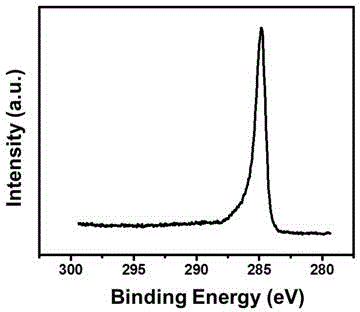

Graphene material and preparation method of electrode material of graphene material

ActiveCN104876213ASolve difficult preparationFix stability issuesCell electrodesPorous grapheneHeat conducting

The invention relates to a halide intercalated porous graphene material. The halide intercalated porous graphene material contains porous graphene sheets and a halide; the halide is intercalated between the porous graphene sheets; the particles of the halide are evenly spread between the porous graphene sheets at one single layer. The preparation method of the halide intercalated porous graphene material comprises the steps of taking a halide intercalated graphite compound as the raw materials and performing ultrasonic stripping on the raw material in a solvent to prepare the halide intercalated porous graphene material. The method is simple; the raw material is cheap and the equipment is easy to obtain; the production cost of the graphene is greatly reduced; in short, the method can be widely applied to the field of preparation of lithium-ion reversible battery electrode materials, energy source materials, conductive materials, heat-conducting materials and the like.

Owner:BEIJING UNIV OF CHEM TECH

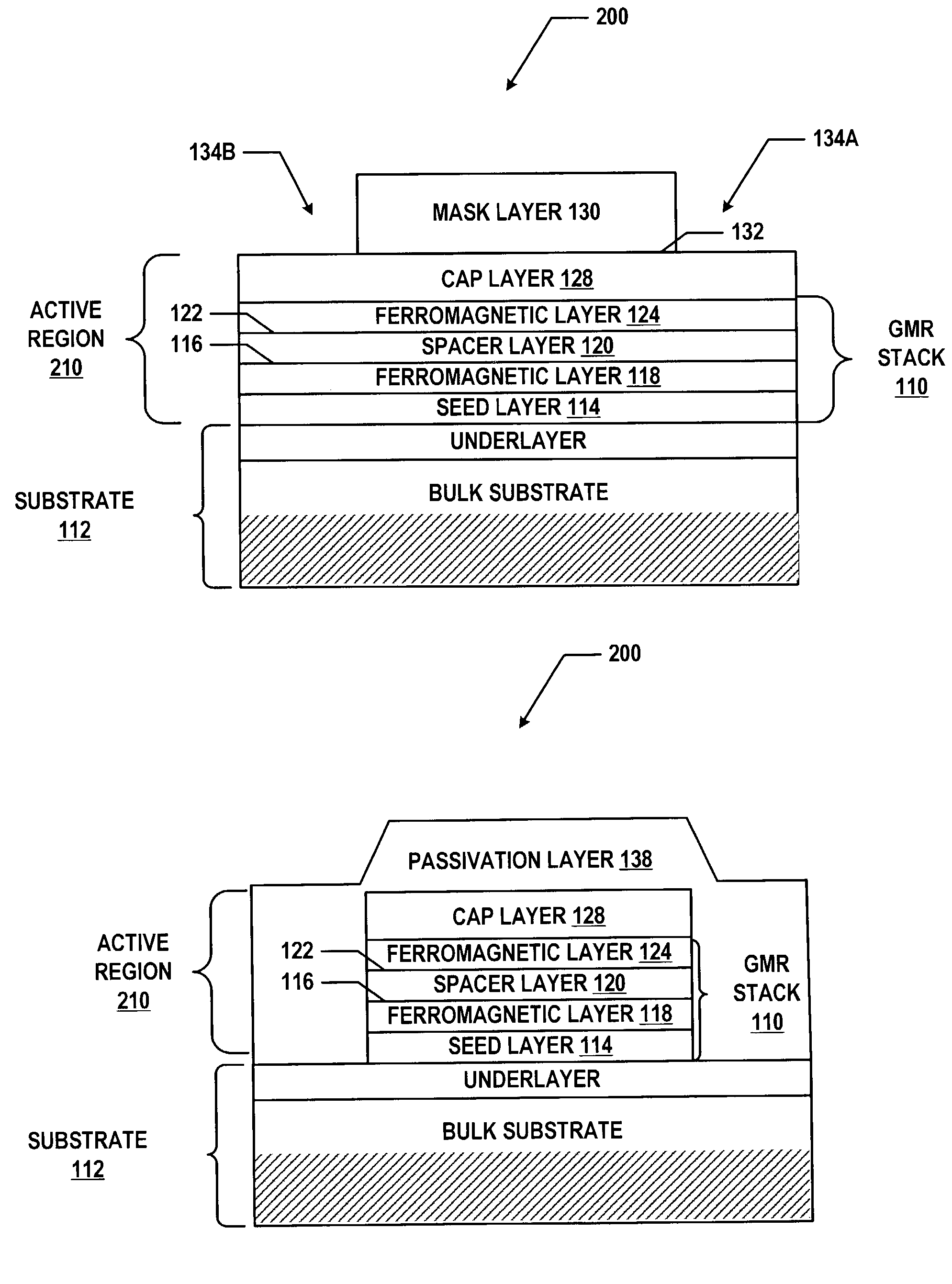

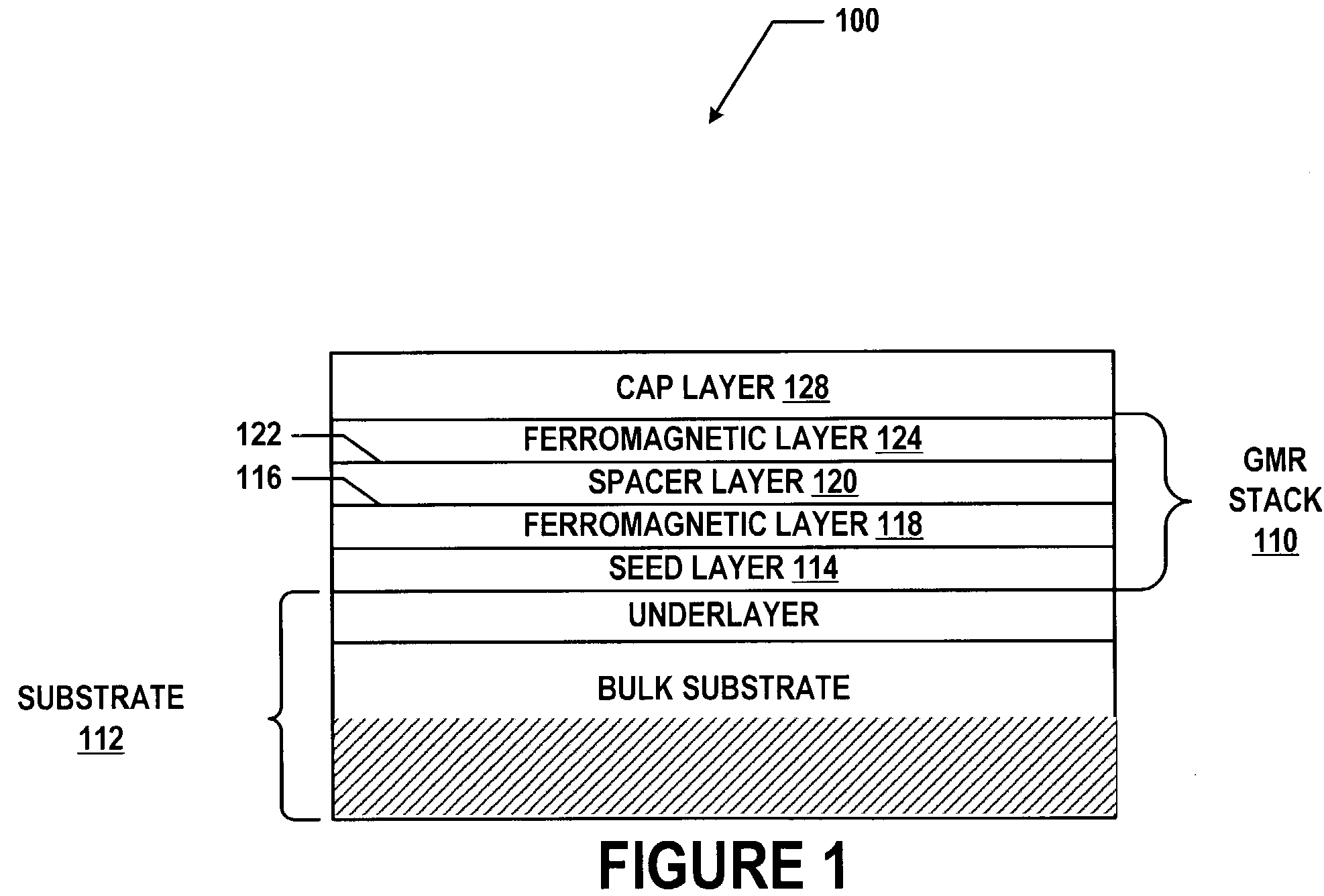

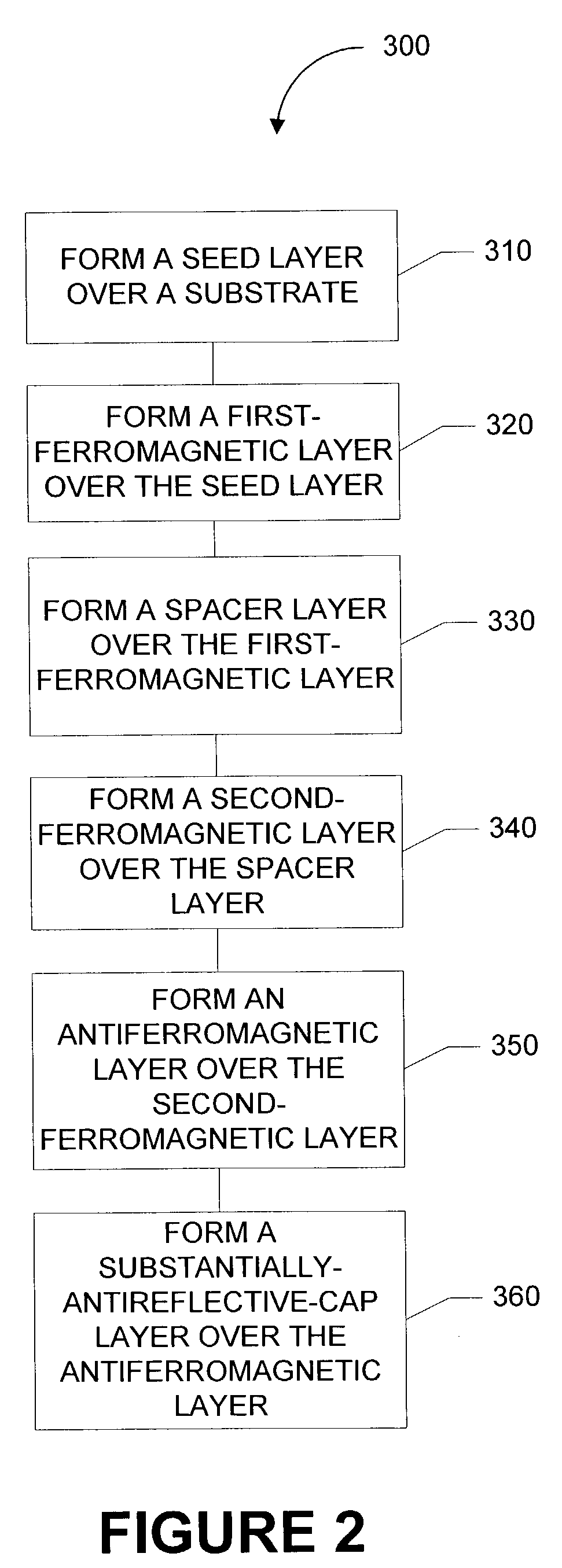

Etch-stop material for improved manufacture of magnetic devices

InactiveUS7183120B2Improved switching threshold of magnetoresistiveHigh selectivityNanostructure applicationNanomagnetismMagnetic reluctanceMagnetic memory

A method for fabricating a magnetoresistive device having at least one active region, which may be formed into a magnetic memory bit, sensor element and / or other device, is provided. In forming the magnetoresistive device, a magnetoresistive stack, such as a giant magnetoresistive stack, is formed over a substrate. In addition, a substantially antireflective cap layer formed from titanium nitride, aluminum nitride, and / or other substantially antireflective material, as opposed to the materials commonly used to form a cap layer, is formed over the magnetoresistive stack. The substantially antireflective cap layer is usable as an etch stop for later processing in forming the magnetic memory bit, sensor element and / or other device.

Owner:HONEYWELL INT INC

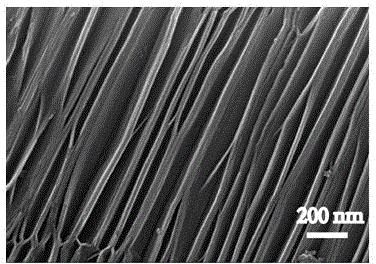

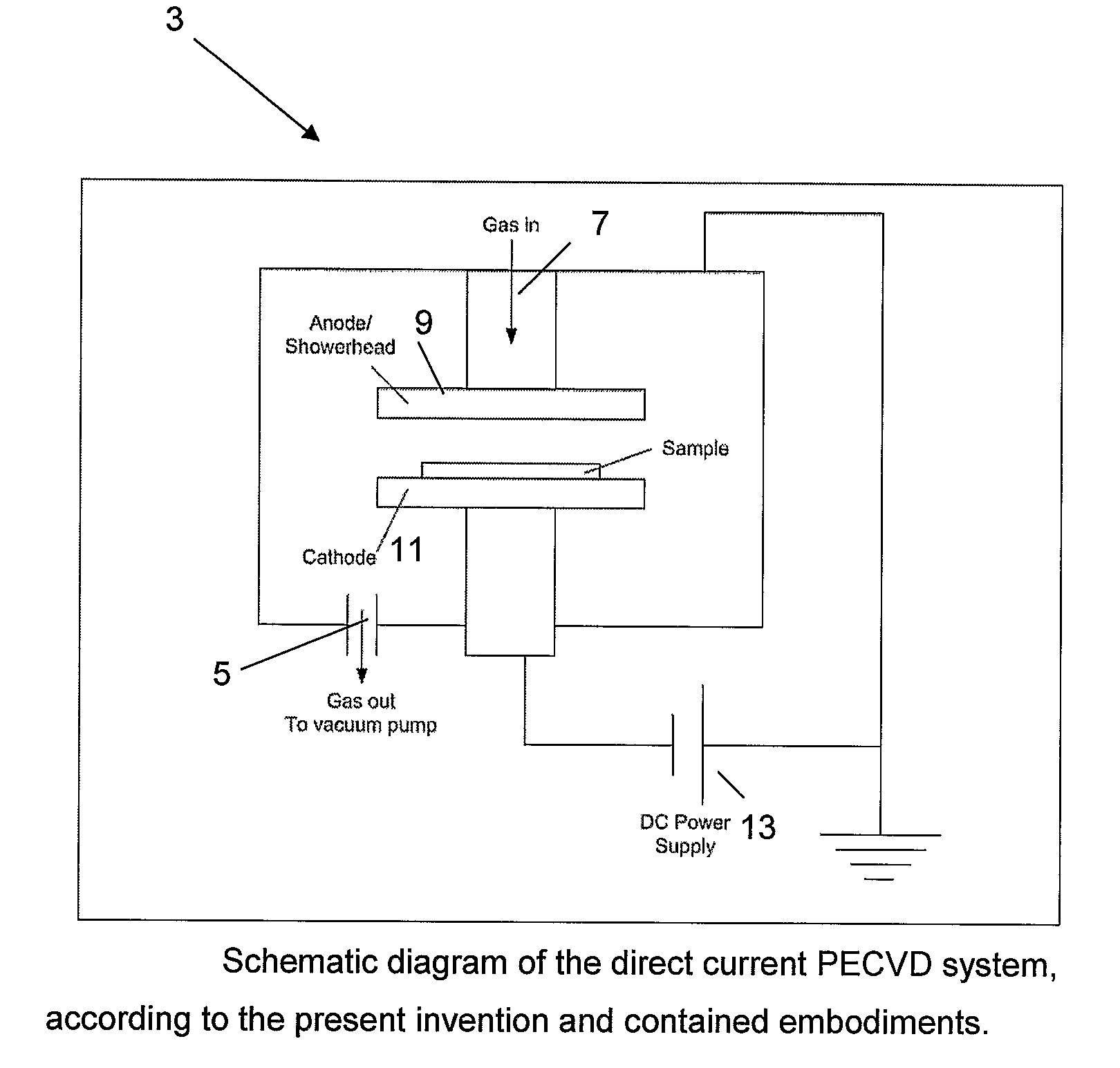

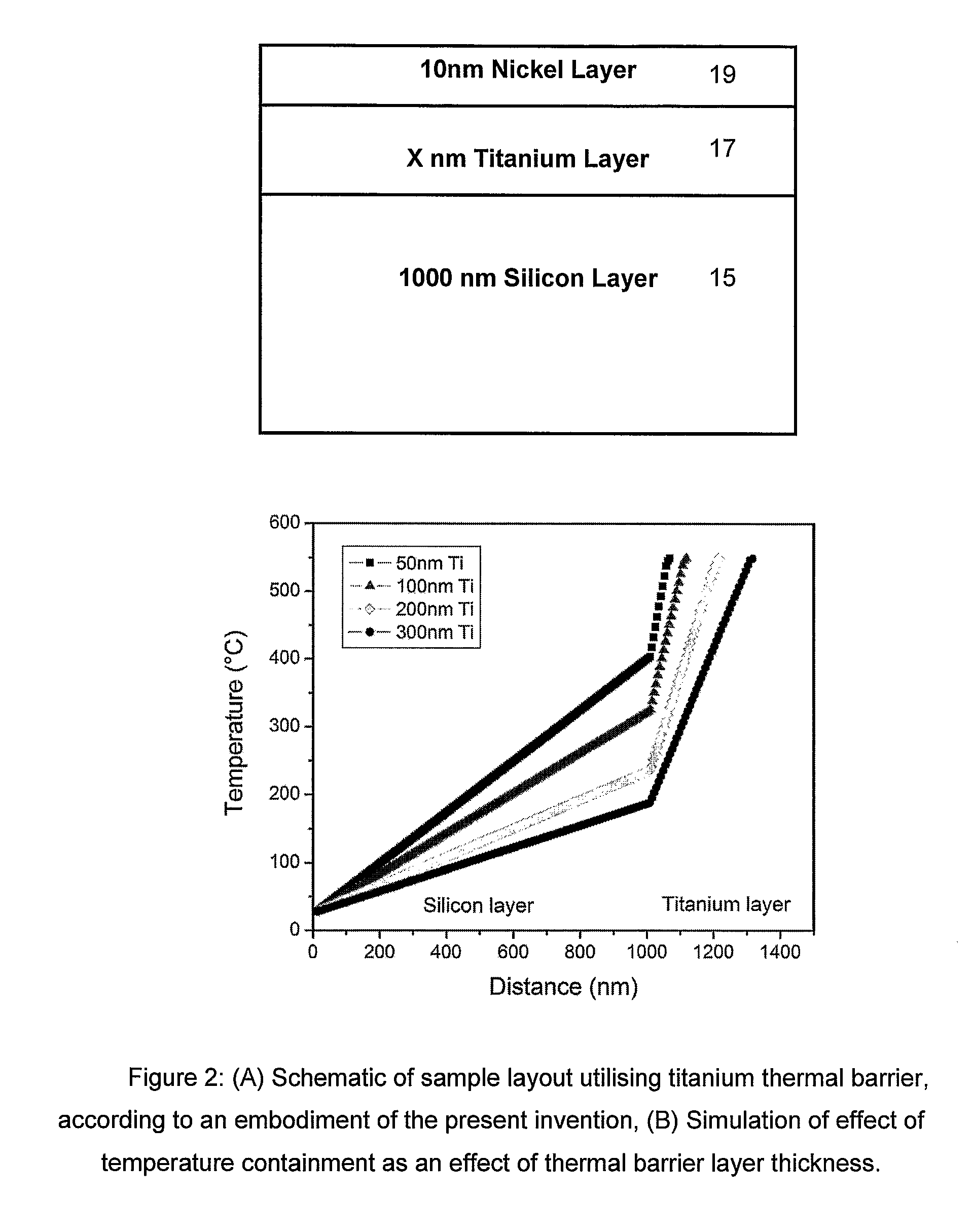

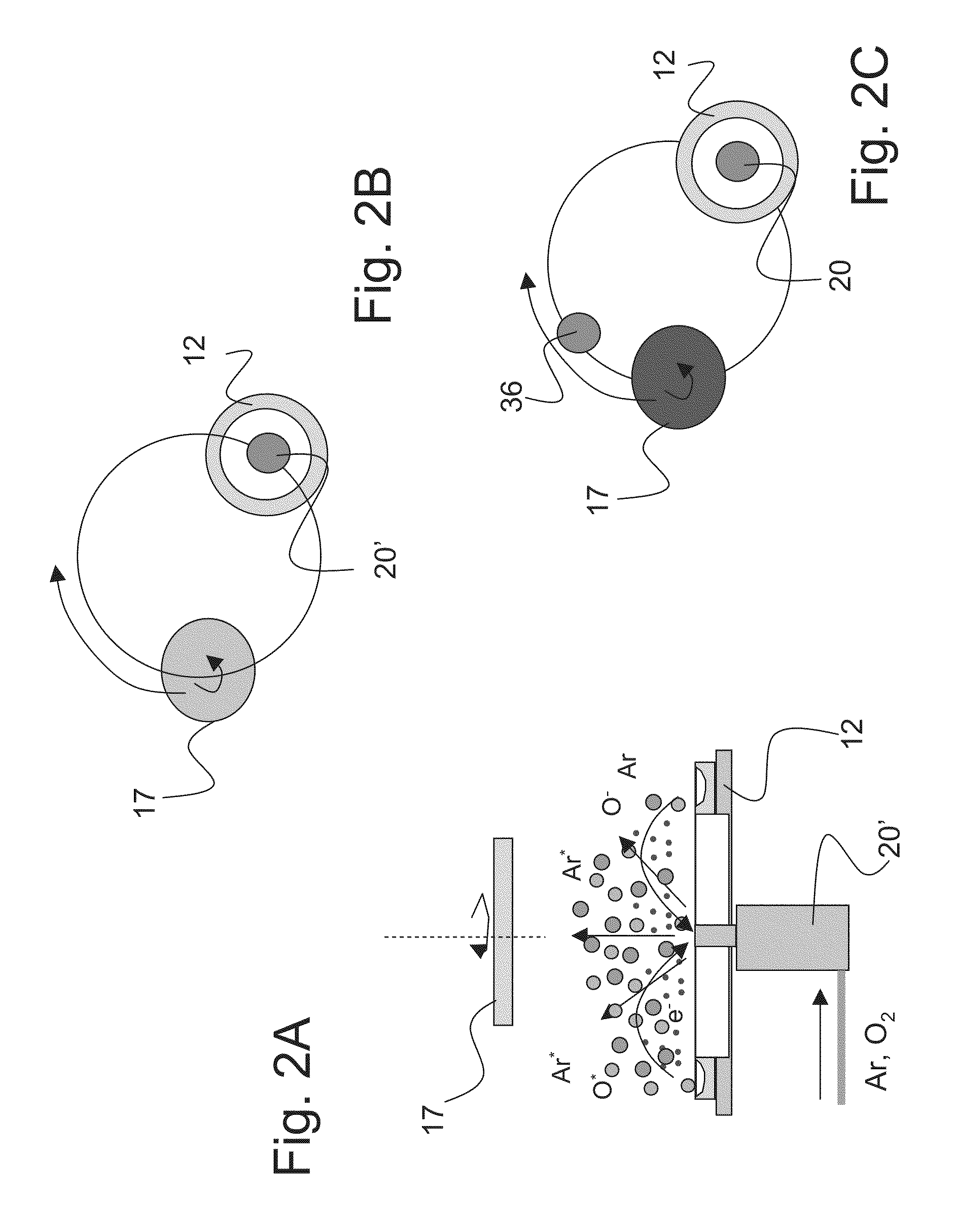

Nanostructure production methods and apparatus

ActiveUS20090061217A1Reduce thermal effectsIncrease rangeMaterial nanotechnologyNanostructure manufactureCompound (substance)Carbon nanotube

The present invention relates to a method of forming nanostructures or nanomaterials. The method comprises providing a thermal control barrier on a substrate and forming the nanostructures or nanomaterials. The method may, for example, be used to form carbon nanotubes by plasma enhanced chemical vapour deposition using a carbon containing gas plasma: The temperature of the substrate may be maintained at less than 350° C. while the carbon nanotubes are formed.

Owner:SURREY NANOSYST

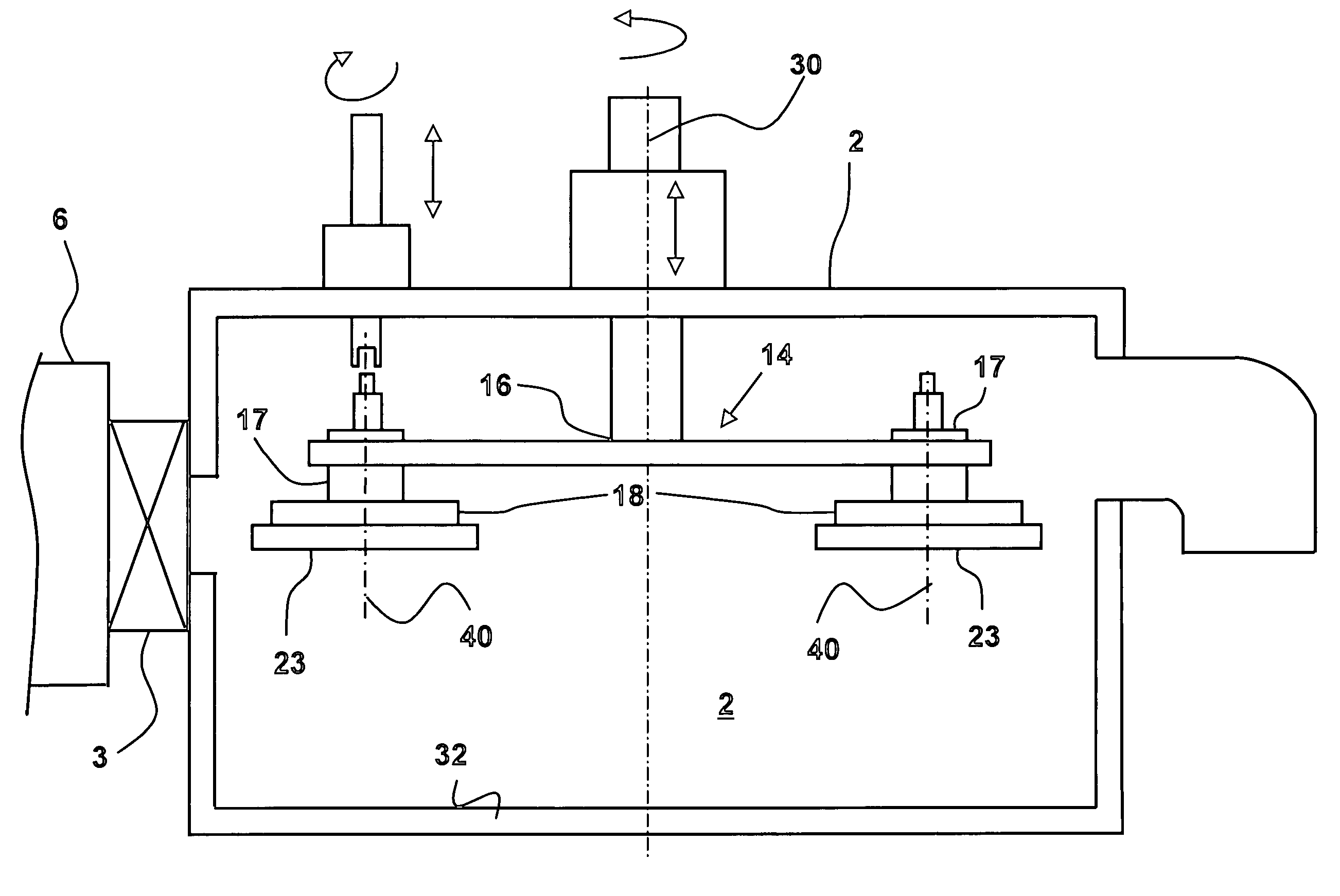

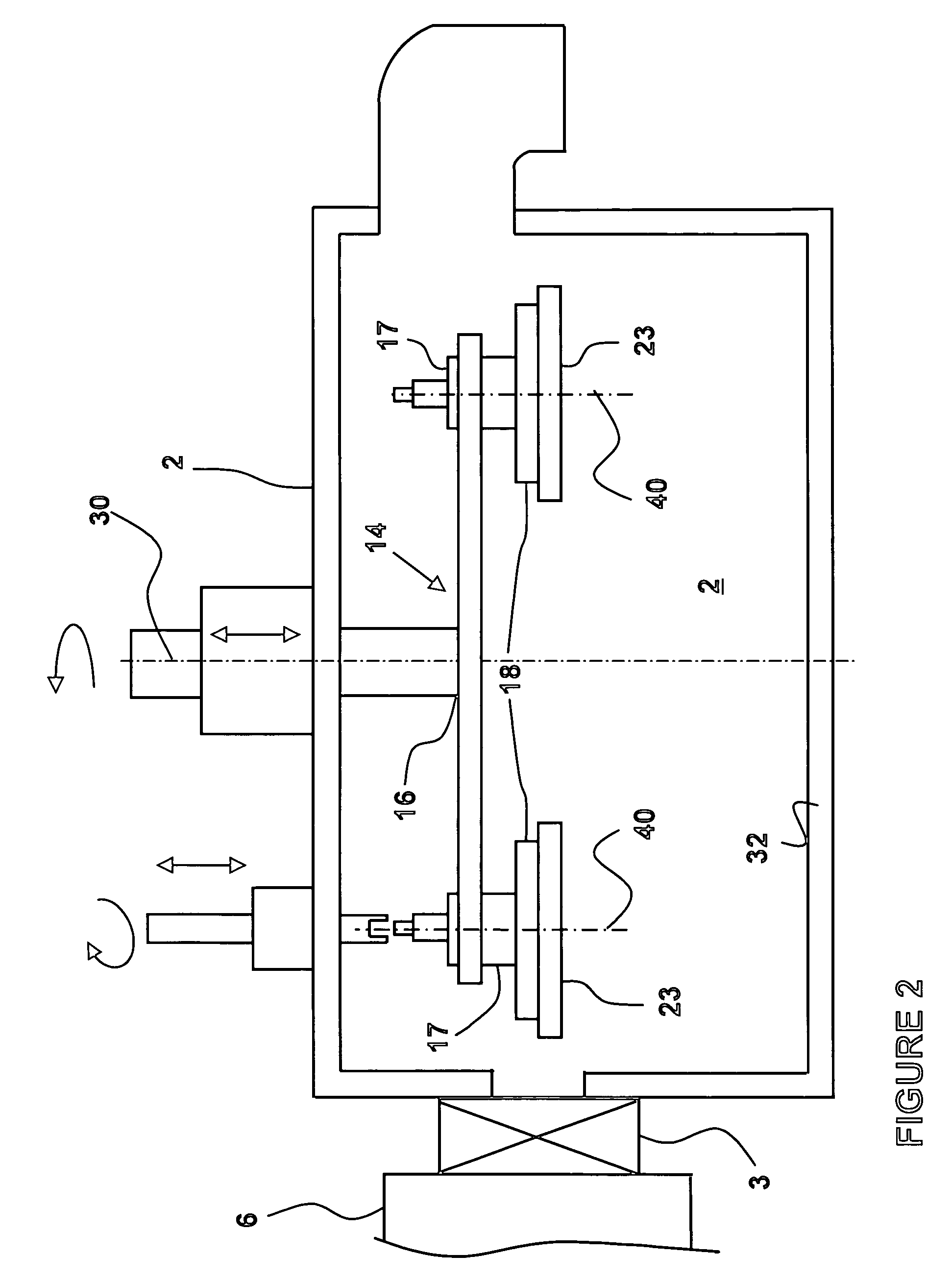

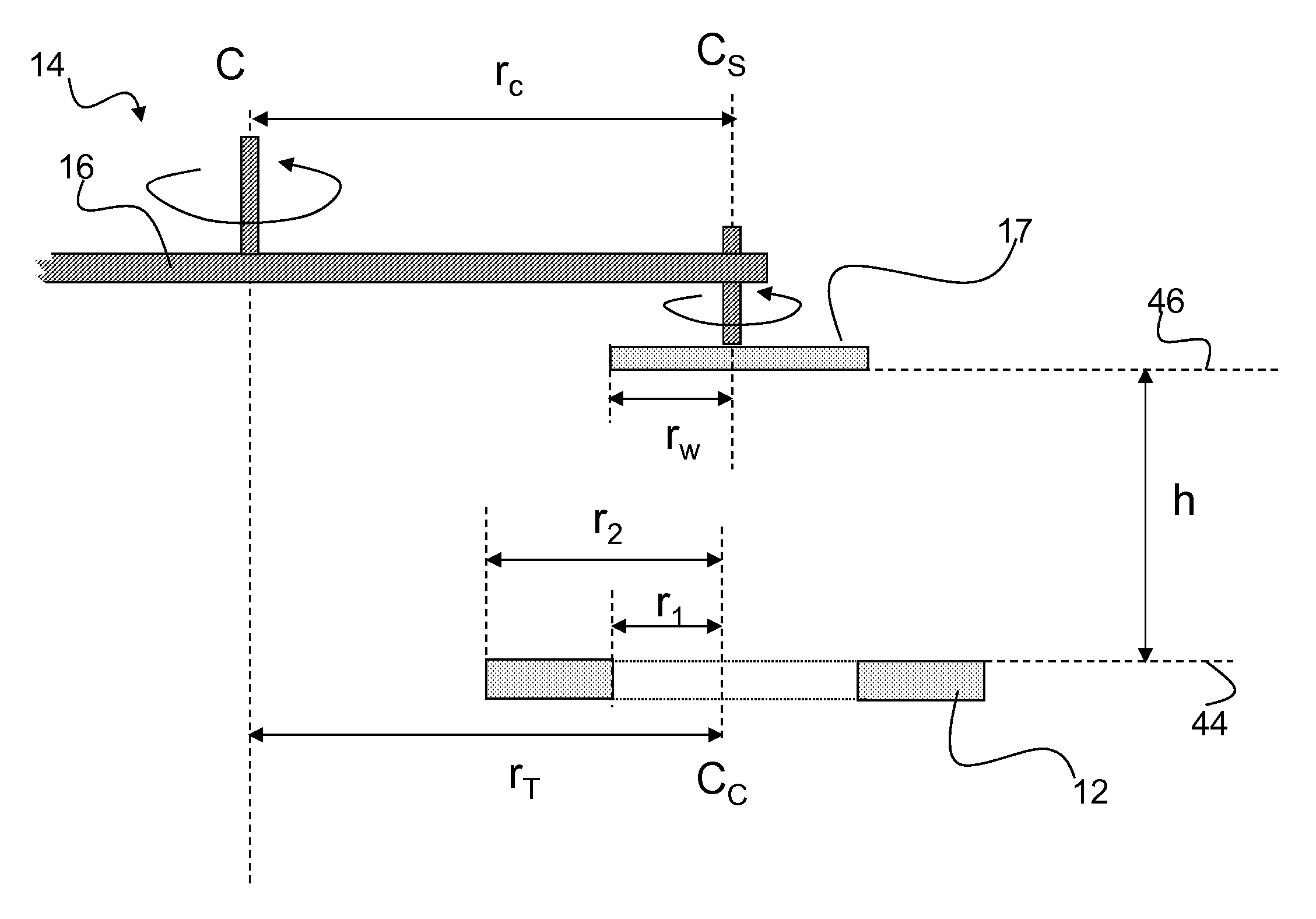

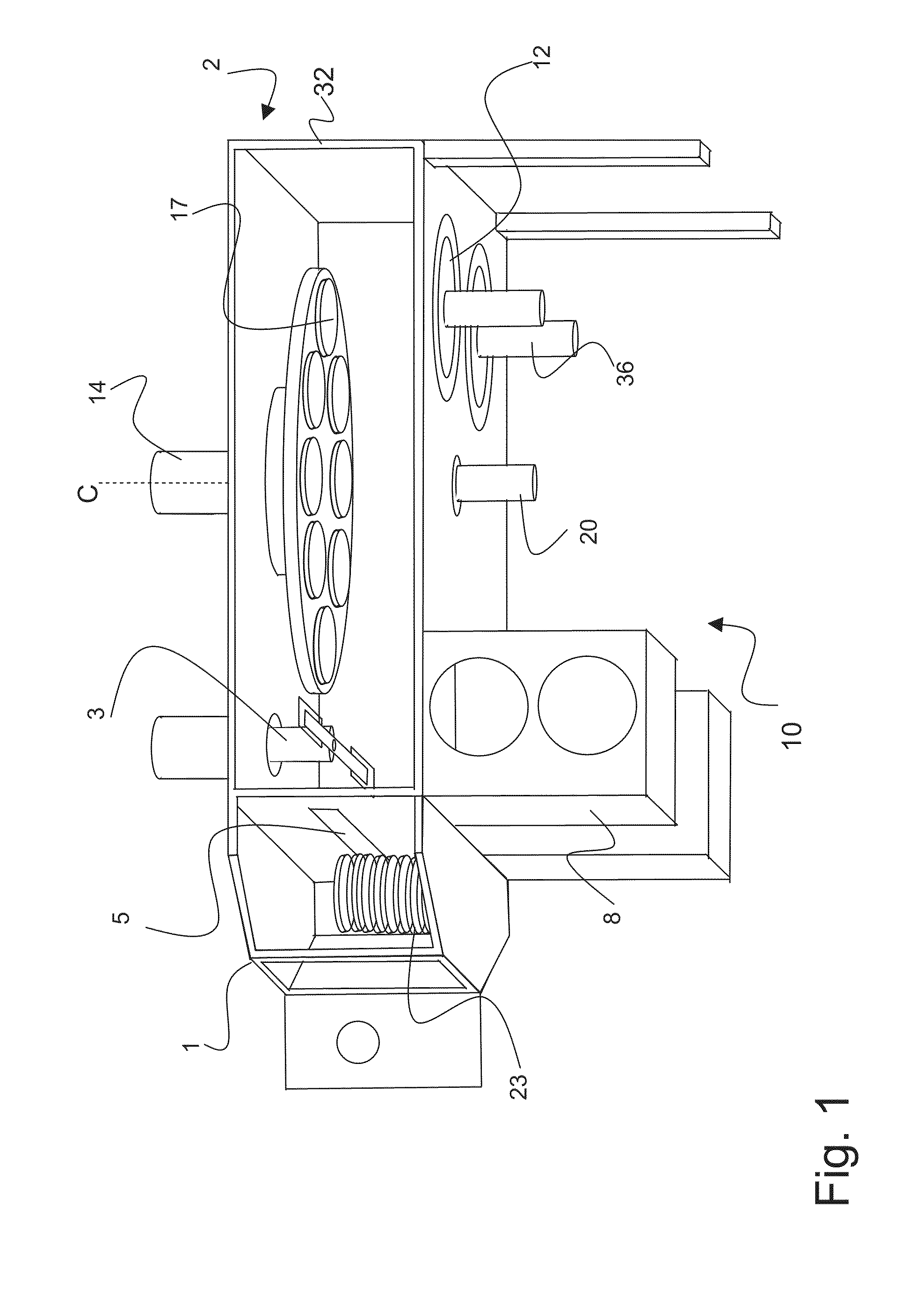

Magnetron sputtering device

ActiveUS20060070877A1Increase productionShorten cycle timeCellsElectric discharge tubesSputteringProduction rate

Owner:VIAVI SOLUTIONS INC

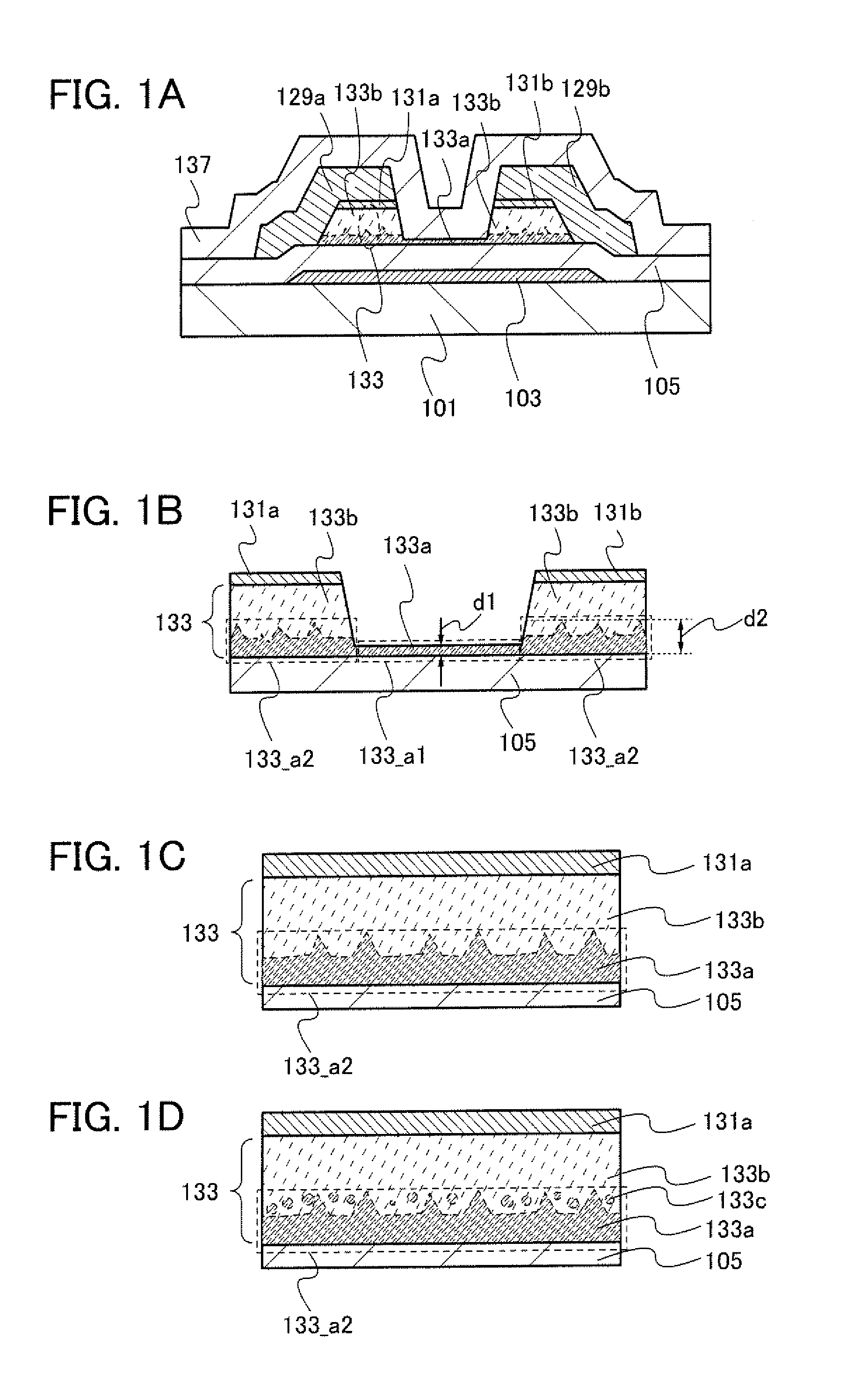

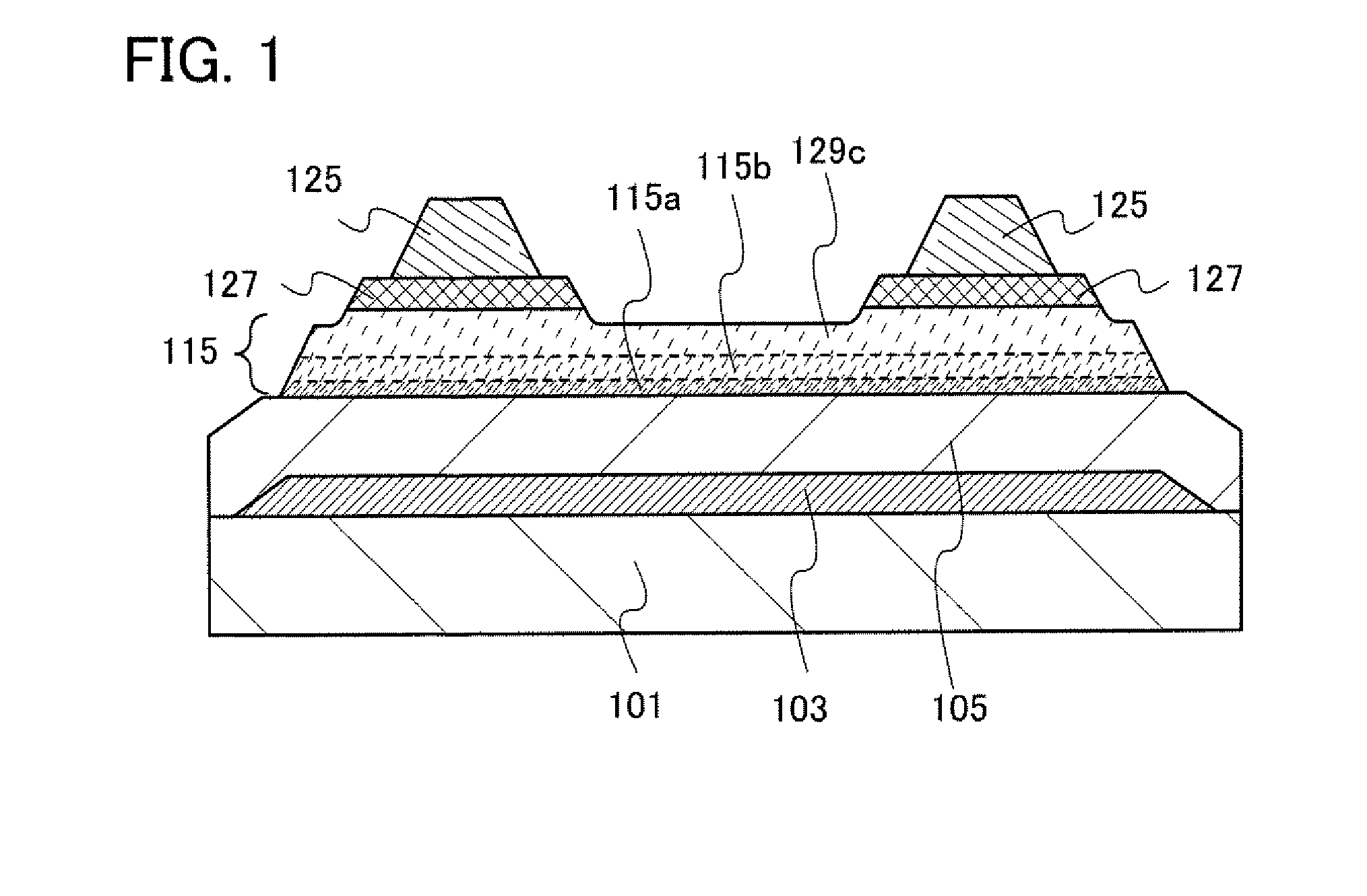

Thin film transistor

ActiveUS20100224879A1Minimal costIncrease in sizeTransistorSolid-state devicesProduction rateSemiconductor package

A thin film transistor includes a gate insulating layer covering a gate electrode, a semiconductor layer in contact with the gate insulating layer, and impurity semiconductor layers which are in contact with part of the semiconductor layer and which form a source region and a drain region. The semiconductor layer includes a microcrystalline semiconductor layer formed on the gate insulating layer and a microcrystalline semiconductor region containing nitrogen in contact with the microcrystalline semiconductor layer. The thin film transistor in which off-current is small and on-current is large can be manufactured with high productivity.

Owner:SEMICON ENERGY LAB CO LTD

SOI by oxidation of porous silicon

InactiveUS7566482B2Simple and cost-effectiveReduce defect levelAnodisationVacuum evaporation coatingDopantPorous layer

A method in which a SOI substrate structure is fabricated by oxidation of graded porous Si is provided. The graded porous Si is formed by first implanting a dopant (p- or n-type) into a Si-containing substrate, activating the dopant using an activation anneal step and then anodizing the implanted and activated dopant region in a HF-containing solution. The graded porous Si has a relatively coarse top layer and a fine porous layer that is buried beneath the top layer. Upon a subsequent oxidation step, the fine buried porous layer is converted into a buried oxide, while the coarse top layer coalesces into a solid Si-containing over-layer by surface migration of Si atoms.

Owner:GLOBALFOUNDRIES INC

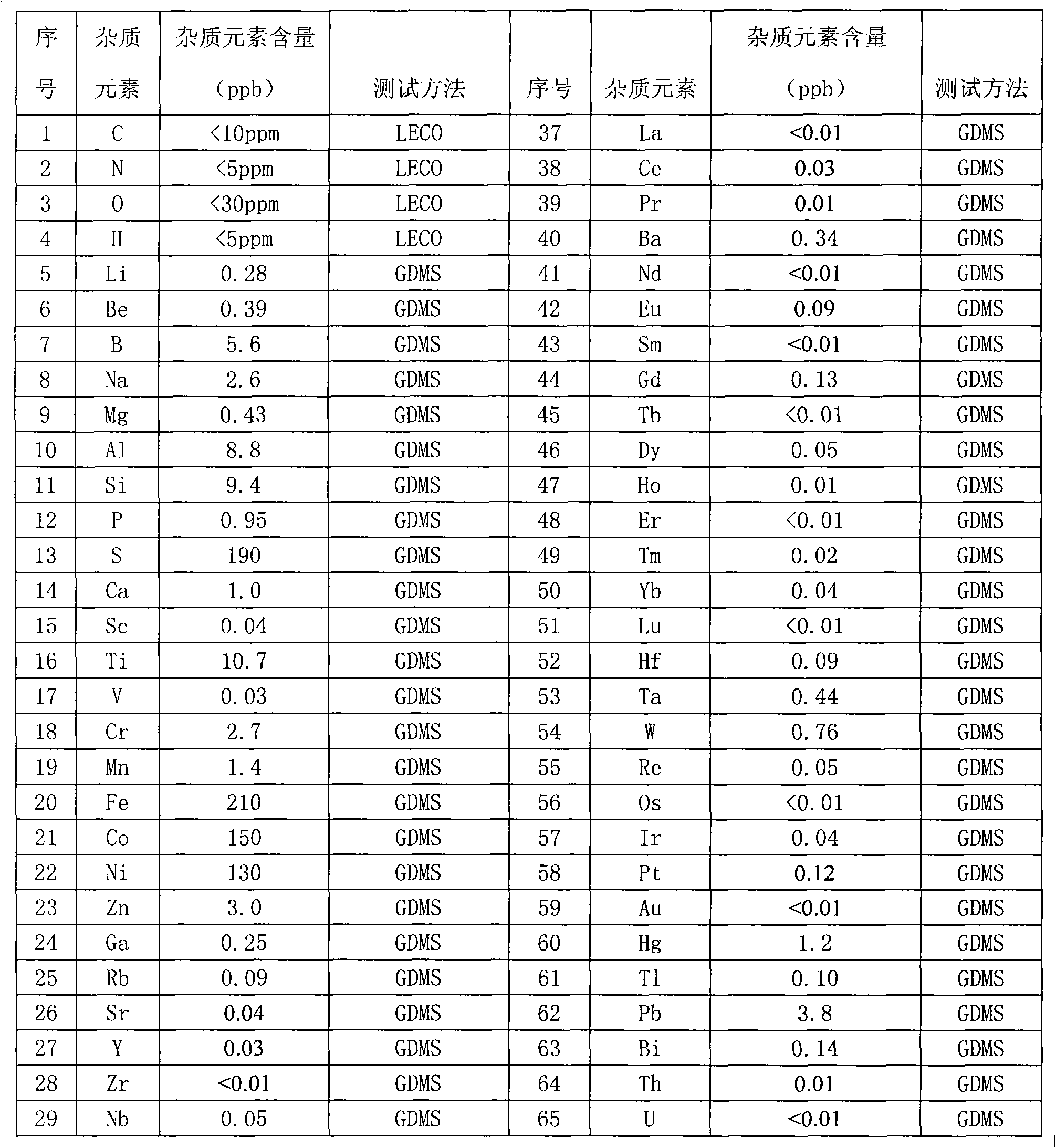

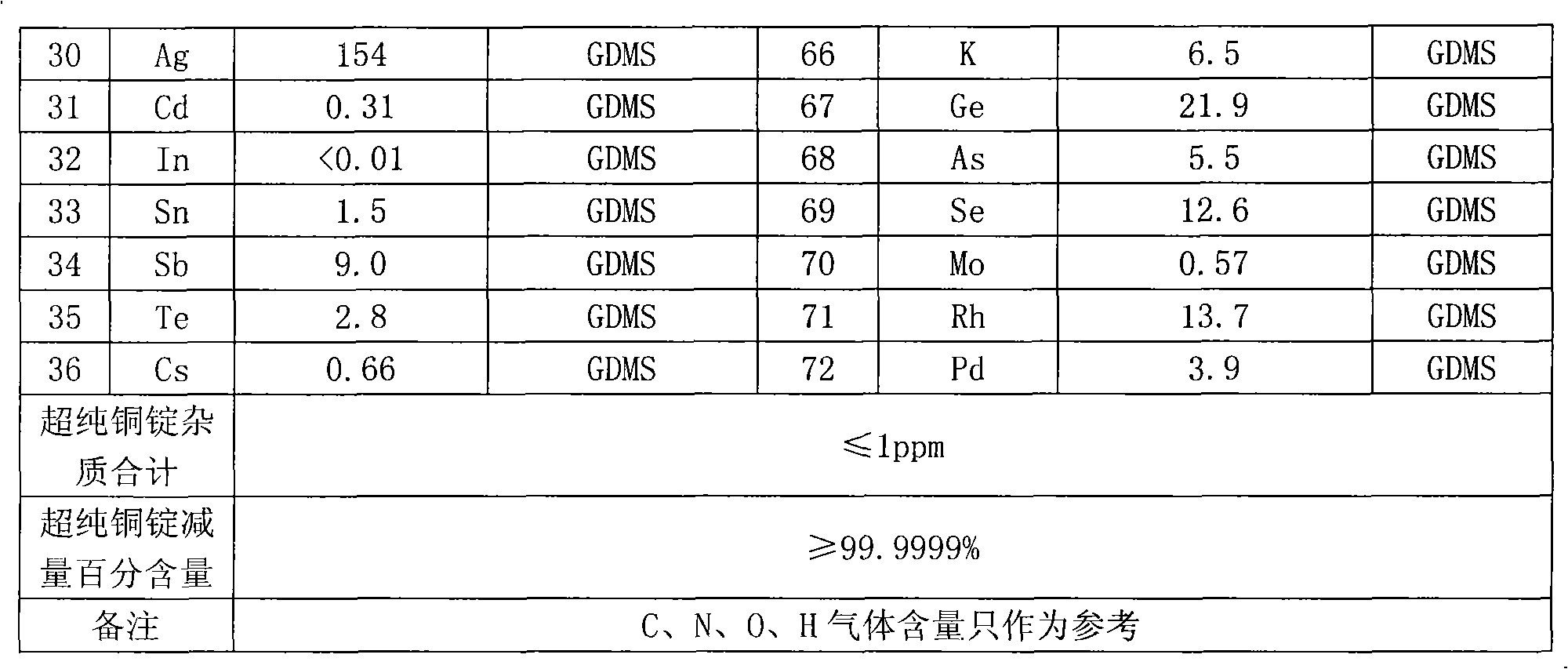

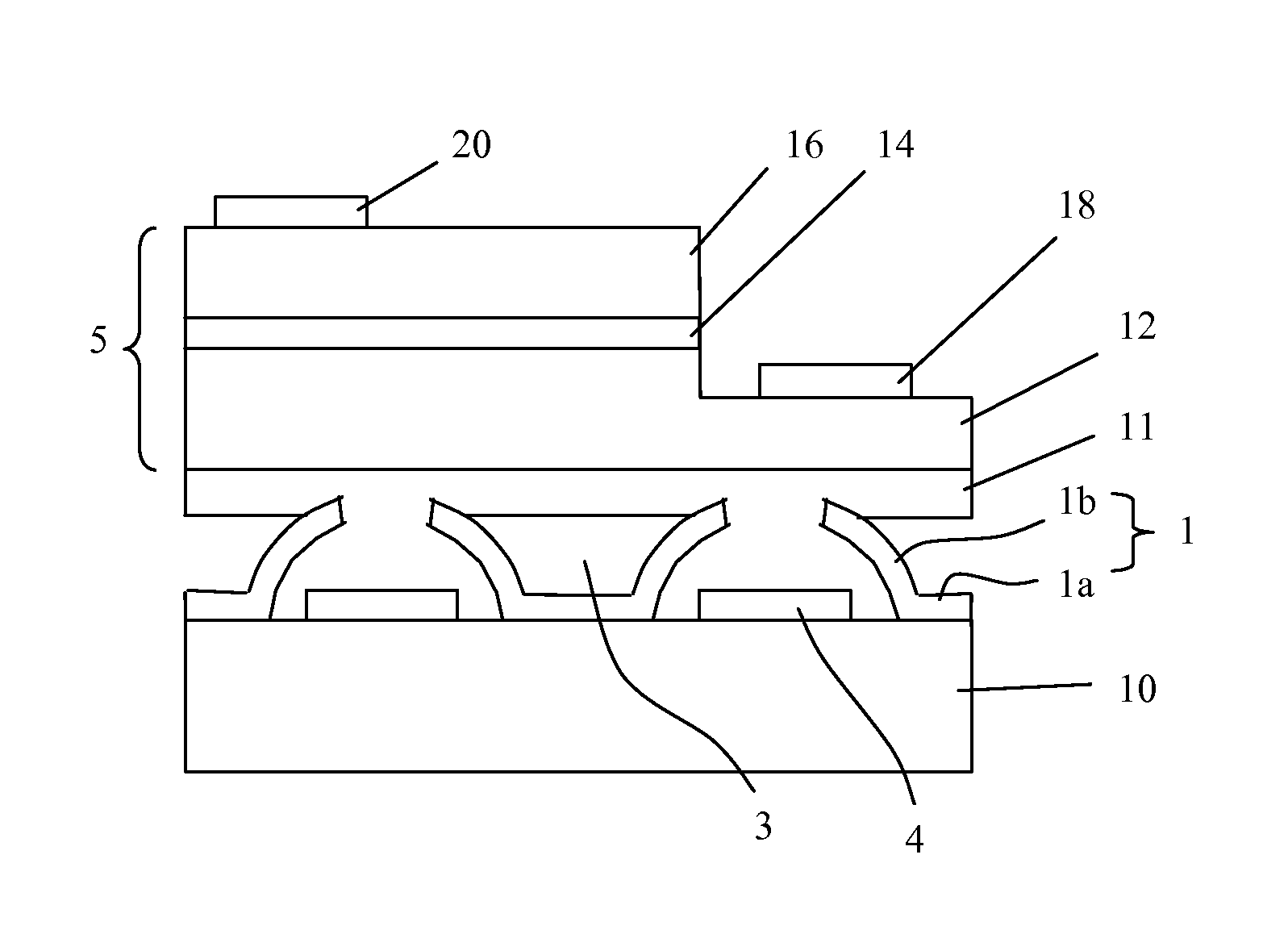

Method for preparing ultrapure copper ingot

The invention relates to a method for preparing an ultrapure copper ingot by performing electron beam melting technology on an ultrapure copper plate obtained by adopting an electrolytic method in an electron beam melting furnace. The method is characterized in that: in the preparation process, a 6 N (the purity is more than or equal to 99.9999 percent) electrolytic ultrapure copper plate is taken as a raw material, is subjected to surface cleaning and is subjected to the electron beam melting technology in the electron beam melting furnace so as to obtain a 6 N or more than 6 N ultrapure copper ingot. The invention provides a method which can effectively solve the problems that: the product specification form is single, several impurity elements are difficult to remove and the consistency is low, reduces the production cost, saves the energy, realizes the diversification of product forms, optimizes the physical property, improves the product quality and fully meets the use requirement of various downstream customers.

Owner:JINCHUAN GROUP LIMITED

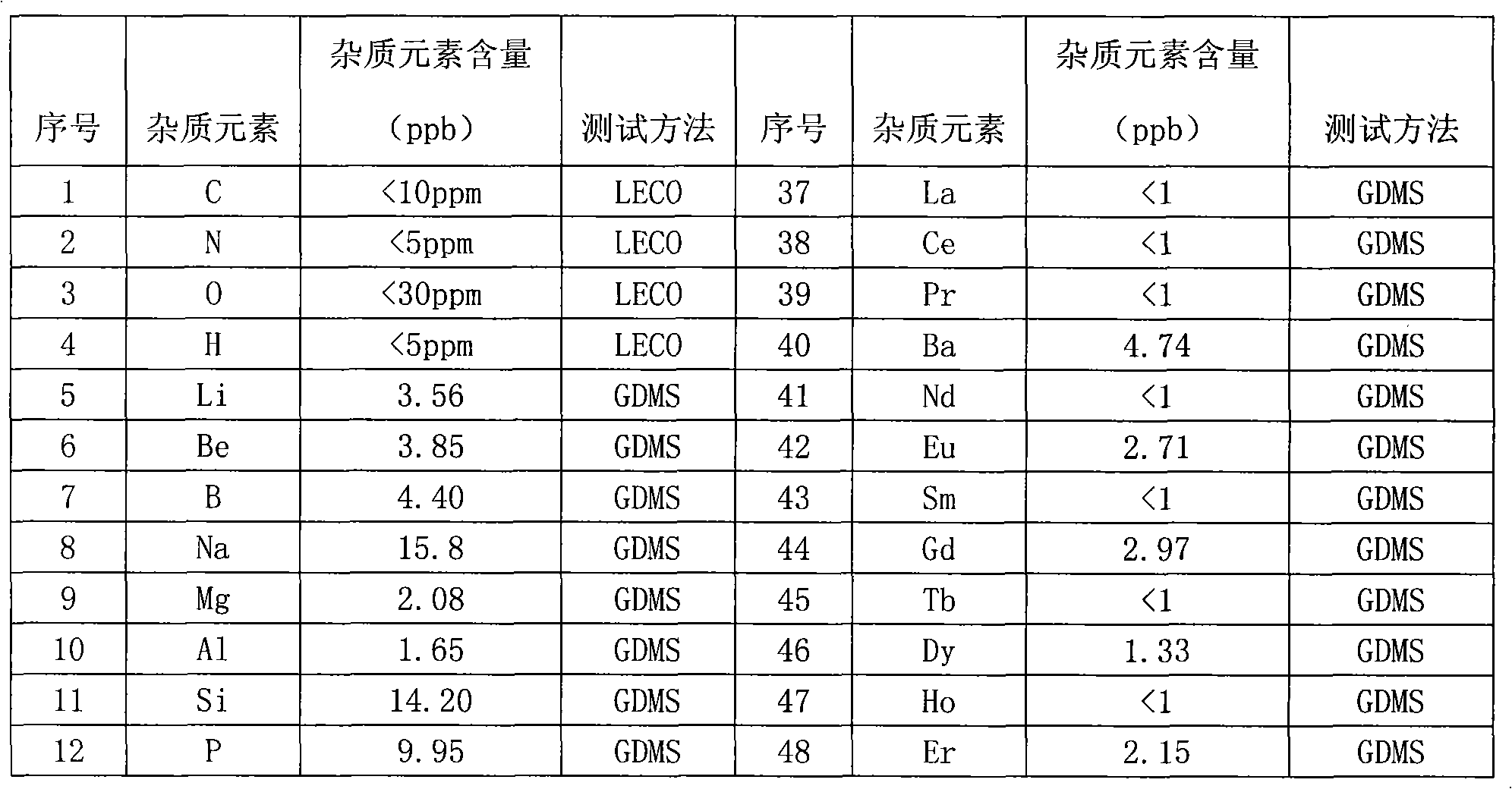

Semiconductor light-emitting device and method of manufacturing the same

ActiveUS20140231841A1Less stressLess heatSolid-state devicesSemiconductor devicesLight beamActive layer

A light-emitting device is disclosed including a light emitting structure comprising a lower layer of the first conductivity type, an active layer, an upper layer of the second conductivity type; a first electrode connected to the lower layer of the first conductivity type; a second electrode connected to the upper layer of the second conductivity type. The light emitting structure is formed using a shell member, which comprises a planar portion and a shell portion. The extent of growth defects such as misfit dislocations is reduced and the extraction of light and heat is improved in the present device. The beam profile of the device may be altered by patterning the light emitting structure instead of shaping the entire chip. The device may be manufactured in a way more compatible with the established, cost-effective processing and packaging methods for large size wafers from the IC industry.

Owner:WANG TIEN YANG

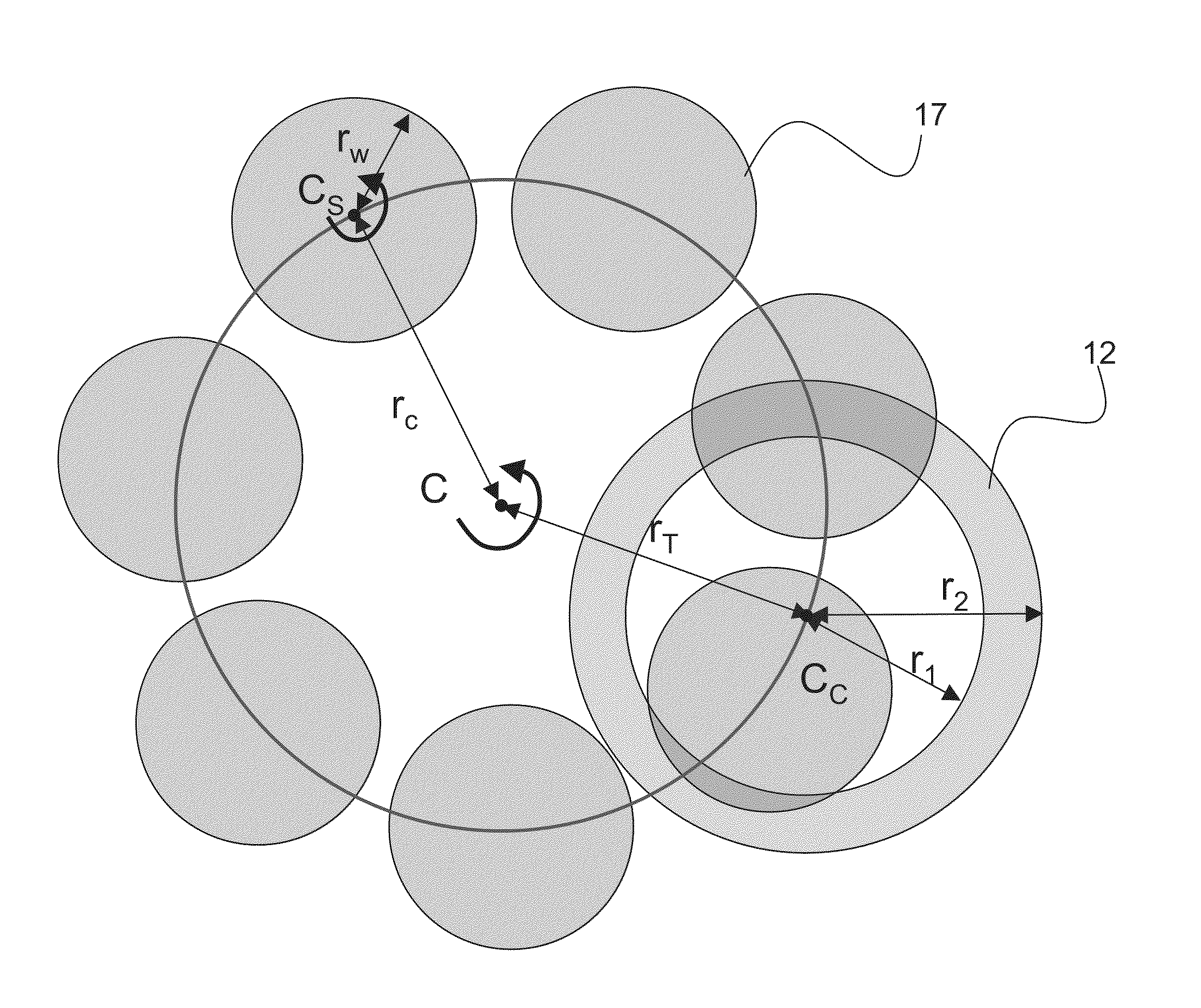

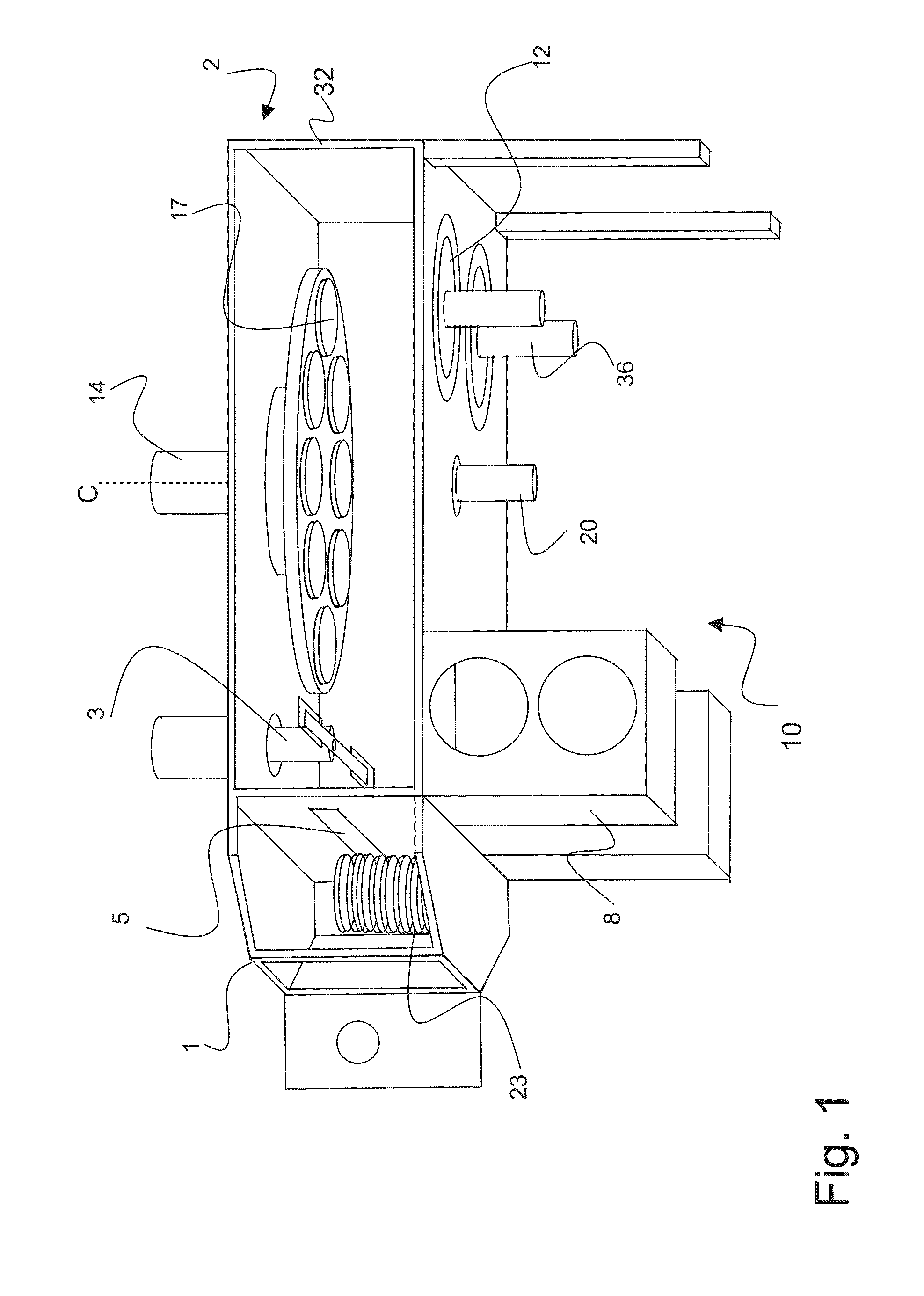

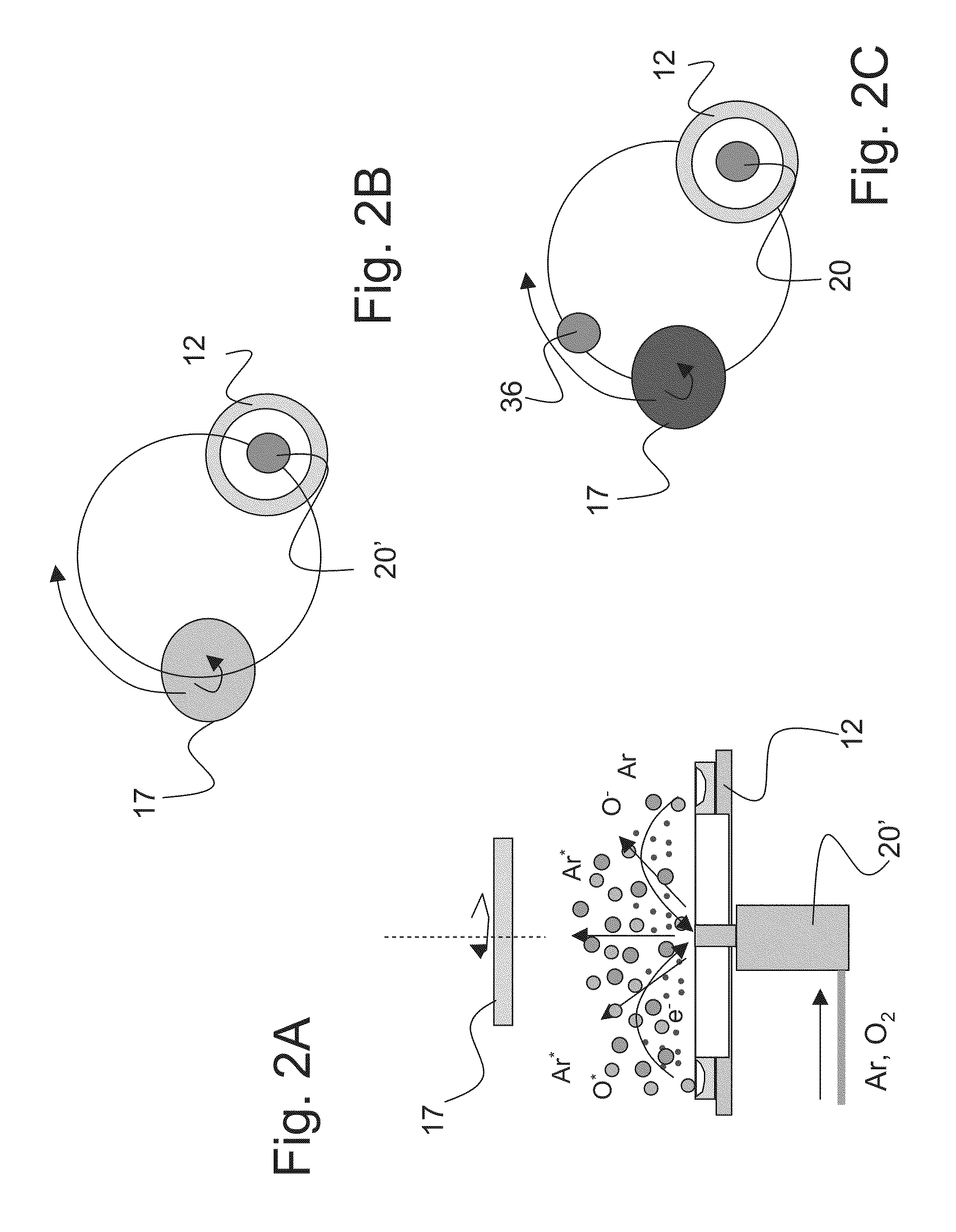

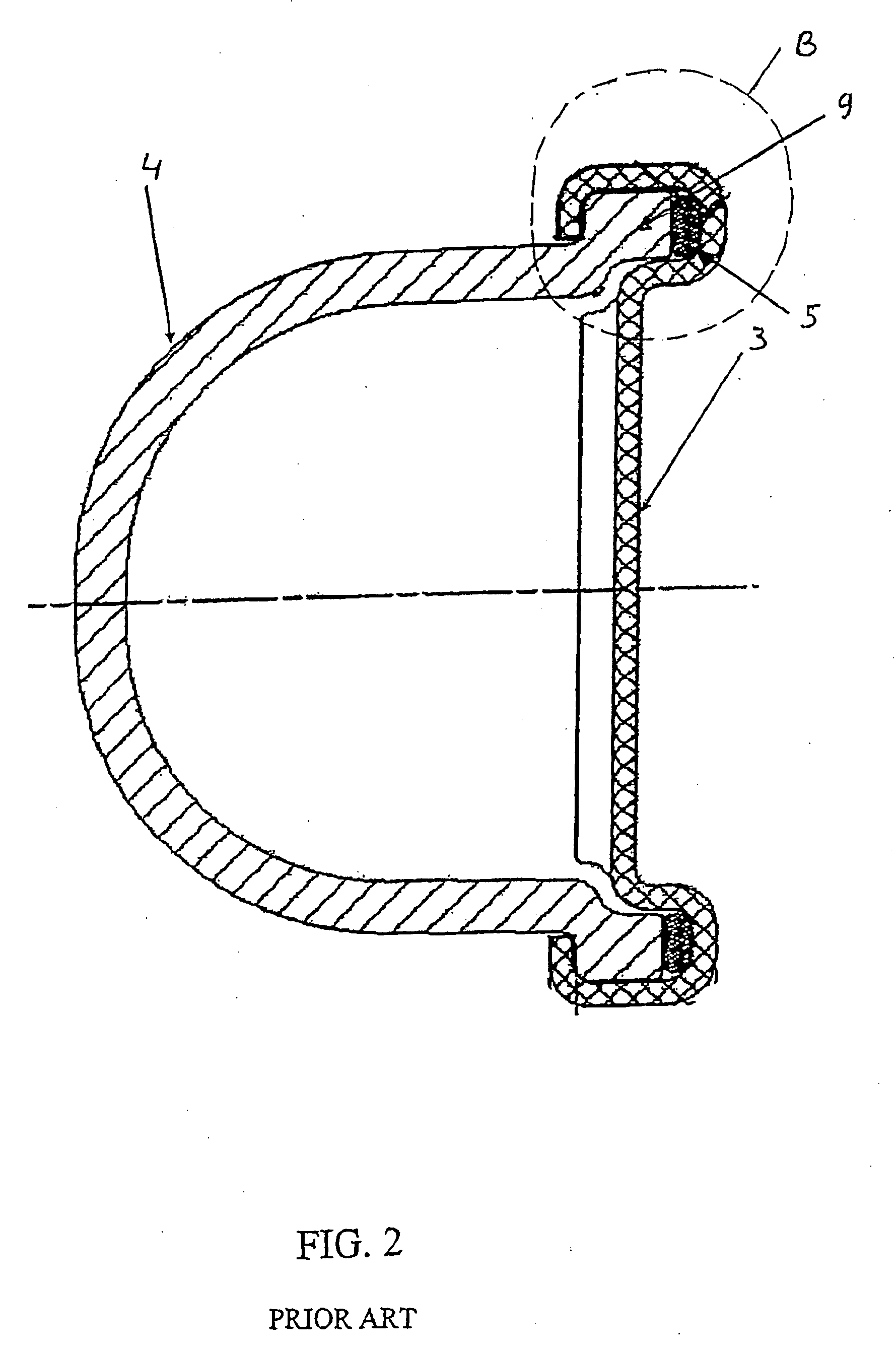

Ring cathode for use in a magnetron sputtering device

ActiveUS20110253529A1Improve coating uniformityImprovement in planet to planet uniformityCellsElectric discharge tubesReactive gasEngineering

The present invention relates to a magnetron sputtering device including a large ring cathode having a defined inner radius. The position of the ring cathode is offset in relation to a center point of a planetary drive system. An anode or reactive gas source may be located within the inner radius of the ring cathode. Lower defect rates are obtained through the lower power density at the cathode which suppresses arcing, while runoff is minimized by the cathode to planet geometry without the use of a mask.

Owner:VIAVI SOLUTIONS INC

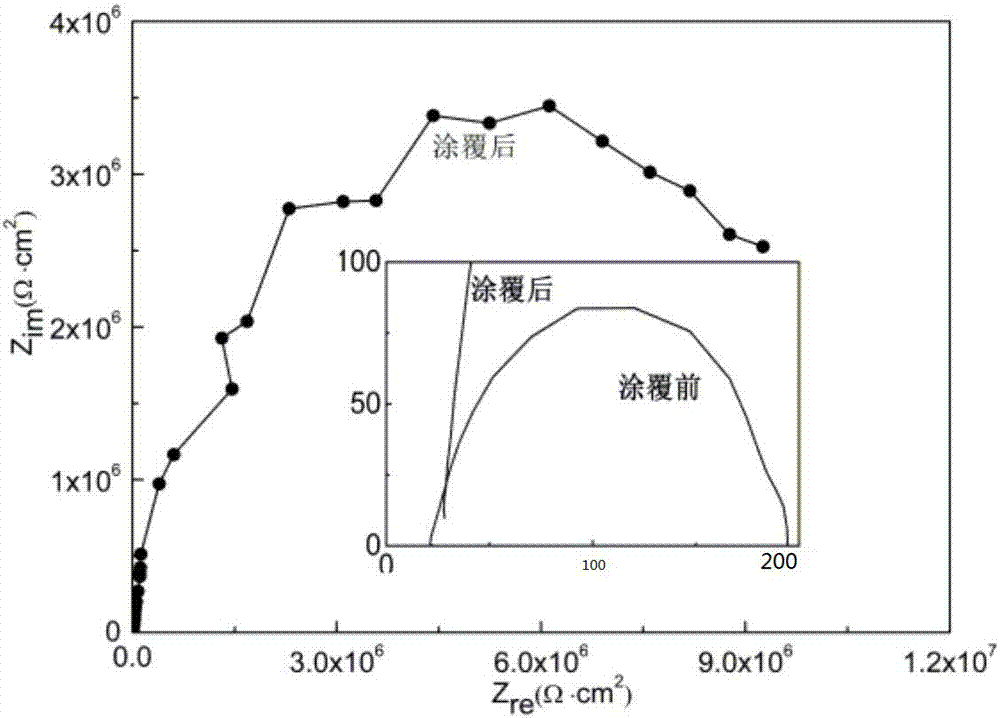

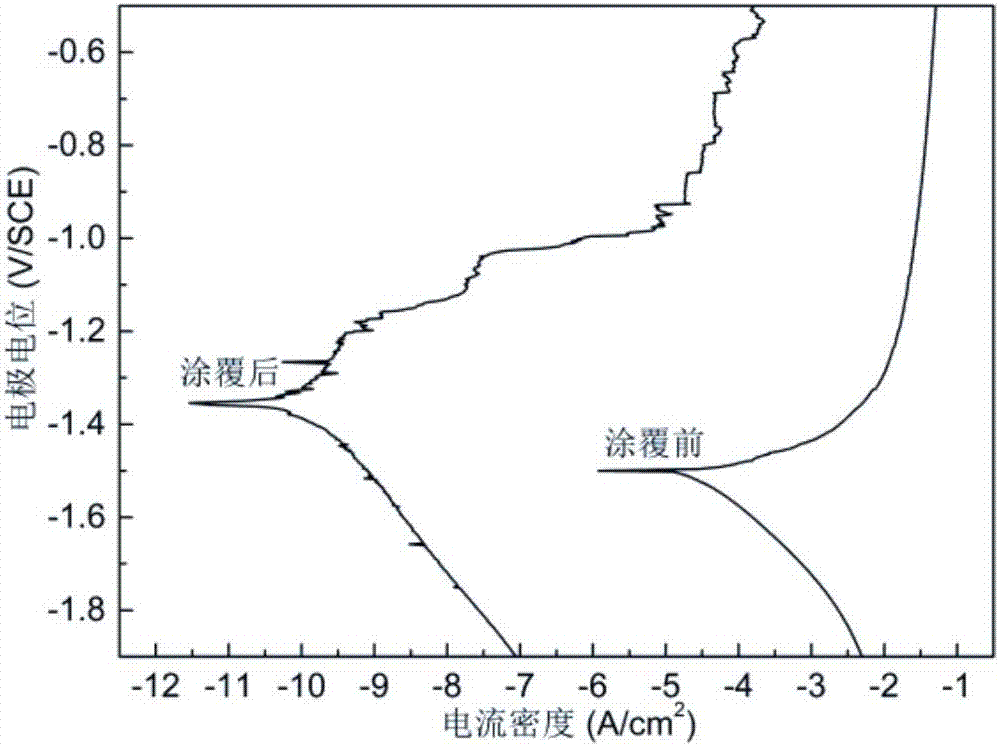

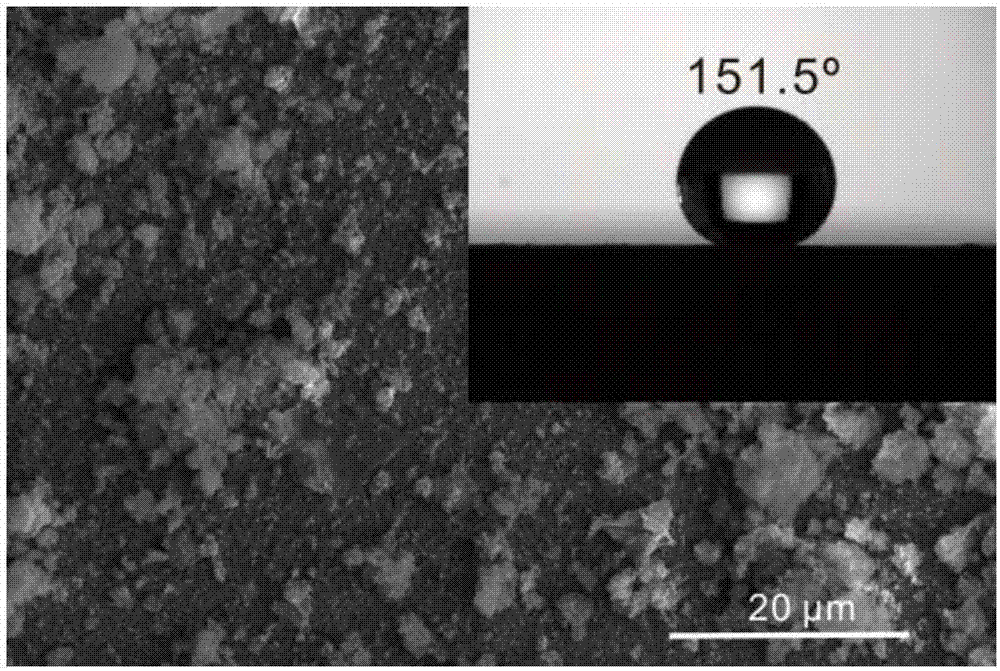

Preparation method of silane-cerium oxide-hydrotalcite composite coating on surface of magnesium/magnesium alloy matrix

ActiveCN107059005AReduce defect levelInhibition of anodic reactionLiquid/solution decomposition chemical coatingSuperimposed coating processEnvironmental resistanceSynthesis methods

The invention discloses a preparation method of a silane-cerium oxide-hydrotalcite composite coating on the surface of a magnesium / magnesium alloy matrix. The preparation method comprises four steps, including preparation of a hydrotalcite precursor, pretreatment of magnesium alloy, preparation of a hydrotalcite coating and preparation of a composite coating; and main chemical raw materials adopted in the preparation method include absolute ethyl alcohol, a silane coupling agent, ultrapure water and cerium salt, wherein the cerium salt is water-soluble salt. The technical route of the preparation method comprises the following steps: firstly depositing a layer of a hydrotalcite film (the chemical ingredient is Mg6Al2(OH)16CO3.4H2O) on the surface of the magnesium or magnesium alloy matrix by adopting a hydro-thermal synthesis method; and subsequently soaking a sample into a mixed solution of the silane coupling agent and the cerium salt so as to accomplish the preparation of the composite coating. The preparation method disclosed by the invention has the technical characteristics that the process is environmentally friendly and controlled simply and easily; the prepared composite coating is compact in structure, high in adhesive force, good in corrosion resistance and long in service life, and the like; and the composite coating is especially applicable to preservative treatment of a material applied to a magnesium alloy structure of maritime machinery equipment.

Owner:SHANDONG UNIV OF SCI & TECH

Ring cathode for use in a magnetron sputtering device

ActiveUS8480865B2Increase the areaSimple materialCellsElectric discharge tubesReactive gasEngineering

The present invention relates to a magnetron sputtering device including a large ring cathode having a defined inner radius. The position of the ring cathode is offset in relation to a center point of a planetary drive system. An anode or reactive gas source may be located within the inner radius of the ring cathode. Lower defect rates are obtained through the lower power density at the cathode which suppresses arcing, while runoff is minimized by the cathode to planet geometry without the use of a mask.

Owner:VIAVI SOLUTIONS INC

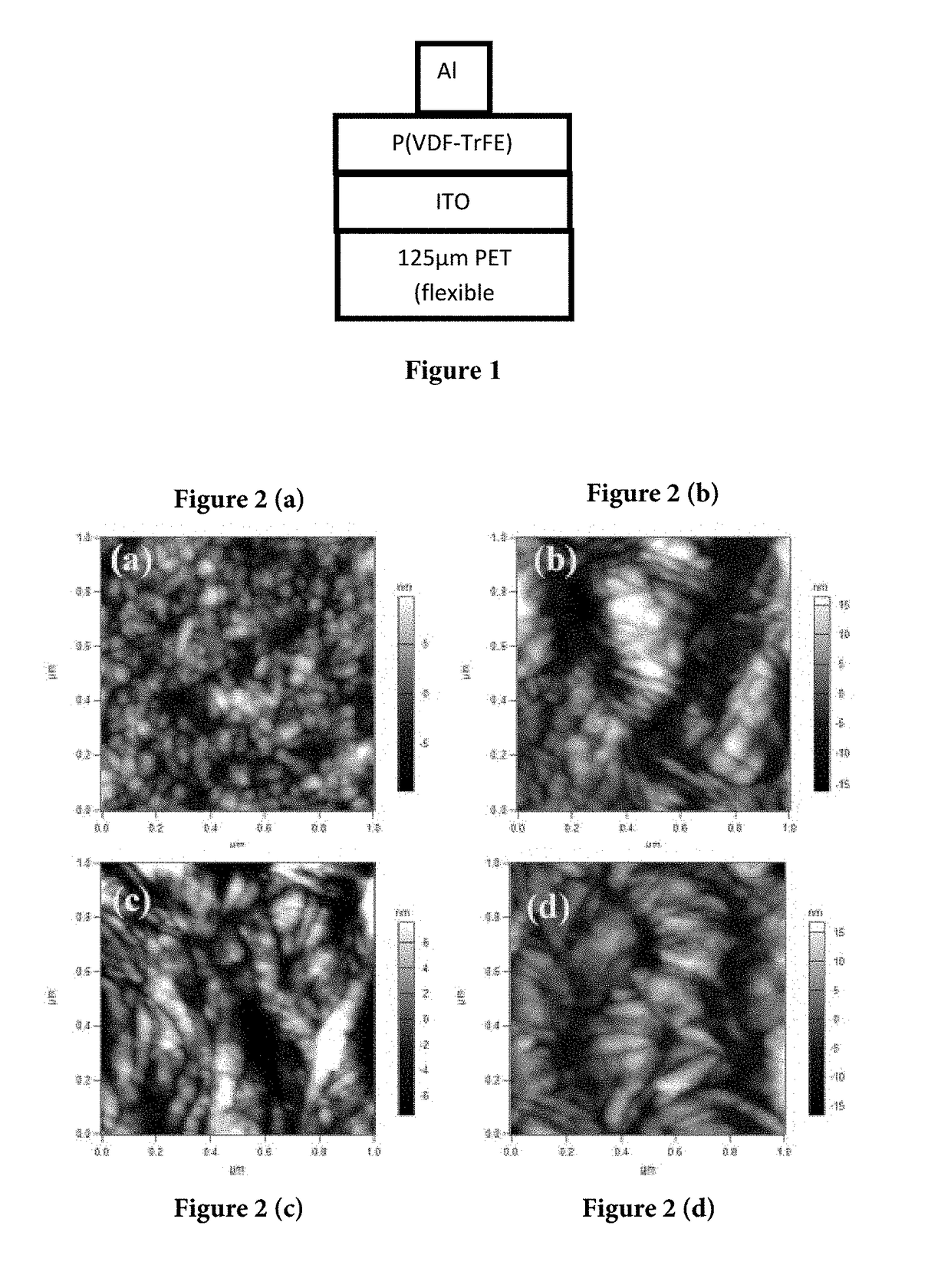

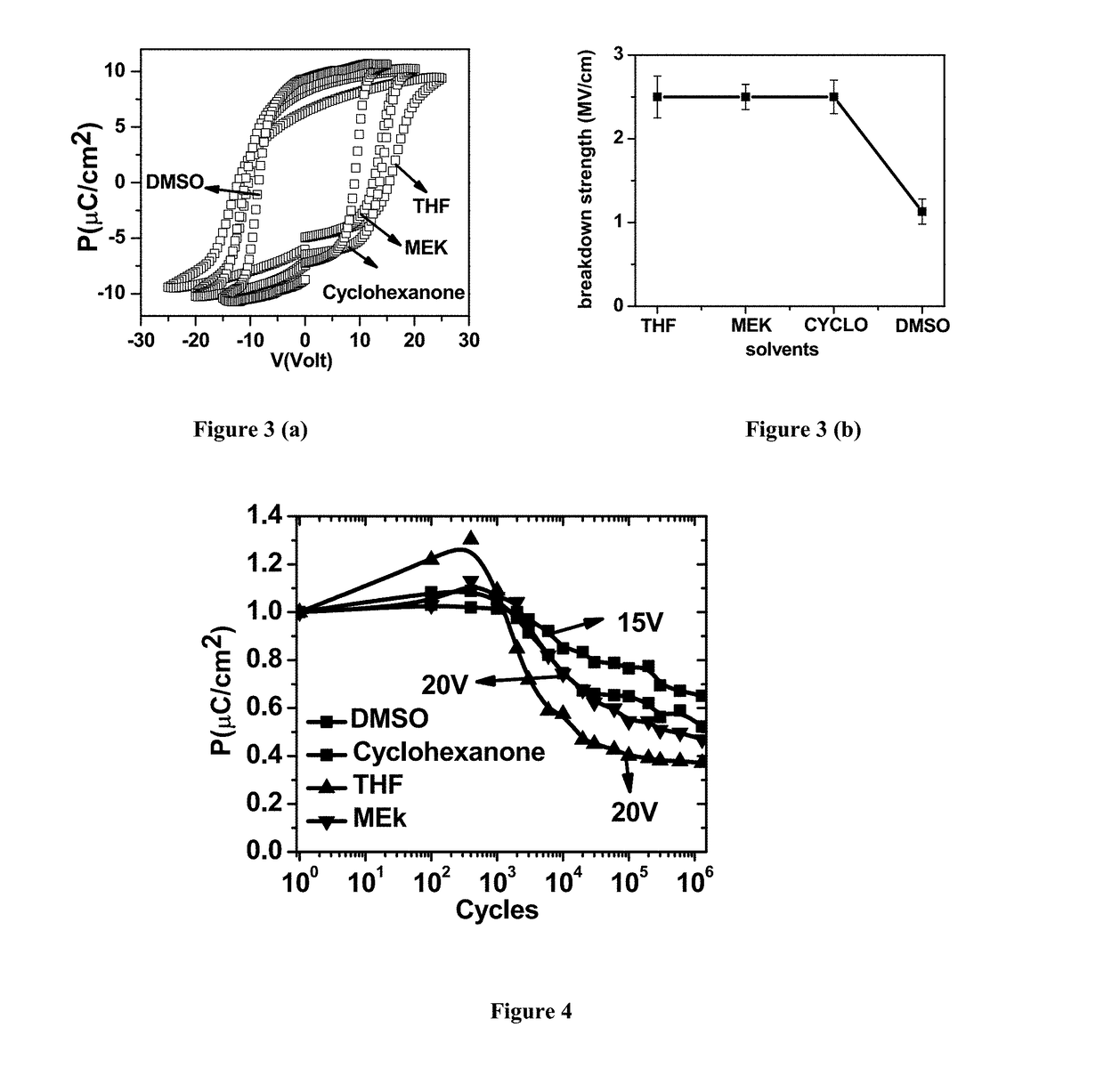

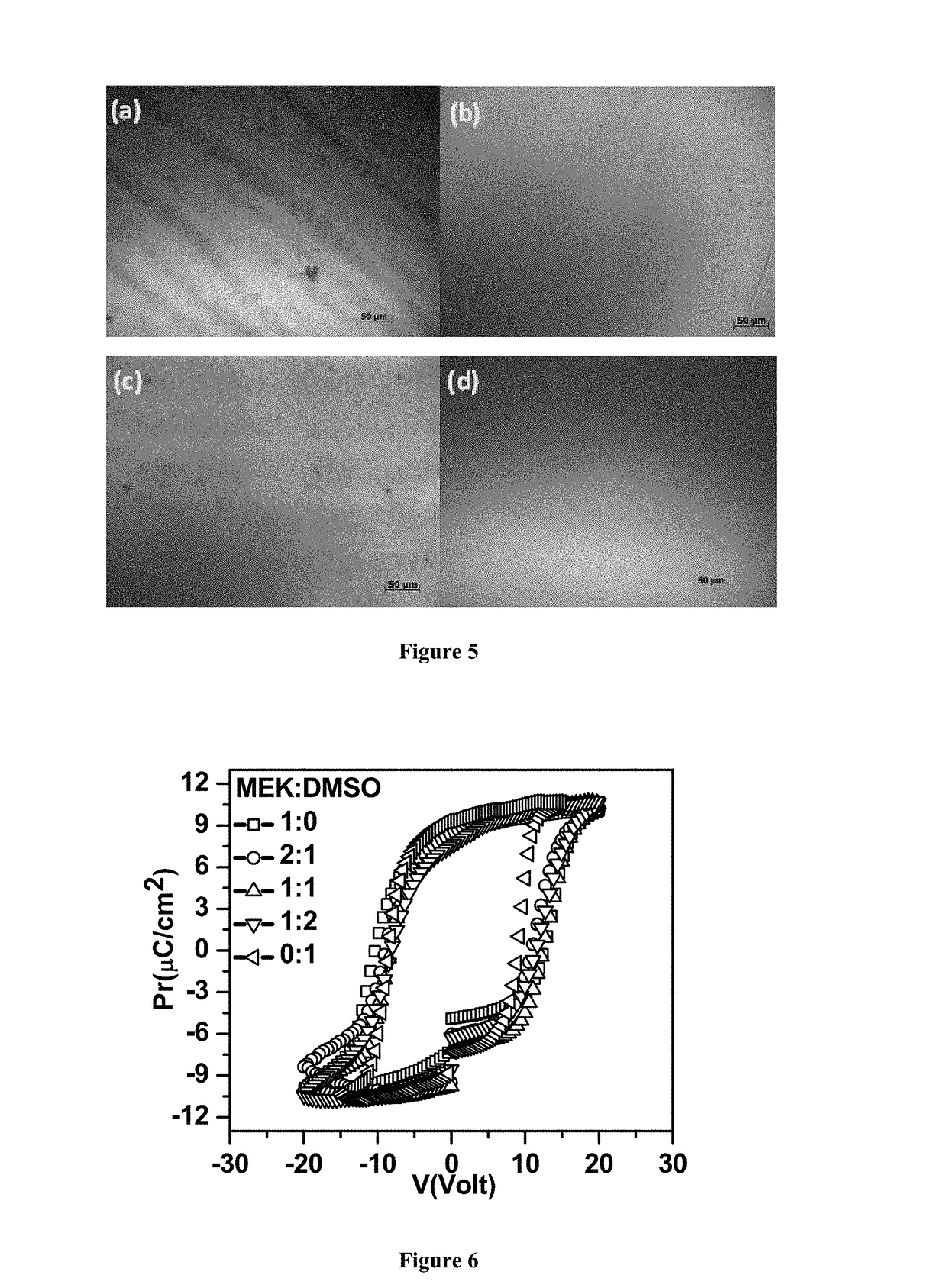

Method of fabricating high-performance poly (vinylidenedifluoride-trifluoroethylene), p(vdf-trfe) films

InactiveUS20170233597A1Simple and cost-effectiveImproved endurance stabilitySolid-state devicesPretreated surfacesLow voltageEngineering

The present invention relates to a process of fabricating P(VDF-TrFE) films by modifying the solvent composition. Two solvents MEK and DMSO were mixed in pre-determined ratios and that co-solvent mixture was used for fabricating the P(VDF-TrFE) films. By virtue of such method driven P(VDF-TrFE) films, the ferroelectric capacitors comprising of the same were found to achieve low voltage operation, thermal stability and fatigue endurance, which indicated improved ferroelectric performance of the devices. In addition, the films made by same process also yielded high piezo- and pyro-electric coefficient, indicating improved piezo- and pyro-electric performances of the devices.

Owner:INDIAN INSTITUTE OF TECHNOLOGY KANPUR

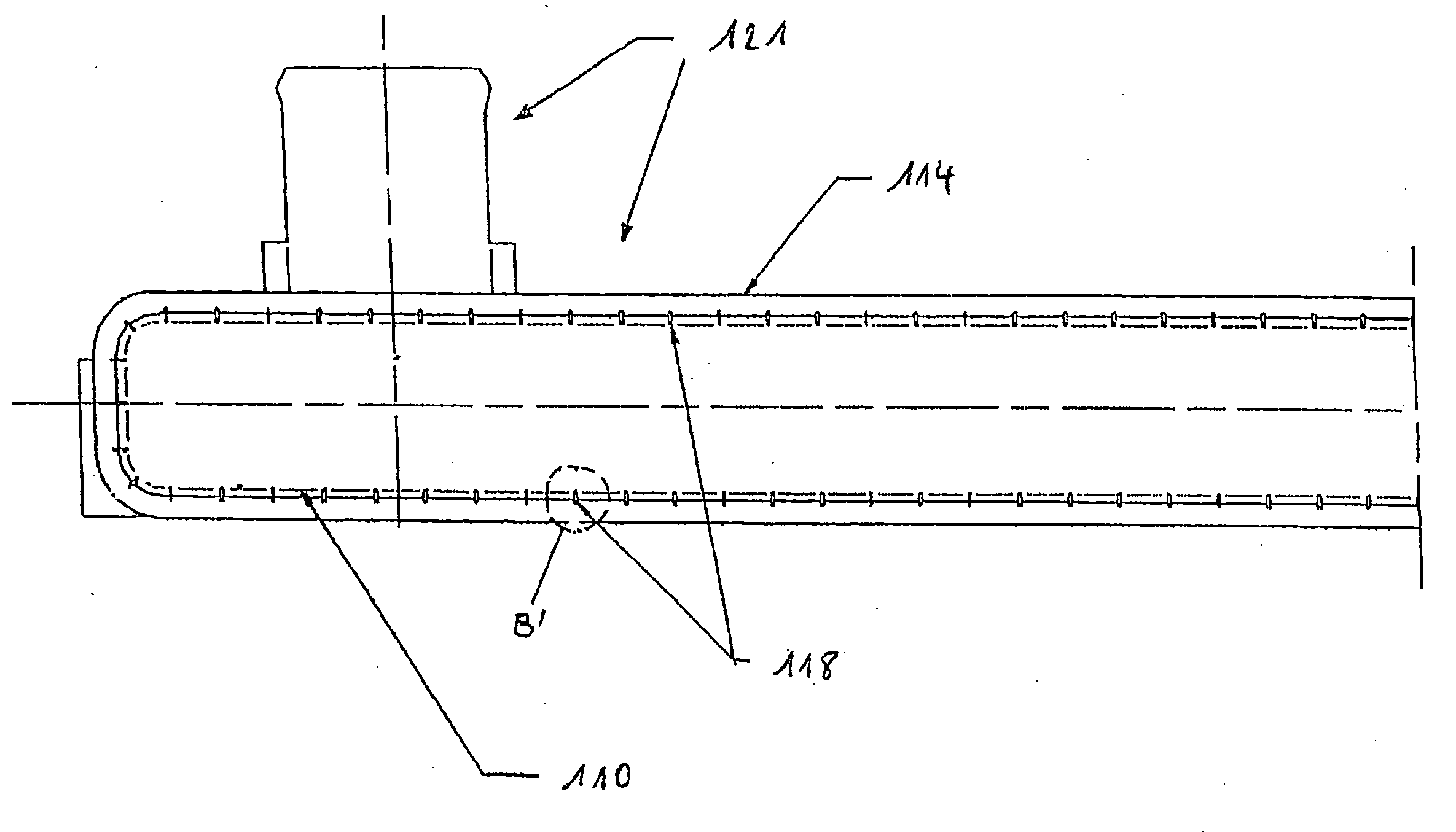

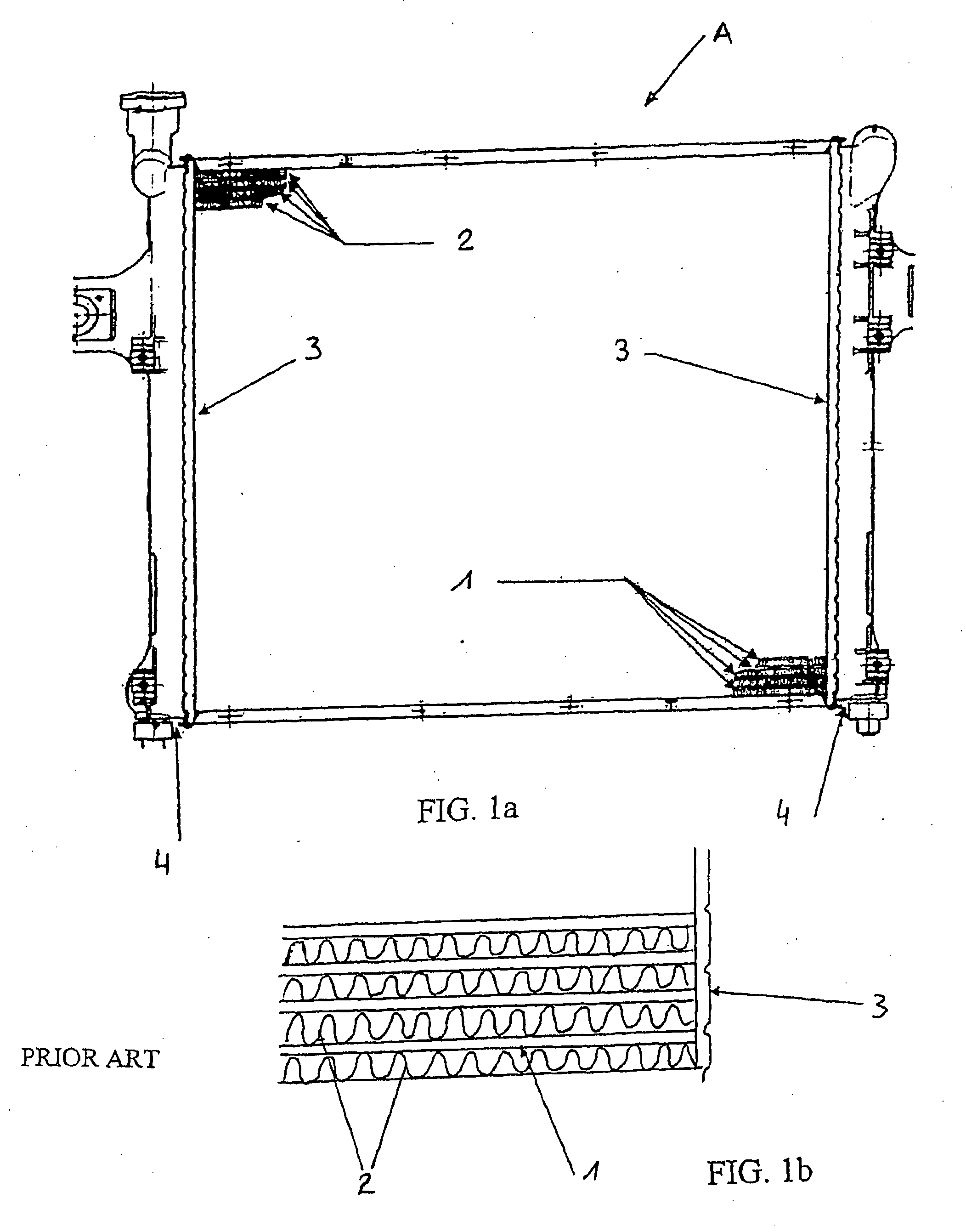

Detection system for localizing defective seals in heat exchangers

ActiveUS20090126517A1Reducing and eliminating customer returnIncrease widthDetection of fluid at leakage pointAir-treating devicesEngineeringHeat exchanger

The present invention relates to the field of automotive heat exchanger assemblies, and, in particular, assemblies with cores with headers and end tanks and / or male and female connections. The present invention also relates to a method of making a positive leak path to determine leaks prior to employment of heat exchanger assembles. The present invention further relates to a method of determining whether or not a leak seal is temporary by providing a positive leak path at the point of assembly or initial evaluation or testing a heat exchanger.

Owner:VALEO INC +1

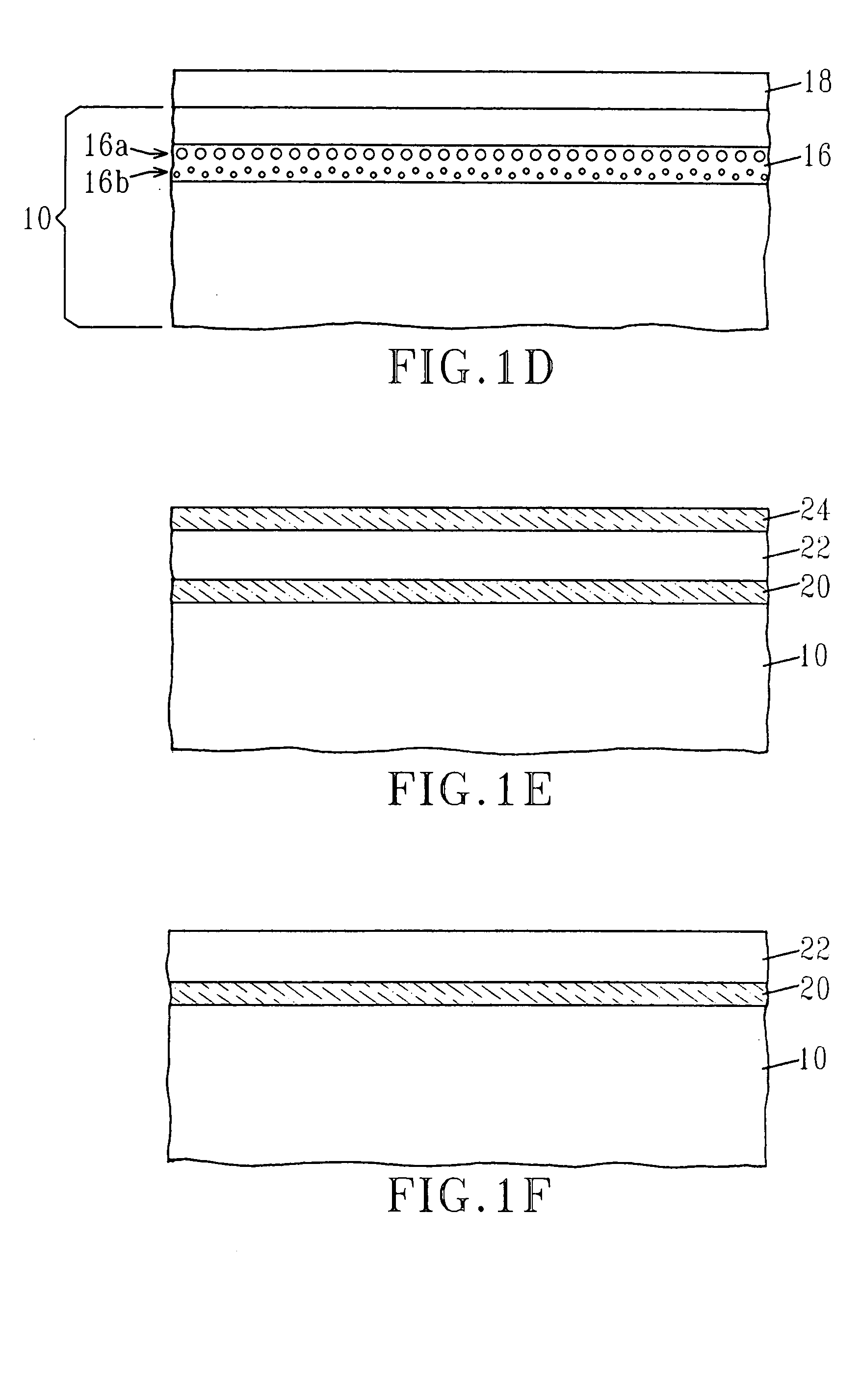

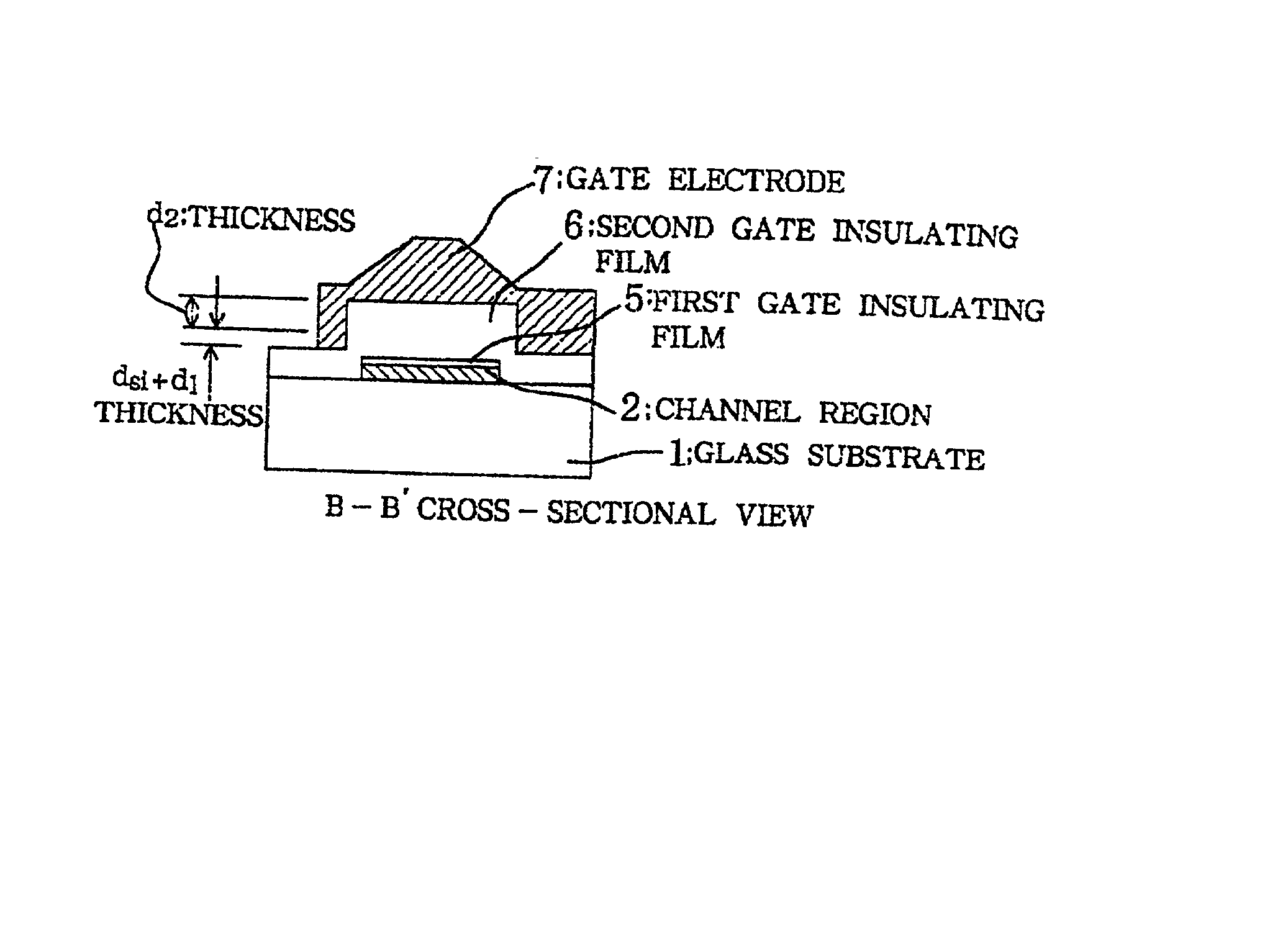

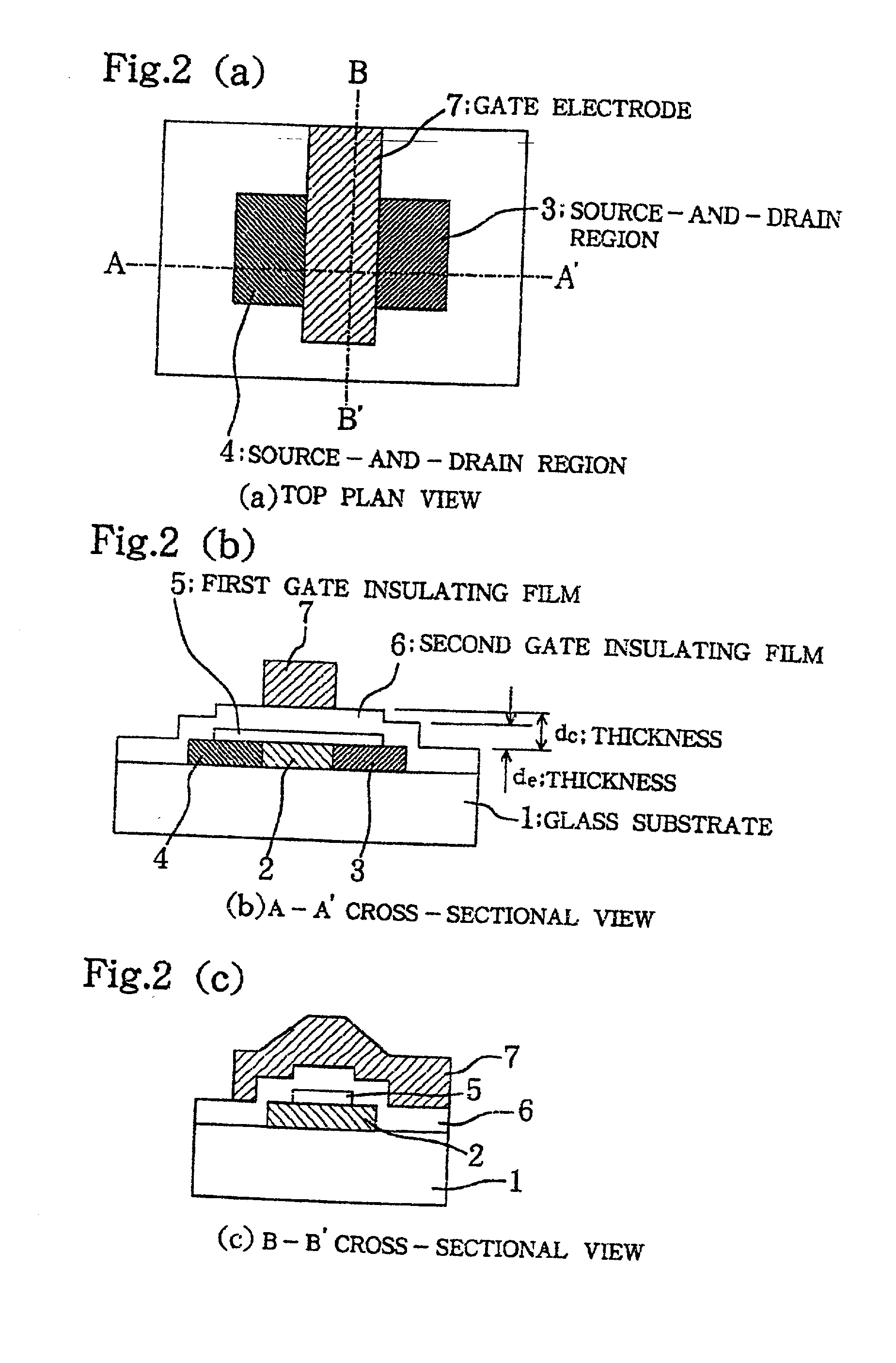

Method of manufacturing thin film transistor

InactiveUS20020072158A1Good precisionLower defect levelSolid-state devicesSemiconductor/solid-state device manufacturingMass numberEngineering

In a thin film transistor, a first insulating film on a silicon layer formed in an island on a substrate is smaller in thickness than the silicon layer so that the stepped island edges is gentle in slope to facilitate covering the island with a second insulating film. This reduces occurrence of gate leak considerably. Since the peripheral region of the stepped island is smaller in thickness than the central region above the channel, it is possible to minimize occurrence of gate electrode breakage. The silicon layer contains two or more inert gas atoms, and the atoms smaller in mass number (e.g., He) are contained in and near an interface with a silicon active layer while the atoms larger in mass number (e.g., Ar) than those smaller in mass number are contained in and near a second interface with a gate electrode.

Owner:GOLD CHARM LTD

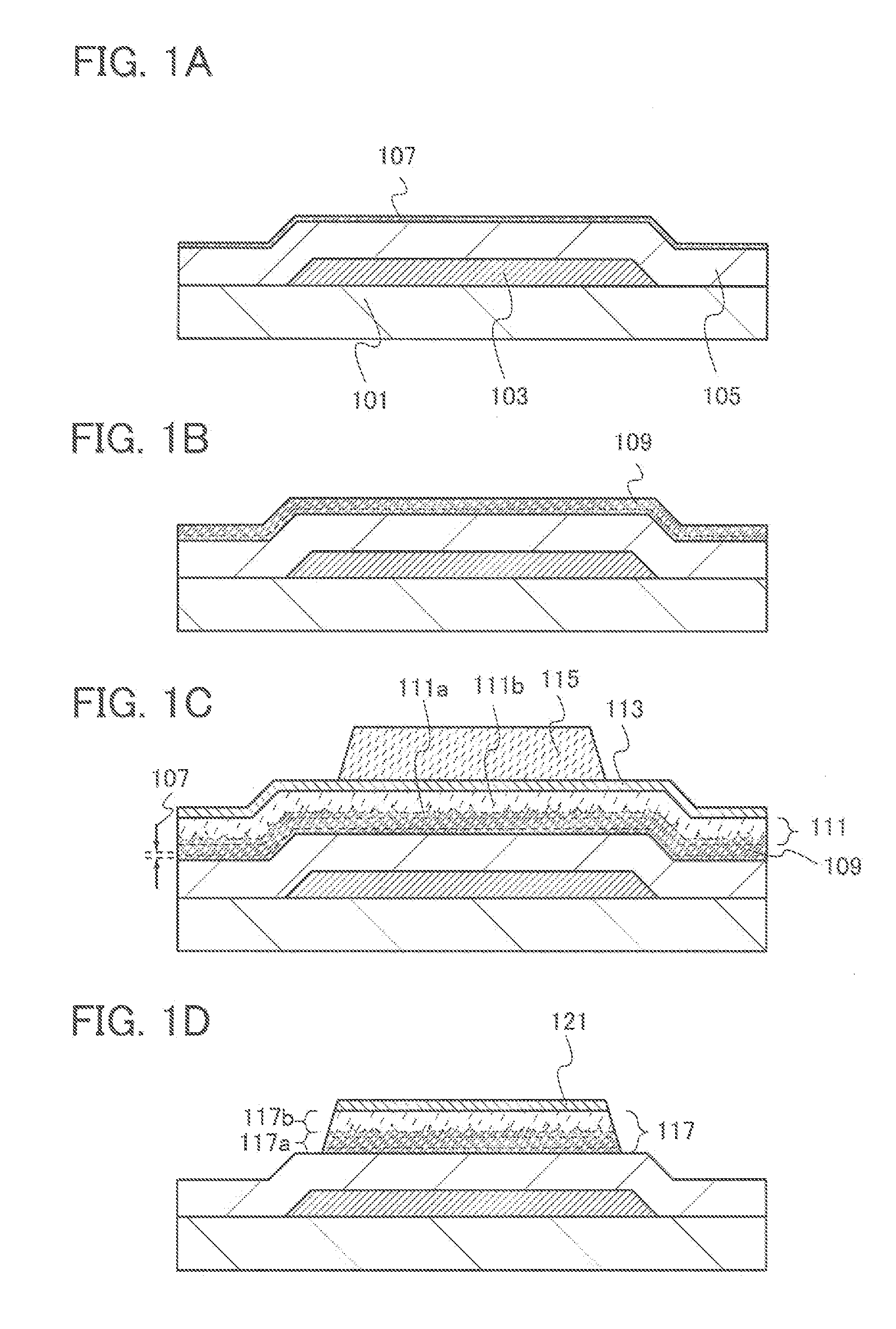

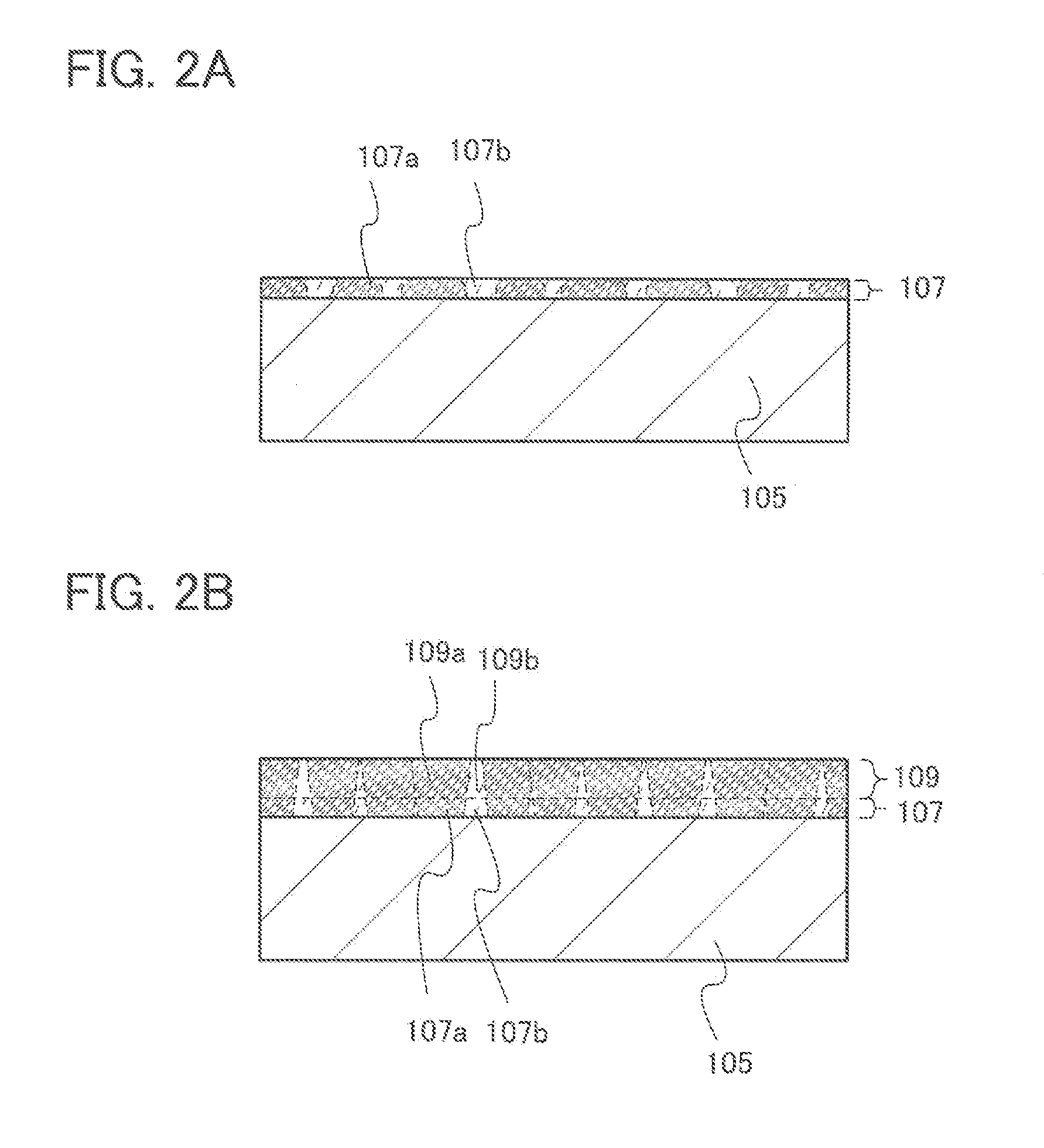

Thin film transistor and manufacturing method thereof

InactiveUS20110204364A1High currentLower average currentTransistorSemiconductor/solid-state device manufacturingProduction rateOxide thin-film transistor

A method for manufacturing a thin film transistor having high electric characteristics with high productivity. In the method for forming a channel region of a dual-gate thin film transistor including a first gate electrode and a second gate electrode which faces the first gate electrode with the channel region provided therebetween, a first microcrystalline semiconductor film is formed under a first condition for forming a microcrystalline semiconductor film in which a space between crystal grains is filled with an amorphous semiconductor, and a second microcrystalline semiconductor film is formed over the first microcrystalline semiconductor film under a second condition for promoting crystal growth.

Owner:SEMICON ENERGY LAB CO LTD

Laser cladding process

ActiveCN107723702AReduce temperature gradientImprove organizationMetallic material coating processesAlcoholLaser processing

The invention discloses a laser cladding process. The laser cladding process comprises the following steps: putting YCF101 powder in a drying box, drying the YCF101 powder for 5h at a constant temperature of 80 DEG C, then pouring the YCF101 powder into a laser cladding powder feeder, and performing powder feeding coaxially for cladding; grinding a substrate, and cleaning the substrate with alcohol to remove impurities so as to obtain a smooth to-be-cladded substrate; and performing laser cladding layer by layer on the smooth to-be-cladded substrate by employing a IPG optical fiber laser according to a certain laser processing parameter and a certain laser scanning policy. According to the laser cladding process disclosed by the invention, defect accumulation as powder is stuck to a lap joint by way of single form interlaminar lap joint is weakened effectively. The extension direction of the defects is consistent to an interlayered scanning track. By crossed longitudinal interlaminar lap of multiple groups, the defects are uniformly distributed on the cladding plane, and the defect degree is reduced effectively; the extension direction of a bath is also consistent to the scanning direction, so that the high temperature of the bath in the next layer also alleviates pores at the lap joint effectively.

Owner:NORTHEASTERN UNIV

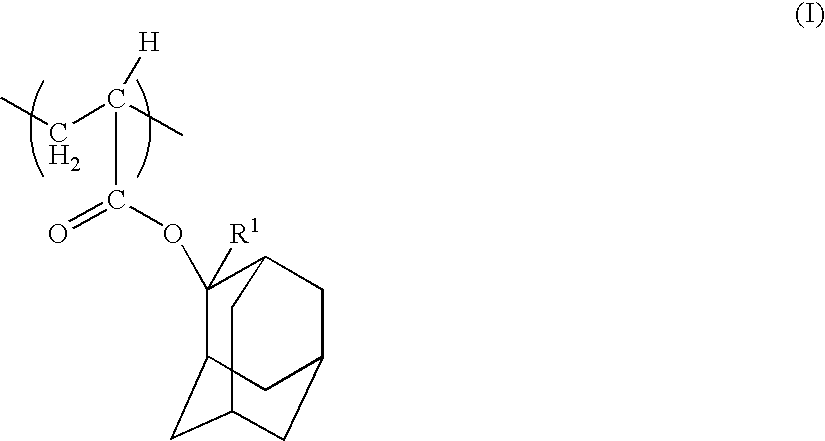

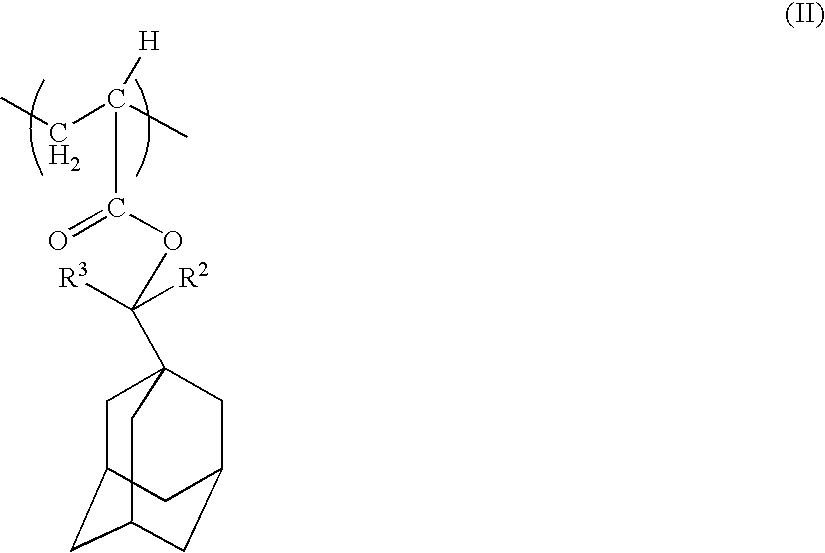

Positive resist composition and method for resist pattern formation

ActiveUS20090042129A1Excellent lithography characteristicLower Level RequirementsPhotosensitive materialsRadiation applicationsResistMethacrylate

A positive resist composition includes a resin component (A) that exhibits increased alkali solubility under the action of acid, and an acid generator component (B) that generates acid upon exposure, wherein the resin component (A) is a mixture of a copolymer (A1) that includes a structural unit (a1) derived from an acrylate ester that contains an acid-dissociable, dissolution-inhibiting group, a structural unit (a2) derived from a methacrylate ester that contains a lactone-containing monocyclic group, and a structural unit (a3) derived from an acrylate ester that contains a polar group-containing polycyclic group, and a copolymer (A2) that has a different structure from the copolymer (A1) and has a lower hydrophilicity than the copolymer (A1).

Owner:TOKYO OHKA KOGYO CO LTD