Manufacturing method for a nanocrystal based device covered with a layer of nitride deposited by CVD

a nanocrystal and nitride technology, applied in the direction of nanotechnology, nanotechnology, coatings, etc., can solve the problems of increasing the capacity of flash memories and their miniaturisation, reducing the thickness of tunnel oxide, reducing the operating voltage, and increasing the leakage current through

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

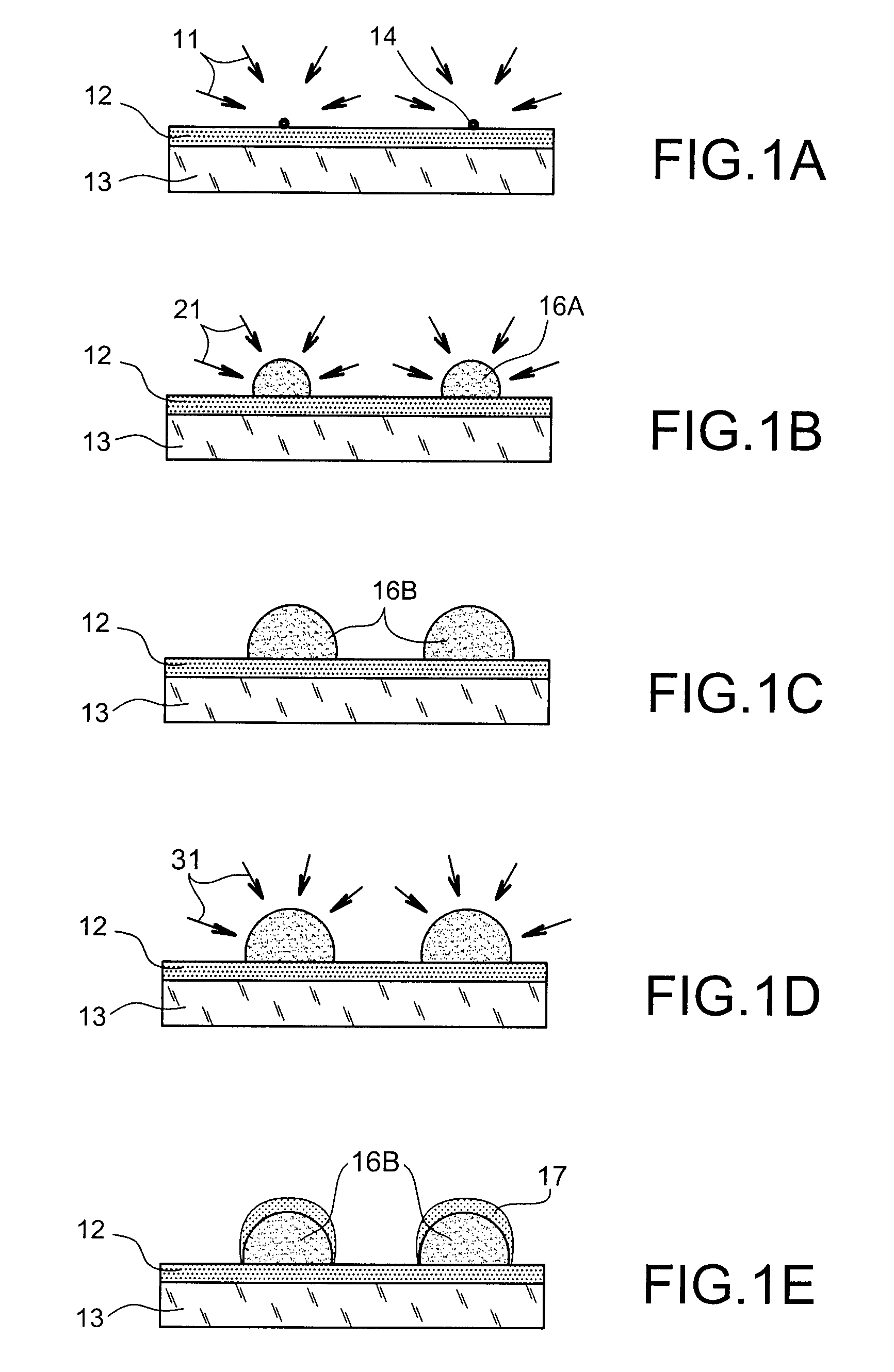

[0034]This purpose is achieved by a CVD (“Chemical Vapour Deposition”) method comprising both the creation of the nanocrystals of determined size and density and their passivation, in the form of stoichiometric nitride deposition only located on the nanocrystals. It is therefore possible to make silicon nanocrystals covered with a layer of silicon nitride.

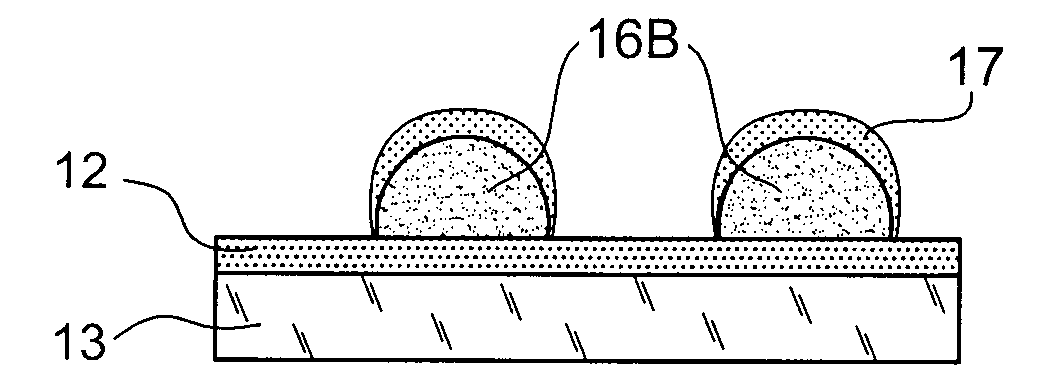

[0035]The method according to the invention is a manufacturing method for a structure comprising semi-conductor material nanocrystals on a dielectric material substrate by chemical vapour deposition (CVD), the nanocrystals being covered by a layer of semi-conductor material nitride, said method comprising:[0036]a germination step by the formation on the dielectric material substrate of stable nuclei in the form of islands, by CVD from a first gaseous precursor of the nuclei selected so that the dielectric material accepts the formation of said nuclei,[0037]a growth step by the formation of semi-conductor material nanocrystals from ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More