Method for manufacturing longitudinal double-grid metal-oxide-semiconductor element

A gate metal and oxide technology, which is applied in the field of manufacturing vertical double-gate MOS devices based on silicon-on-insulator materials, can solve the problems of small overlapping area of modulation area and light field, and the modulation efficiency needs to be improved, so as to achieve the effect of reducing the complexity of process manufacturing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

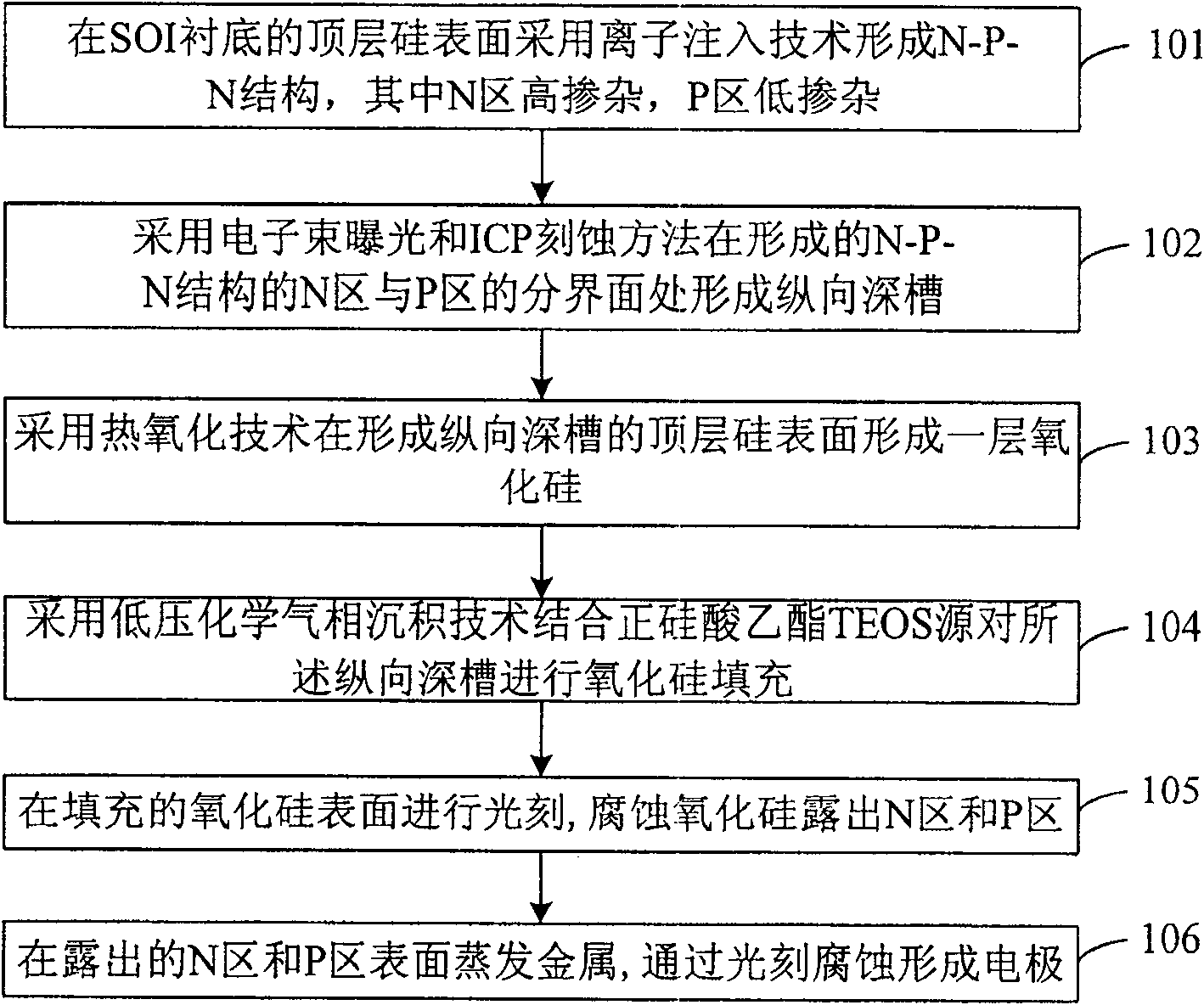

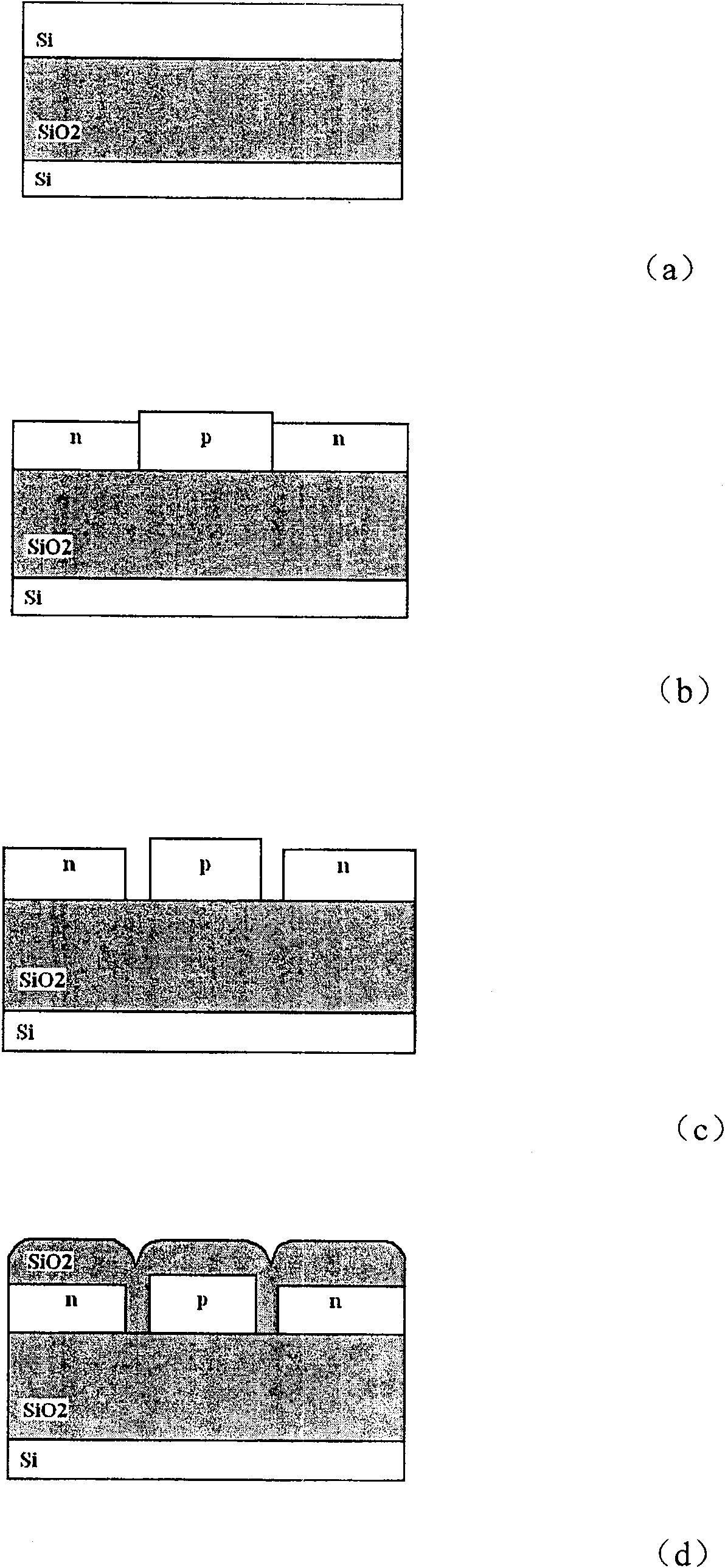

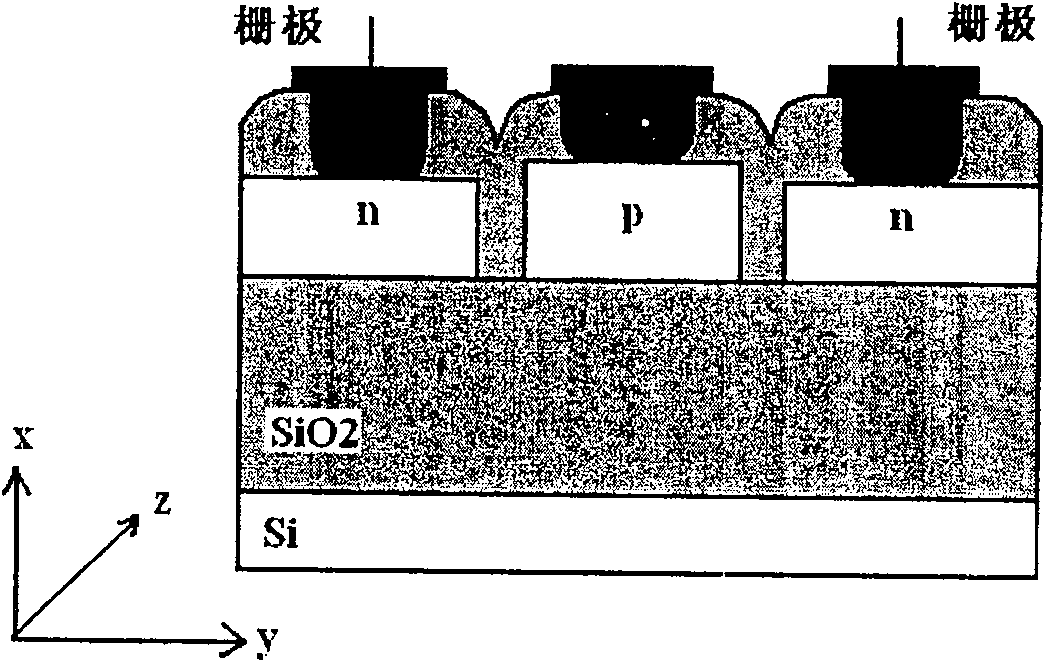

[0056] Such as figure 2 As shown, figure 2 In order to manufacture a process flow chart of a vertical dual-gate MOS device according to an embodiment of the present invention, the method specifically includes the following steps:

[0057] First, the SOI substrate is cleaned. Such as figure 2 As shown in middle figure a, figure a is a schematic diagram of the structure of the SOI substrate used in the present invention.

[0058] Secondly, ordinary photolithography is performed on the cleaned SOI substrate. It is assumed that the top silicon of the SOI substrate itself is P-type low-doped (if the top silicon concentration and type do not meet the requirements, a large-area ion implantation can be used to obtain a rational concentration). Use photoresist as a mask to perform shallow etching of silicon and ion implantation to form a highly doped N region, which is used as an ohmic contact electrode at the end. The purpose of shallow etching silicon is to leave a mark for the next e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More