Manufacturing method of bi-polar transistor array isolated by double shallow slots

A bipolar transistor, shallow trench isolation technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of high manufacturing cost, high manufacturing process, requirements, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

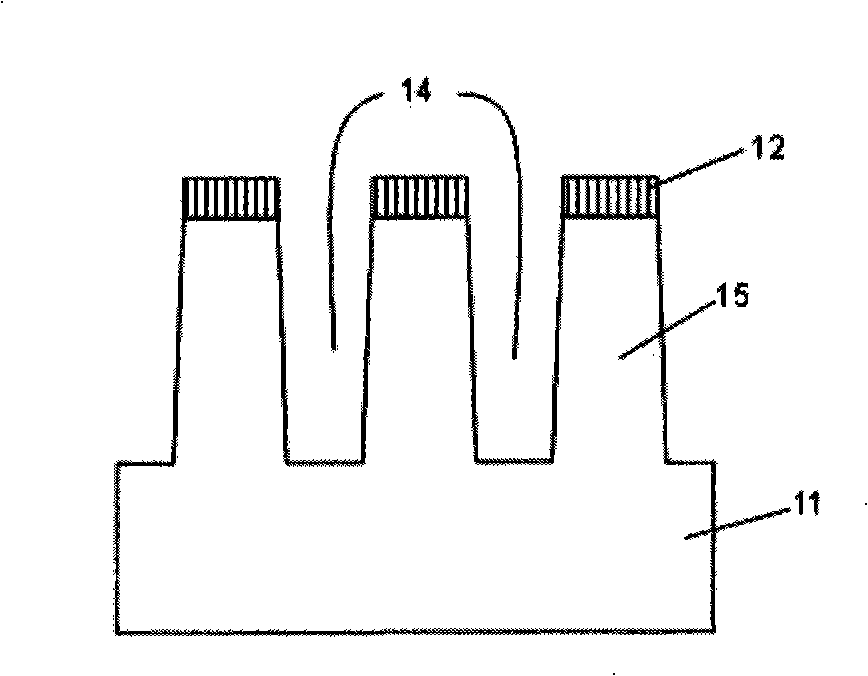

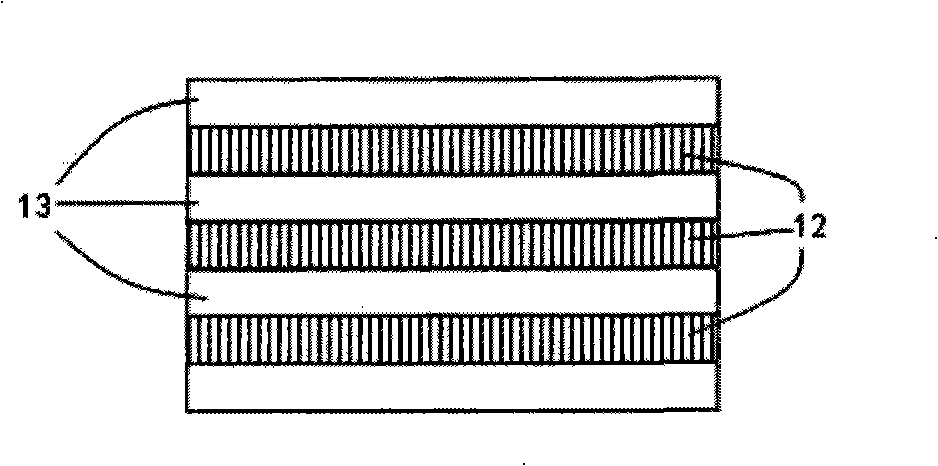

[0039] 1. On a clean p-type conductive substrate 11, an STI groove 14 with a depth of 500 nanometers is manufactured by exposure and etching processes. The part blocked by the photoresist 12 is not etched, and after etching, it is on the silicon wafer Form the protruding lines 15 that are separated from each other; the cross-sectional view of the lines formed after the above-mentioned processing is as Figure 1A As shown, the top view is as Figure 1B shown.

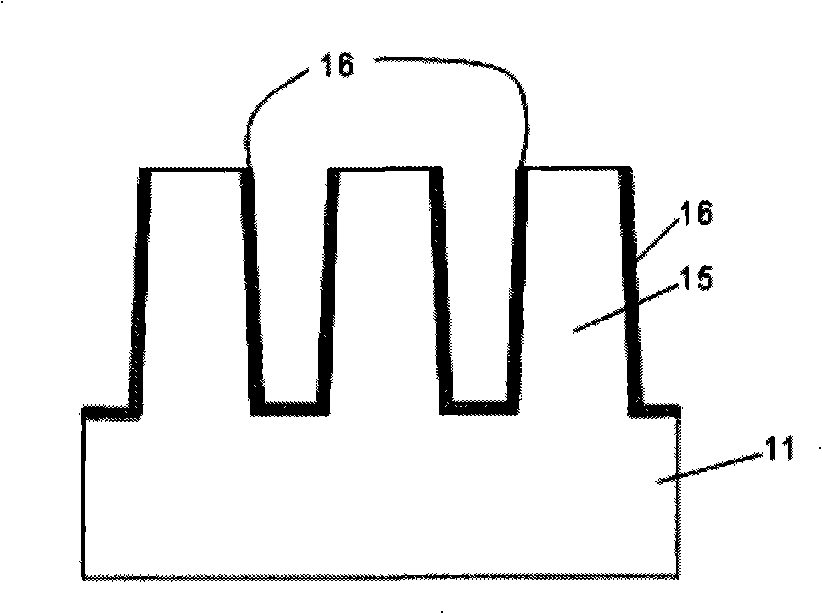

[0040] 2. After removing the glue, use chemical vapor deposition to uniformly deposit the As glass film 16 on the top of the line 15, the side wall and the bottom of the STI groove 14; use chemical mechanical polishing to remove the As-containing glass layer 16 on the line 15. Get the cross-section and top view of the graph such as Figure 1C and Figure 1D shown.

[0041] 3. Spin the photoresist on the above-mentioned substrate with a glue-spinning machine, and the photoresist layer 18 will partly penetrate into the...

Embodiment 2

[0051] A method for manufacturing a bipolar transistor-gated PCRAM device based on the method described above.

[0052] 1. The manufacturing method of manufacturing bipolar transistor array is as embodiment 1.

[0053] 2. Deposit electrode material 24 (TiN 30nm), phase change material 25 (SiSb material 100nm) and electrode material 24 (TiN 30nm) sequentially above the bipolar transistor array obtained above, and manufacture memory cell patterns by photolithography.

[0054] 3. Through the deposition of the dielectric material 29, chemical mechanical polishing and planarization, and then photolithography on the dielectric material, holes are carved in the dielectric material, so that the upper electrode 24 of the phase change memory unit and the bit line 19 are connected by metal plugs 27 and 26 leads out, manufactures electrode 28, forms memory array, as Figure 2A shown. Figure 2A In , the projection along the 5-5 direction is as Figure 2B shown.

Embodiment 3

[0056] 1. On the p-type conductive silicon substrate 30, the STI groove 32 with a depth of 700nm is etched with a photolithography process, and the lines 31 separated from each other are formed, the cross section of which is as follows Figure 3A shown.

[0057] 2. Deposit silicon oxide 33 by vapor phase deposition, such as Figure 3B shown.

[0058] 3. Using the etch-back process, the rest of the silicon oxide at the bottom of the STI groove is etched and removed, such as Figure 3C shown.

[0059] 4. Phosphorus-containing glass 34 is deposited by chemical vapor deposition, adopting a method similar to that of 3 to 5 steps in Example 1 to remove the phosphorus-containing glass at the top and notch of the STI, forming such as Figure 3D The cross-sectional view shown.

[0060] 5. Perform annealing treatment in argon protection, the annealing temperature is 1100 ° C for 5 hours, so that the phosphorus atoms in the material can fully diffuse into the line 31, forming a heavi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More