Glass passivating technique process for semi-conductor device with silicon large diameter round wafer

A glass passivation and large-diameter technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems affecting long-term working life, difficulty in overall planning, power device reduction of power indicators, etc., to achieve electrical parameters and reliability Performance optimization, simple technical method and remarkable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

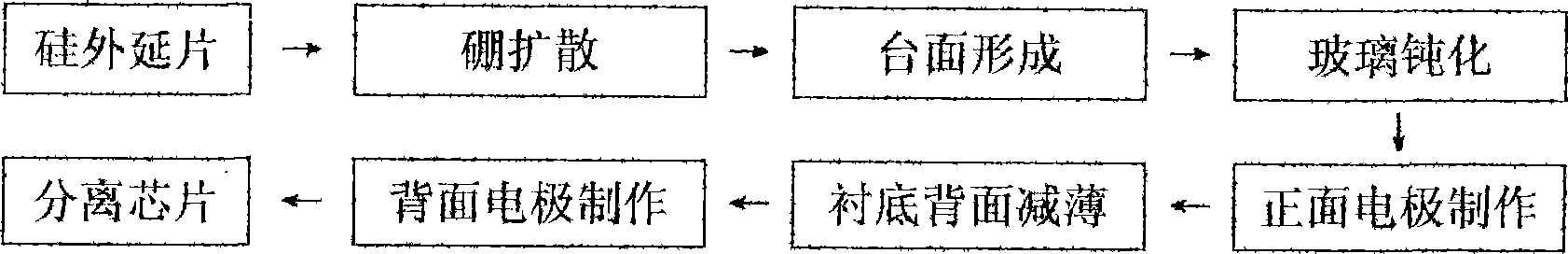

Method used

Image

Examples

Embodiment 1

[0020] Embodiment 1 Silicon switch diode glass passivation technology and method

[0021] Silicon substrate diameter: 3 inches

[0022] Original thickness of silicon wafer: 480μm

[0023] Chip size on silicon substrate: mesa height 30μm~35μm

[0024] Mesa diameter Φ45μm~Φ50μm

[0025] The distance between adjacent chips is 350μm

[0026] P + N - Junction depth 5μm~5.5μm

[0027] N-layer thickness 24μm~25μm

[0028] Process steps:

[0029] 1. Strict chemical cleaning and drying of the silicon wafers etched on the device table;

[0030] 2. Fabricate glass passivation film by scraping method, and in P + Open the electrode contact window on the surface to make the front electrode system;

[0031] 3. Use a grinding wheel dicing machine with a knife width of 10-20 μm, and the depth of the knife is 35 μm for the height of the table, and cut the glass film groove between the adjacent chips on the...

Embodiment 2

[0034] Embodiment 2 Silicon varactor glass passivation technology method

[0035] Silicon substrate diameter: 3 inches

[0036] Original thickness of silicon wafer: 480μm

[0037] Chip size on silicon substrate: mesa height 8μm~10μm

[0038] Mesa diameter Φ105μm~Φ110μm

[0039] The distance between adjacent chips is 350μm

[0040] P + N - Junction depth 0.6μm~0.8μm

[0041] N-layer thickness 2μm~2.5μm

[0042] Process steps:

[0043] 1. Strict chemical cleaning and drying of the silicon wafers etched on the device table;

[0044] 2. Make glass passivation film by scraping method;

[0045] 3. Use a photolithography mask with a line width of 15 μm and an outer frame size of 365 μm×365 μm to carve a glass film layer groove with a strip width of about 25 μm between adjacent chips, subject to the engraved clean glass film;

[0046] 4. In P + The electrode contact window is opened on the surfa...

Embodiment 3

[0049] Example 3 Glass Passivation Technology and Method of Silicon Pin ESC Attenuation Diode

[0050] Silicon substrate diameter: 3 inches

[0051] Original thickness of silicon wafer: 480μm

[0052] Chip size on silicon substrate: Mesa diameter Φ90μm~Φ95μm

[0053] Mesa height 110μm~115μm

[0054]The distance between adjacent chips is 400μm

[0055] P + N - Junction depth 5μm~5.5μm

[0056] N-layer thickness 70μm~80μm

[0057] Process steps:

[0058] 1. Strict chemical cleaning and drying of the silicon wafers etched on the device table;

[0059] 2. Use a box-shaped screen printing mask with a line width of 20 μm and an outer frame size of 420 μm×420 μm. The real part of the mask covers the centerline of the adjacent die, and the imaginary part of the mask exposes the device chip for passivation protection. area;

[0060] Apply the glass paste by scraping method, remove the mask after drying to thermofo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More