Semiconductor packaging base plate and manufacturing method thereof

A technology for encapsulating substrates and semiconductors, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc. Effects of thickness, avoidance of stress concentration, and optimum bonding strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

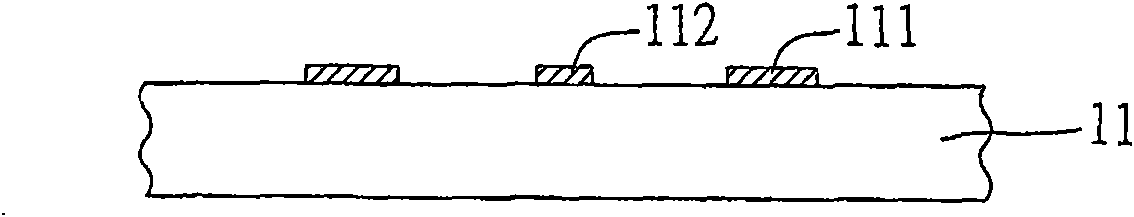

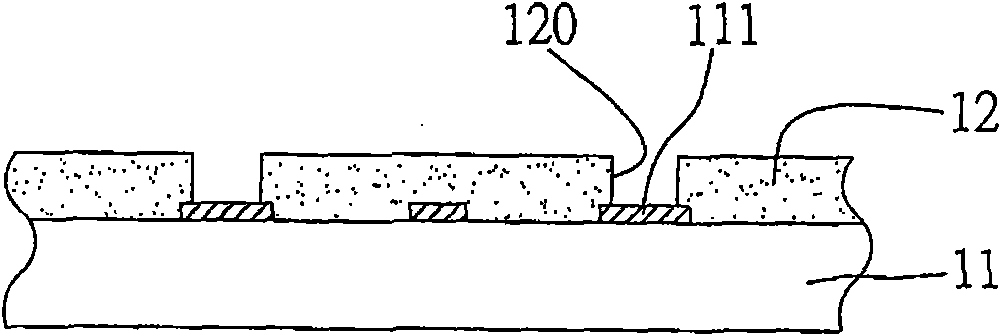

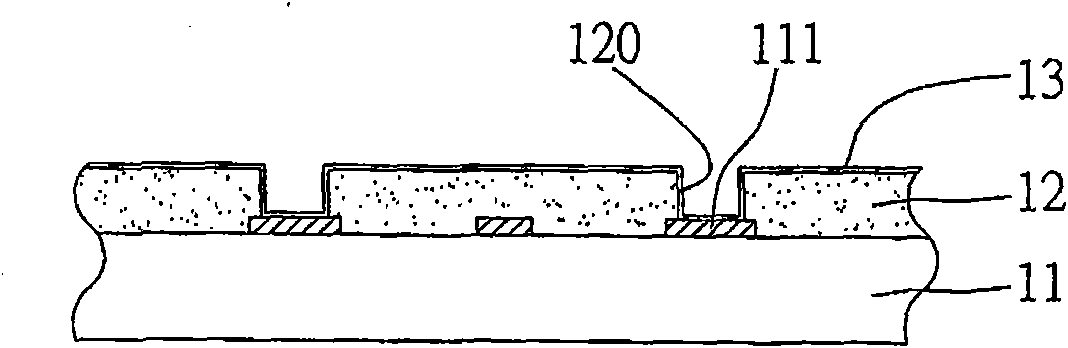

[0044] see Figure 2A to Figure 2J , are the semiconductor package substrate and the manufacturing method thereof of the present invention.

[0045] see Figure 2A Firstly, a substrate body 20 with a dielectric layer 21 formed on at least one surface is provided, and a conductive layer 22 is formed on the dielectric layer 21, and the conductive layer 22 is mainly used as a current conduction path required for electroplating metal materials described later, which It can be composed of metal or deposited several layers of metal layers, such as single-layer or multi-layer structures selected from copper, tin, nickel, chromium, titanium, copper-chromium, etc., or can use polyacetylene, polyaniline or organic sulfur polymers, etc. Conductive polymer materials.

[0046] see Figure 2B A first resist layer 23 is formed on the conductive layer 22 by means of printing, spin coating or bonding, and a plurality of openings 230 are formed on the first resist layer 23 through patterning p...

no. 2 example

[0061] see Figure 3A and Figure 3B , is another implementation method of the present invention, which is different from the previous embodiment in that the opaque area of the photomask completely covers each of the conductive pillars and includes the regions between the conductive pillars.

[0062] Such as Figure 3A As shown, it is a continuation of the first embodiment Figure 2I The opaque region 281' of the photomask 28 completely covers each of the conductive pillars 26 and the area between each of the conductive pillars 26, so that the insulating protection layer 27 not covered by the opaque region 281 exposure.

[0063] see Figure 3B , and then remove the surface of the insulating protection layer 27 that has not been exposed, and then form an exposed portion that is a recessed region 272 on the surface of the insulating protection layer 27. The recessed region 272 does not penetrate through the insulating protection layer 27 and exposes each of the The top su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More