Process for electrodeposition of copper chip to chip, chip to wafer and wafer to wafer interconnects in through-silicon vias (TSV)

A technology of electrodeposition and process, which is applied in the field of high-purity copper electrolysis to form a conductor structure in through-silicon vias, which can solve problems such as wafer bending or deformation, uneven deposition, deformation, etc., to minimize stress and avoid dopants and the effect of stomata

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

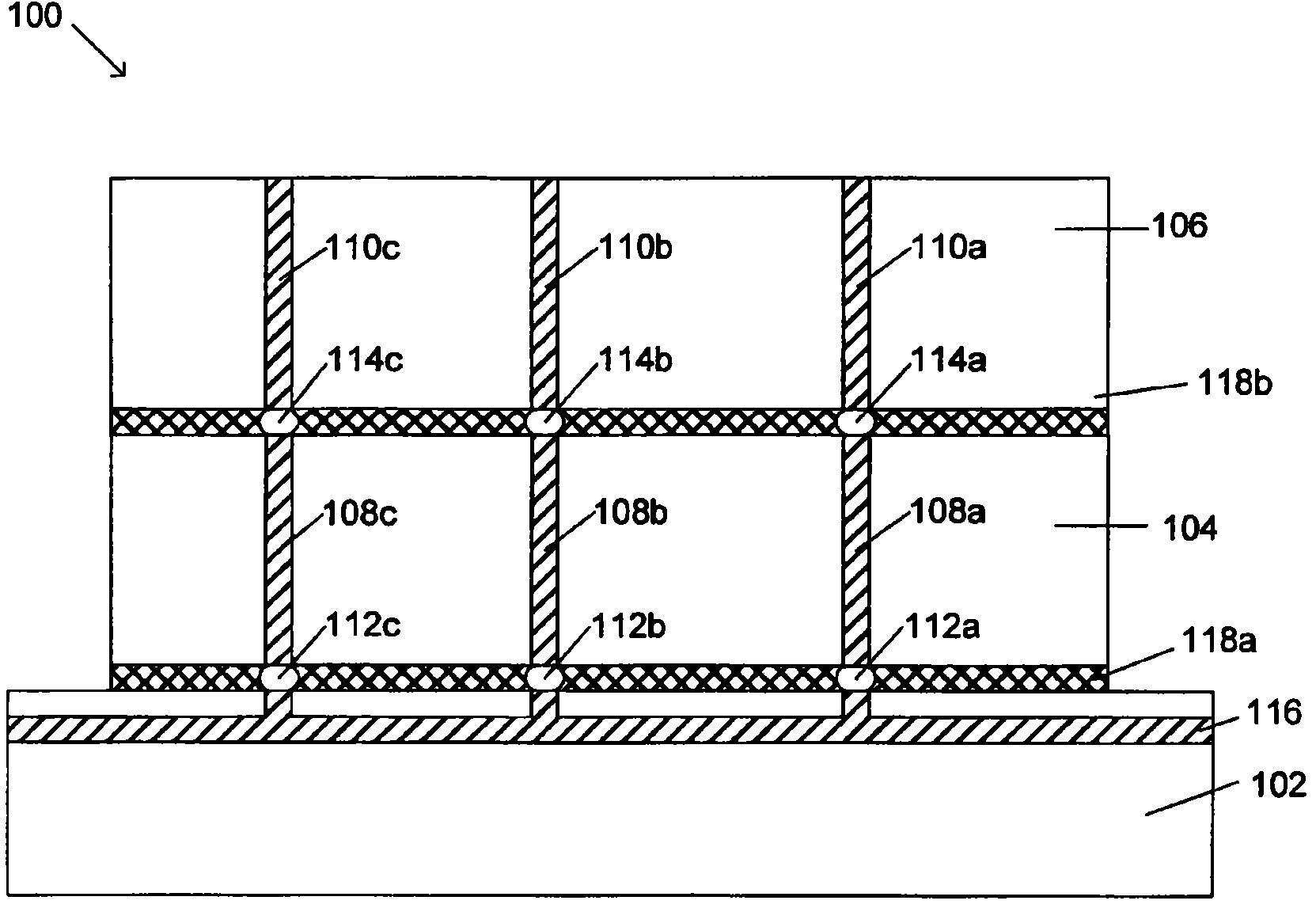

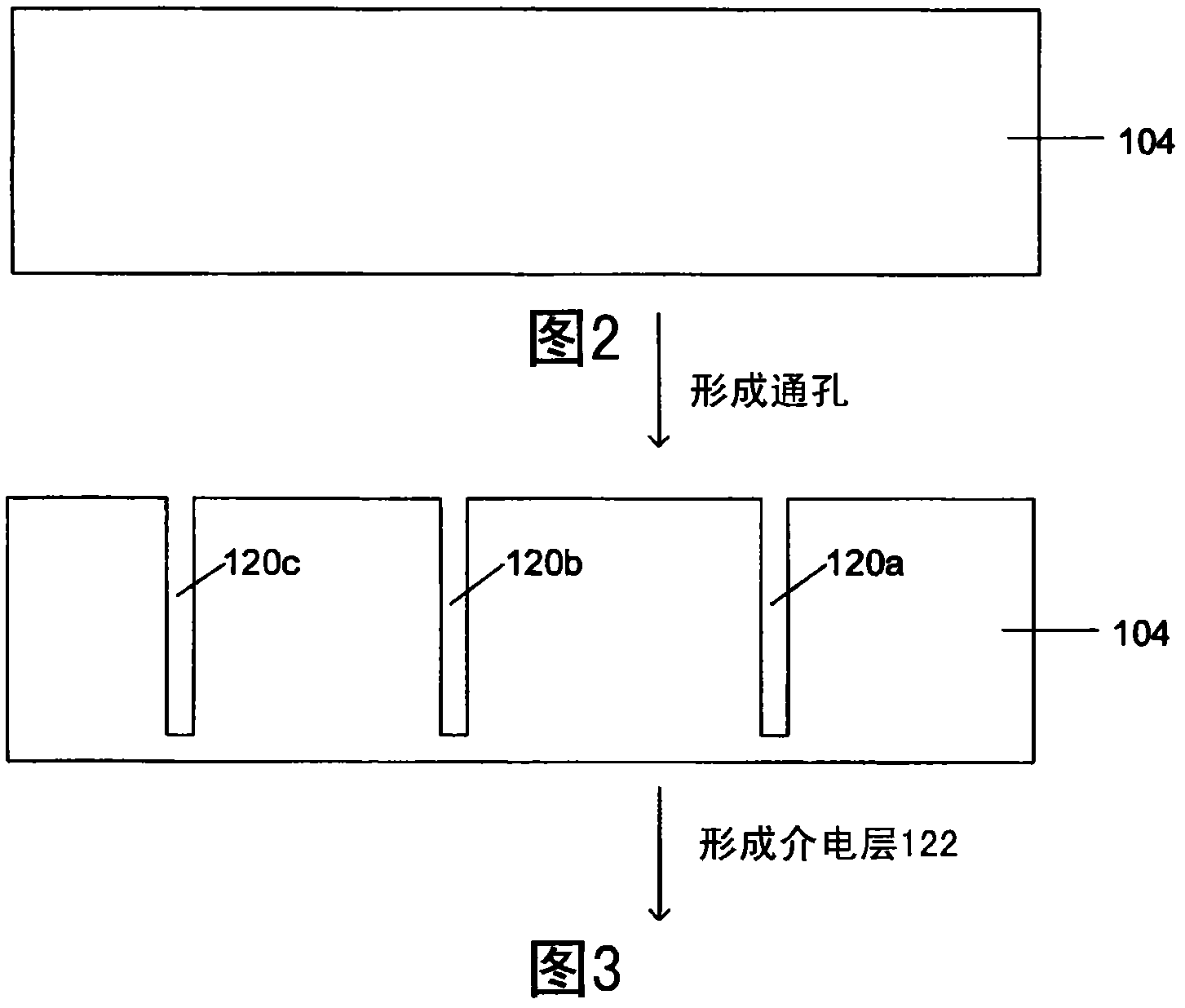

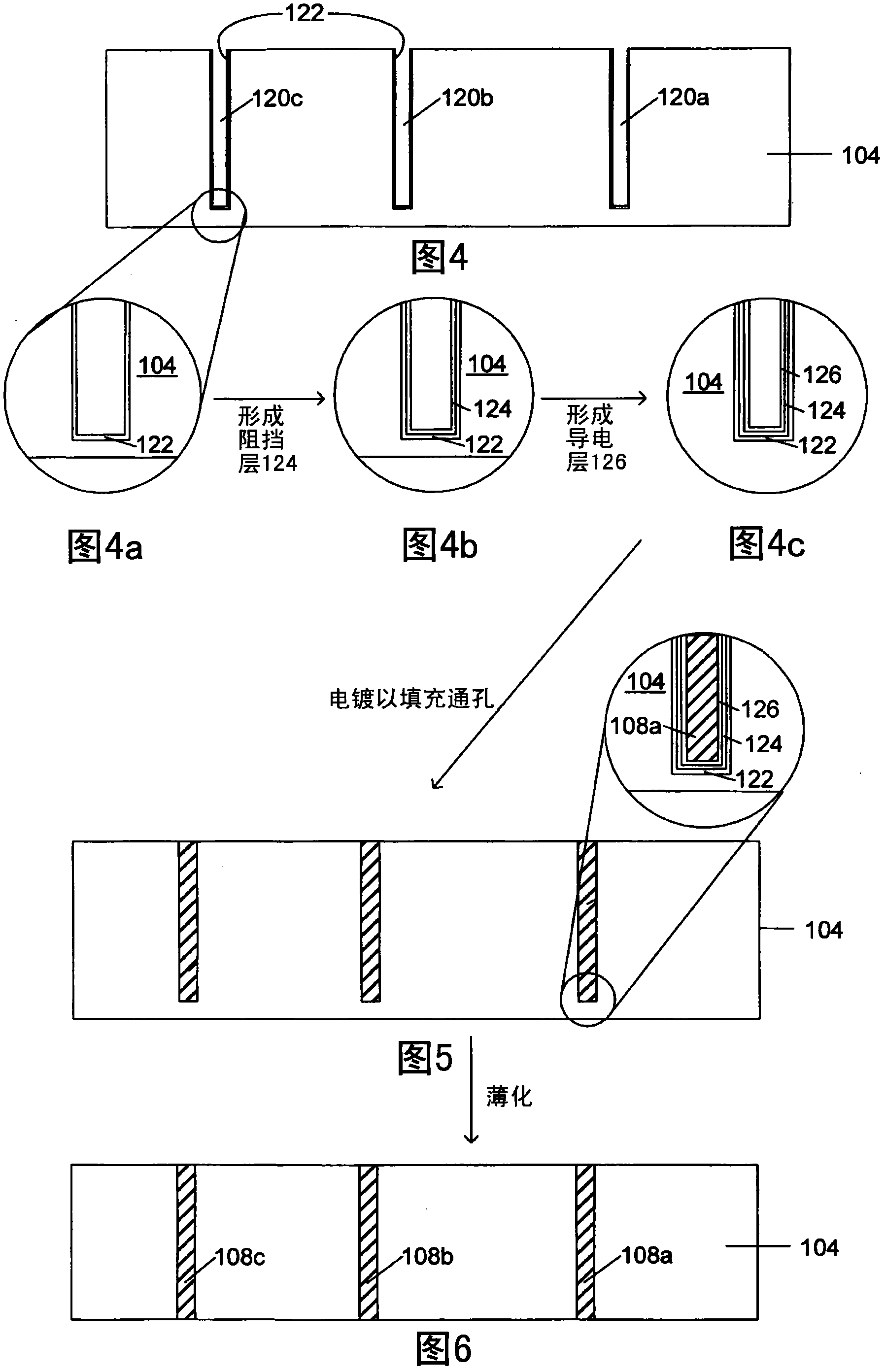

[0173]To create TSVs filled with high-purity copper deposits, the wafer is provided with vias with a diameter of approximately 10 microns and a depth of approximately 50 microns. The via is initially coated with a dielectric layer of silicon dioxide formed from high temperature oxidation of the inner sidewalls of the via. The dielectric layer on the inner sidewalls of the via is then coated with a diffusion barrier formed by sputtering from tantalum nitride. Subsequently, the diffusion barrier layer was coated with a copper base metal layer by a sputtering process, wherein the thickness of the copper base deposition layer was about 0.1 microns. The wafer was then dipped into the copper deposition bath described below in which the wafer was connected as a cathode and included an insoluble anode. The vias were filled with high purity copper by electrodeposition from a cell having the following composition to form TSVs according to the invention.

[0174]

[0175] The high-p...

example 2

[0181] By using different electroplating methods of the cells disclosed above according to the present invention (these different electroplating methods or using similar cells but without the addition of Fe 2+ / Fe 3+ ions, or using a similar cell but with a soluble copper anode) where a pulsed current with the parameters shown in the table below was applied:

[0182]

[0183] The copper stress in the as-deposited TSV is:

[0184]

[0185] The internal stresses were measured after being deposited without a post annealing step. The measurements are the warpage and bow of the through-hole wafer (laser measurement). The facility used is a KLA-TENCOR FLX-2320 film stress measurement system, the thickness of the copper film is 1 micron, and the thickness of the wafer is 750 microns.

[0186] It is clearly shown by the data of Example 2 that when the TSVs are filled according to the invention, a significantly reduced and more significantly consistent stress level is obtained...

PUM

| Property | Measurement | Unit |

|---|---|---|

| composition ratio | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More