Single-ended input and differential output parallel dual-frequency low noise amplifier and design method thereof

A low-noise amplifier, single-ended input technology, applied in differential amplifiers, DC-coupled DC amplifiers, improved amplifiers to reduce noise effects, etc., can solve problems such as high loss, increased design difficulty, and low noise figure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with the accompanying drawings.

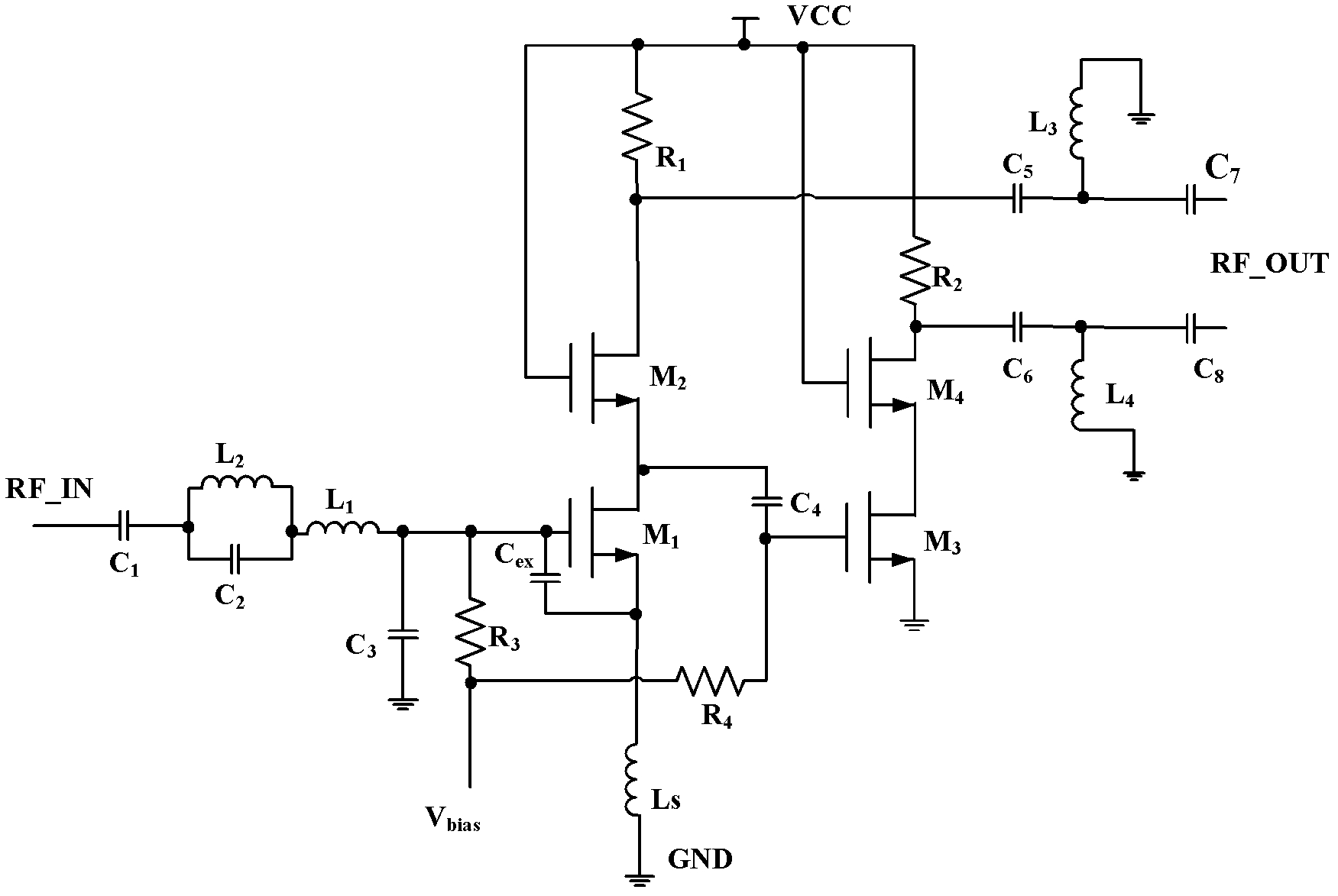

[0044] A parallel dual-frequency low noise amplifier with single-ended input and differential output of the present invention, such as figure 1 As shown, it includes the main amplifier circuit with single-ended input, source coupling inductor, input matching network, single-ended to differential output stage and output network.

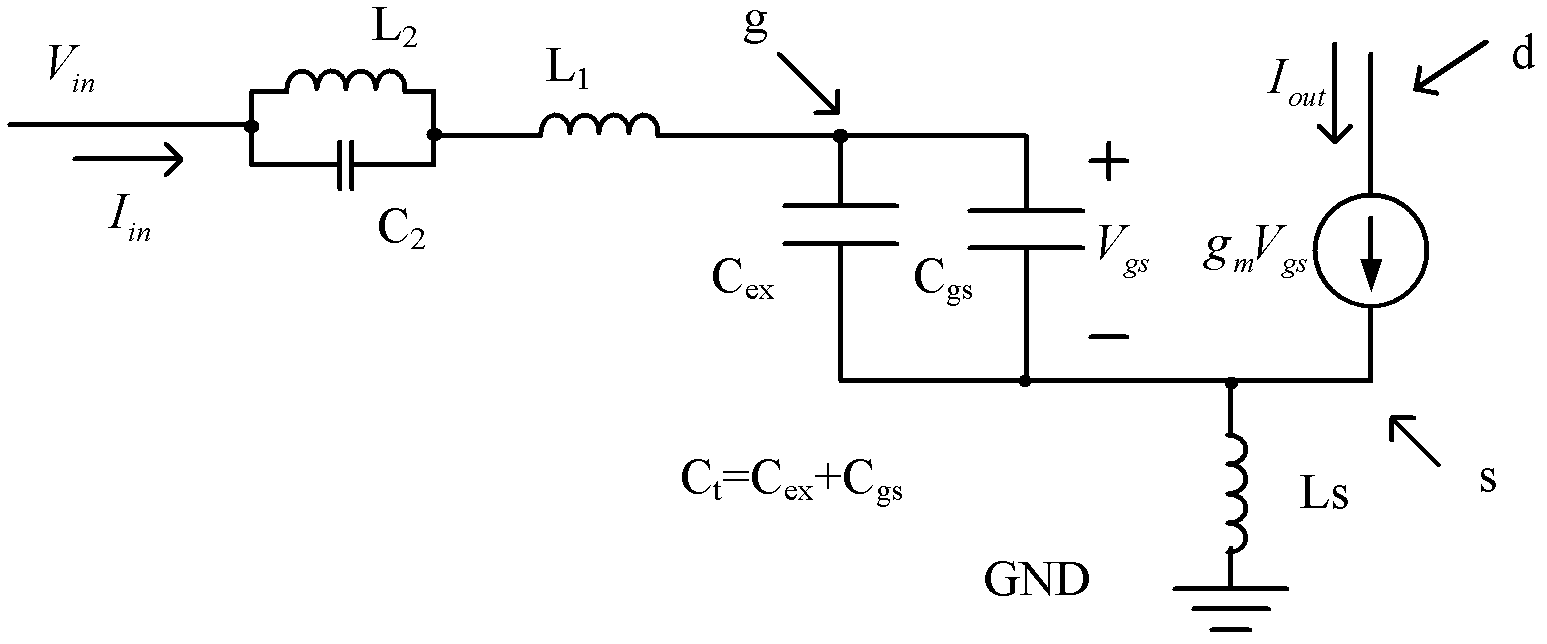

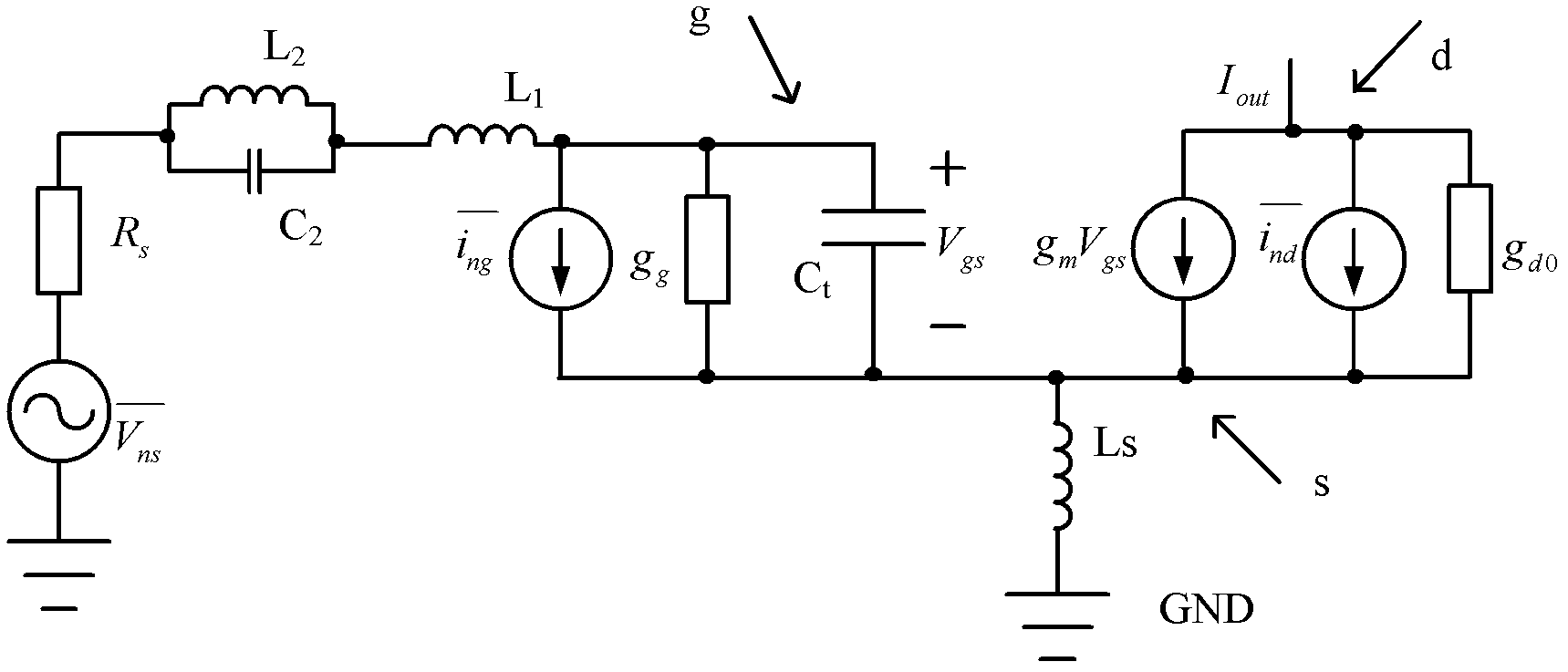

[0045] The main amplifier circuit with single-ended input includes a first common-source transistor M 1 , the first common gate transistor M 2 , the third resistor R 3 , the fourth resistor R 4 , the third capacitor C 3 and in the first common source transistor M 1 The gate-source capacitance between the gate and source C ex . The first common source transistor M 1 The gate of the input matching network with the first inductance L 1 Connected, the source is grounded through the source coupling inductor Ls, and the drain is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More