Method for fabricating organic devices

A technology of organic devices and organic semiconductor layers, applied in the field of manufacturing organic devices, can solve problems such as uneven thickness of metal contacts, limiting circuit frequency, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

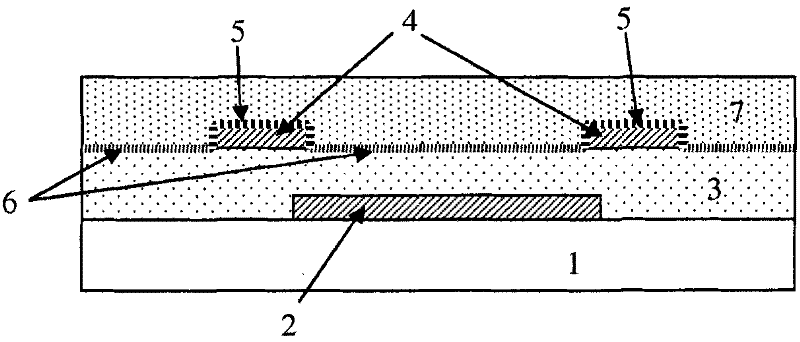

[0153] Example 1: Au Bottom Contact Transistor

[0154] Au bottom-contact organic transistors were fabricated by using a lift-off fabrication process for the formation of bottom metal contacts. In the experiments, a silicon substrate comprising a common aluminum gate and a 140 nm thick dielectric layer (silicon dioxide) was used. After cleaning the substrate provided with a patterned photoresist layer, a metallization step followed, including sputtering a 20 nm thick layer of gold and a 5 nm thick layer of aluminum. Next, perform a stripping step with acetone in an ultrasonic bath. In the transistor structure, a 20nm thick layer of gold forms the source and drain of the transistor. According to an embodiment of the invention, a 5 nm aluminum layer is used as a temporary protective layer.

[0155] After wet cleaning and UV-ozone cleaning (15 min) of the samples, a silane treatment (first surface modification layer) was performed in which PETS (phenylethyltris Chlorosilanes)...

example 2

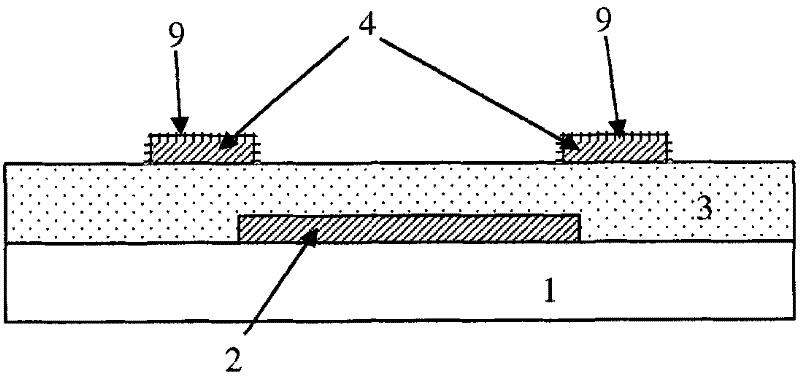

[0157] Example 2: Ag Bottom Contact Transistor

[0158] Experiments were carried out in which Ag bottom-contact transistors were fabricated according to methods of embodiments of the present invention. A metallization step is performed, consisting of providing a 15 nm thick layer of Au (used as an adhesion layer) and a 20 nm thick layer of Ag (used as a bottom contact metal, from which it can also be produced by a partial chemical reaction between silver and an electron acceptor). into a stack of "injection layers"). A 5 nm thick Al protective layer was then provided on the Ag layer. Patterning of the Au adhesion layer, Ag layer and Al protection layer was performed using a single lift-off step. After UV-ozone cleaning and silanization (formation of the first surface modification layer), within 10 minutes by mixing with diluted hydrochloric acid (1 volume concentrated hydrochloric acid + 5 volumes 2 O) to remove the Al protective layer. Next, the surface of the Ag layer is...

example 3

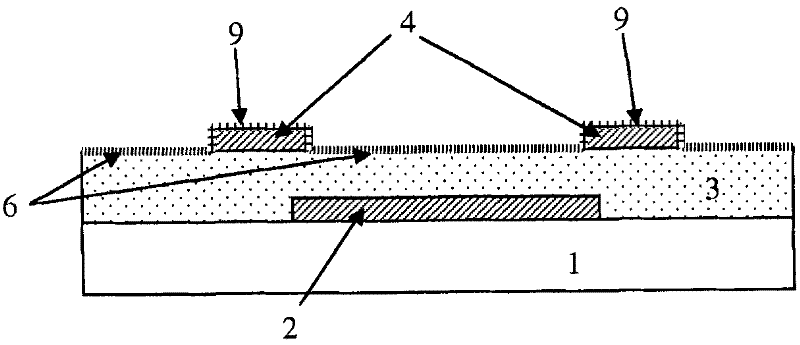

[0160] Example 3: Pd Bottom Contact Transistor

[0161] Experiments were carried out in which Pd bottom contact transistors were fabricated according to methods of embodiments of the present invention. A metallization step was performed consisting of providing a stack of a 5nm thick layer of TiW (used as an adhesion layer) and a 20nm thick layer of Pd (used as bottom contact metal). A 5 nm thick Al protective layer was then provided on the Pd layer. After UV-ozone cleaning and silanization (formation of the first surface modification layer), within 10 min by mixing with dilute sulfuric acid (1 volume of concentrated H 2 SO 4 +5 volume H 2 O) to remove the Al protective layer. For the metallization step, two different silanes were used: for one set of transistors, OTS (octadecyltrichlorosilane) was used as the first surface modification layer, and for the other set of transistors, PETS (phenylethyltrichlorosilane) was used. Chlorosilane) as the first surface modification l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More