JFET (Junction Field Effect Transistor) and manufacturing method thereof, and micro inverter using JFET

An N-type, channel layer technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, output power conversion devices, etc., can solve the problems of single type, slow development of SiC fully-controlled power devices, and high price, and achieve Simple structure, excellent electrical characteristics, compact size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

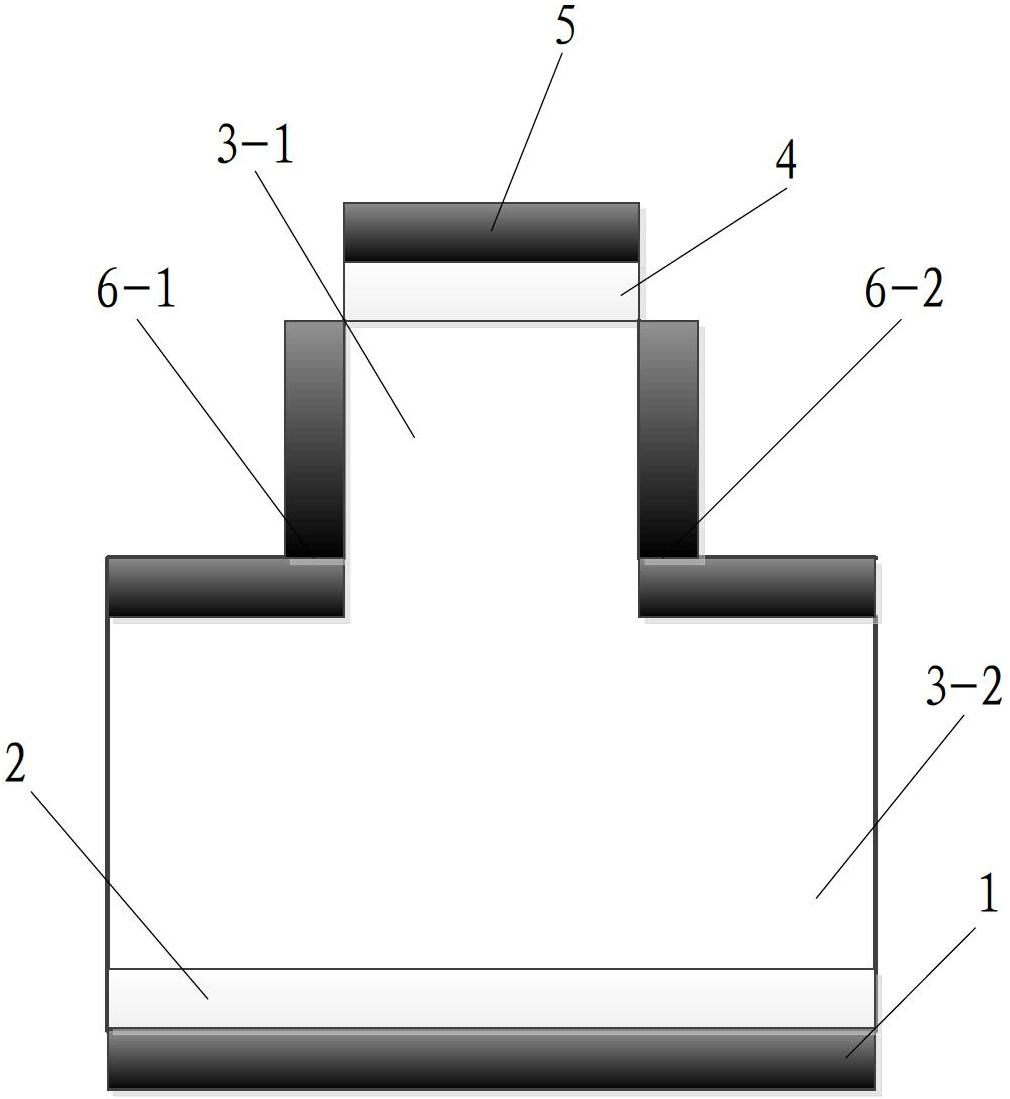

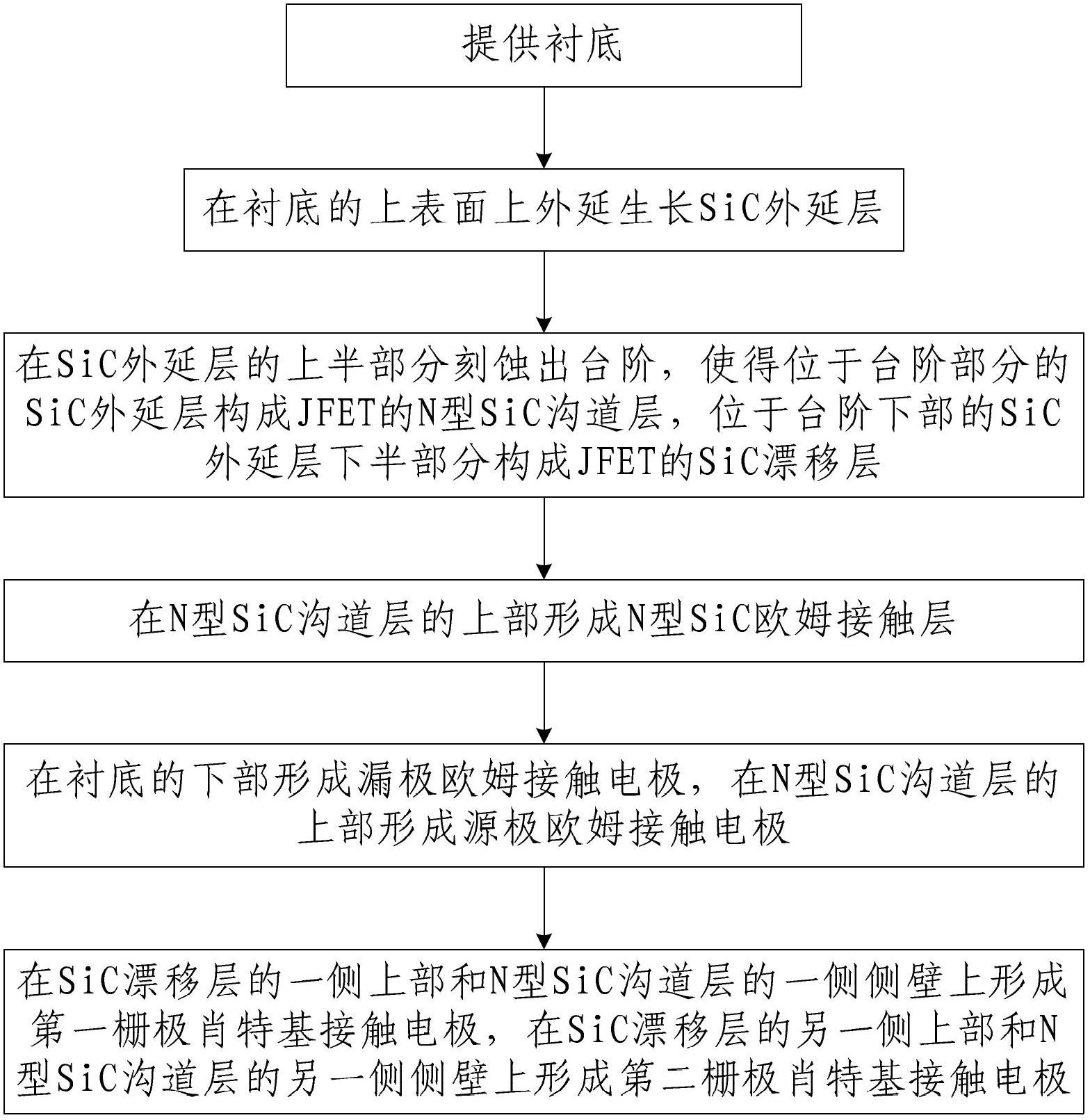

[0042] combine figure 2 , the manufacturing method of JFET described in the present invention, comprises the following steps:

[0043] Step 1, providing a substrate 2, which is composed of an N-type SiC substrate;

[0044] Step 2. Epitaxial growth on the upper surface of the substrate 2 with a doping concentration of 5×10 by using a low pressure hot wall chemical vapor deposition method 16 cm -3 , a SiC epitaxial layer 3 with a thickness of 5 μm, the epitaxial growth temperature is 1570° C., the epitaxial growth pressure is 100 mbar, and the epitaxial growth gas is C with a volume ratio of 2:1:4. 3 h 8 、SiH 4 and H 2 The mixed gas; the structure diagram of JFET when step 2 is completed is as follows Figure 3a shown;

[0045] Step 3, using reactive ion dry etching method and using SF 6 Gas-generated plasma etches a step with a width of 0.5 μm and a thickness of 1 μm on the upper half of the SiC epitaxial layer 3, so that the SiC epitaxial layer 3 at the stepped portio...

Embodiment 2

[0051] The difference between this embodiment and embodiment 1 is that in step 2, a doping concentration of 12×10 is epitaxially grown on the upper surface of the substrate 2 by using a low pressure hot wall chemical vapor deposition method. 16 cm -3 , a SiC epitaxial layer 3 with a thickness of 10 μm; in step 3, reactive ion dry etching and SF 6 The plasma generated by the gas etches a step with a width of 0.9 μm and a thickness of 1.5 μm on the upper half of the SiC epitaxial layer 3; in step 4, ion implantation is used in the N-type SiC channel layer 3-1 The upper part is formed with a doping concentration of 3×10 18 cm -3 N-type SiC ohmic contact layer 4, and thermal annealing at a temperature of 1575° C. for 10 minutes under an Ar atmosphere; in step five, on the lower part of the substrate 2 and the upper part of the N-type SiC channel layer 3-1 Metal Ni and Pt were sequentially evaporated by electron beam, and the N 2 Thermal annealing at a temperature of 975°C for ...

Embodiment 3

[0054] The difference between this embodiment and Embodiment 1 is that in step 2, a low-pressure hot-wall chemical vapor deposition method is used to epitaxially grow on the upper surface of the substrate 2 with a doping concentration of 20×10 16 cm -3 , a SiC epitaxial layer 3 with a thickness of 15 μm; in step 3, reactive ion dry etching and SF 6 Gas-generated plasma etches a step with a width of 1.25 μm and a thickness of 2 μm on the upper half of the SiC epitaxial layer 3; in step 4, an ion implantation method is used in the upper half of the N-type SiC channel layer 3-1 The upper part is formed with a doping concentration of 5×10 18 cm -3 N-type SiC ohmic contact layer 4, and thermal annealing at a temperature of 1600° C. for 10 minutes in an Ar atmosphere; in step five, on the lower part of the substrate 2 and the upper part of the N-type SiC channel layer 3-1 Metal Ni and Pt were sequentially evaporated by electron beam, and the N 2 Thermal annealing at a temperatur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More