Mixed crystal plane silicon-on-insulator (SOI) bipolar complementary metal oxide semiconductor (BiCMOS) integrated device based on square channel process and preparation method

A technology of integrated devices and mixed crystal planes, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problem that the mobility cannot be optimized at the same time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

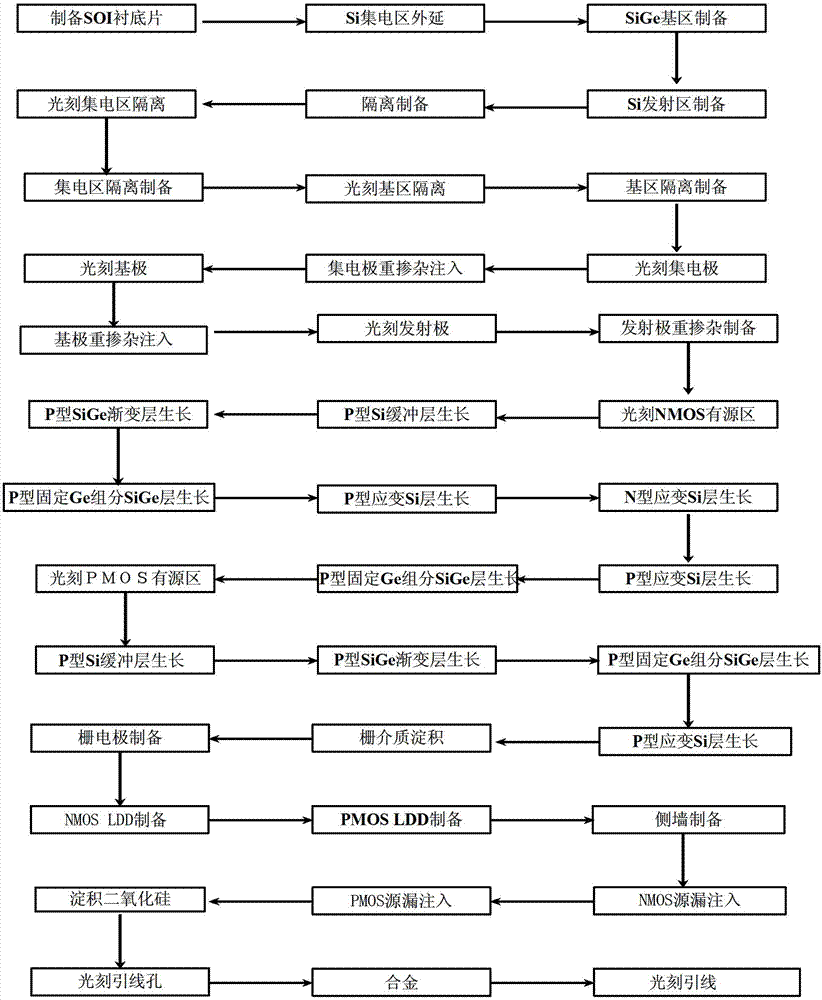

Method used

Image

Examples

Embodiment 1

[0127] Embodiment 1: Preparation of a mixed crystal plane SOIBiCMOS integrated device and circuit based on a back-channel process with a channel length of 22 nm, the specific steps are as follows:

[0128] Step 1, SOI substrate material preparation.

[0129] (1a) Select N-type doping concentration as 1×10 15 cm -3 The Si wafer with a crystal plane of (110), the surface is oxidized, the thickness of the oxide layer is 0.5μm, as the underlying base material, and hydrogen is injected into the base material;

[0130] (1b) Choose the P-type doping concentration as 1×10 15 cm -3 The Si wafer with a crystal plane of (100), the surface of which is oxidized, and the thickness of the oxide layer is 0.5μm, as the base material of the upper layer;

[0131] (1c) Use chemical mechanical polishing (CMP) process to polish the surface of the lower layer and the upper layer of the base material after hydrogen injection;

[0132] (1d) SiO on the surface of the lower and upper base materials after polishin...

Embodiment 2

[0203] Embodiment 2: Preparation of a mixed-plane SOI BiCMOS integrated device and circuit based on a back-channel process with a channel length of 30 nm, the specific steps are as follows:

[0204] Step 1, SOI substrate material preparation.

[0205] (1a) Select the N-type doping concentration as 3×10 15 cm -3 Si wafer with a crystal plane of (110), the surface is oxidized, and the thickness of the oxide layer is 0.75μm, as the underlying base material, and hydrogen is injected into the base material;

[0206] (1b) Choose the P-type doping concentration as 3×10 15 cm -3 The Si wafer with a crystal plane of (100), the surface is oxidized, and the thickness of the oxide layer is 0.75μm, which is used as the base material of the upper layer;

[0207] (1c) Use chemical mechanical polishing (CMP) process to polish the surface of the base material of the lower layer and the upper layer after hydrogen injection;

[0208] (1d) SiO on the surface of the lower and upper base materials after poli...

Embodiment 3

[0279] Embodiment 3: Preparation of a mixed-surface SOI BiCMOS integrated device and circuit based on a back-channel process with a channel length of 45 nm, the specific steps are as follows:

[0280] Step 1, SOI substrate material preparation.

[0281] (1a) Choose N-type doping concentration as 5×10 15 cm -3 The Si wafer with a crystal plane of (110), the surface is oxidized, and the thickness of the oxide layer is 1μm, as the underlying base material, and hydrogen is injected into the base material;

[0282] (1b) Choose the P-type doping concentration as 5×10 15 cm -3 The Si wafer with a crystal plane of (100), the surface of which is oxidized, and the thickness of the oxide layer is 1μm, as the base material of the upper layer;

[0283] (1c) Use chemical mechanical polishing (CMP) process to polish the surface of the lower layer and the upper layer of the base material after hydrogen injection;

[0284] (1d) SiO on the surface of the lower and upper base materials after polishing 2 R...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More