TSV structure applicable to adapter board and preparation method of TSV structure

An adapter plate and substrate technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of increased cost, high etching cost, and small etching options

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

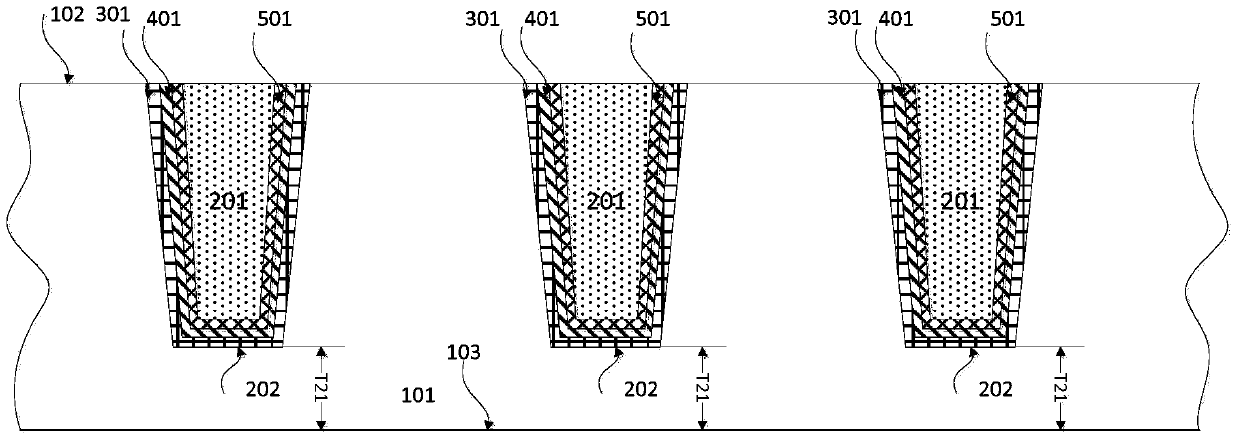

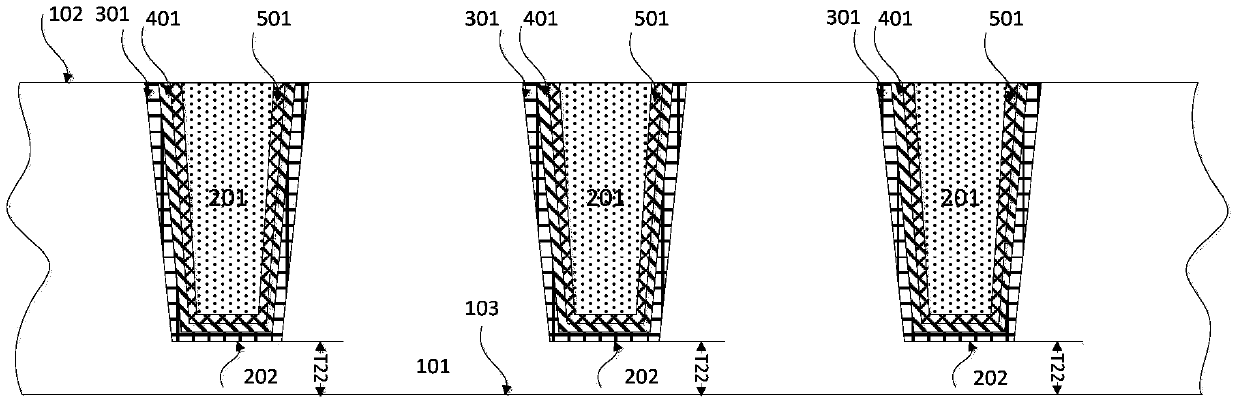

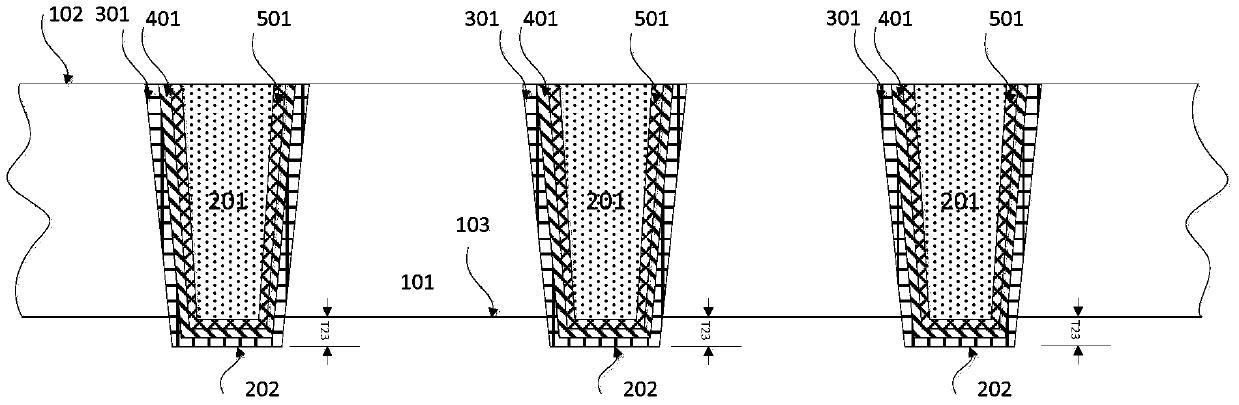

[0026] Embodiment 1: A method for preparing a TSV structure suitable for an adapter plate, comprising the following steps:

[0027] (1) if figure 1 As shown, a substrate 101 is provided, and the substrate 101 is a silicon wafer, silicon carbide (SiC) or gallium arsenide (GaAs), etc., and the substrate 101 has a corresponding substrate front 102 and a substrate back 103; TSV deep hole 201 is formed on 101, and the method of forming TSV deep hole 201 is deep reactive ion etching (DRID), reactive ion etching (RIE) or laser (laser); One end is the TSV head 202, and the thickness of the TSV head 202 from the back surface 103 of the substrate is T21; then a first insulating layer 301 is deposited on the front surface 102 of the substrate, and the first insulating layer 301 covers the front surface 102 of the substrate and the TSV deep hole 201 The side wall and the bottom wall of the first insulating layer 301 adopt thermal oxidation to grow silicon dioxide, and its thickness depen...

Embodiment 2

[0030] Embodiment 2: A method for preparing a TSV structure suitable for an adapter plate, comprising the following steps:

[0031] (1) if figure 1 As shown, a substrate 101 is provided, and the substrate 101 is a silicon wafer, silicon carbide (SiC) or gallium arsenide (GaAs), etc., and the substrate 101 has a corresponding substrate front 102 and a substrate back 103; TSV deep hole 201 is formed on 101, and the method of forming TSV deep hole 201 is deep reactive ion etching (DRID), reactive ion etching (RIE) or laser (laser); One end is the TSV head 202, and the thickness of the TSV head 202 from the back surface 103 of the substrate is T21; then a first insulating layer 301 is deposited on the front surface 102 of the substrate, and the first insulating layer 301 covers the front surface 102 of the substrate and the TSV deep hole 201 The side wall and the bottom wall of the first insulating layer 301 adopt thermal oxidation to grow silicon dioxide, and its thickness depen...

Embodiment 3

[0034] Embodiment 3: A method for preparing a TSV structure suitable for an adapter plate, comprising the following steps:

[0035] (1) if figure 1 As shown, a substrate 101 is provided, and the substrate 101 is a silicon wafer, silicon carbide (SiC) or gallium arsenide (GaAs), etc., and the substrate 101 has a corresponding substrate front 102 and a substrate back 103; TSV deep hole 201 is formed on 101, and the method of forming TSV deep hole 201 is deep reactive ion etching (DRID), reactive ion etching (RIE) or laser (laser); One end is the TSV head 202, and the thickness of the TSV head 202 from the back surface 103 of the substrate is T21; then a first insulating layer 301 is deposited on the front surface 102 of the substrate, and the first insulating layer 301 covers the front surface 102 of the substrate and the TSV deep hole 201 The side wall and the bottom wall of the first insulating layer 301 adopt thermal oxidation to grow silicon dioxide, and its thickness depen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More