Method for manufacturing bifacial solar cell

A manufacturing method and solar cell technology, applied in the field of solar cells, can solve the problems of solar cell performance degradation, phosphorus diffusion and boron diffusion surface corrosion, high manufacturing costs, etc., to avoid pollution, high surface recombination rate, and photogenerated carrier recombination The effect of less and low manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

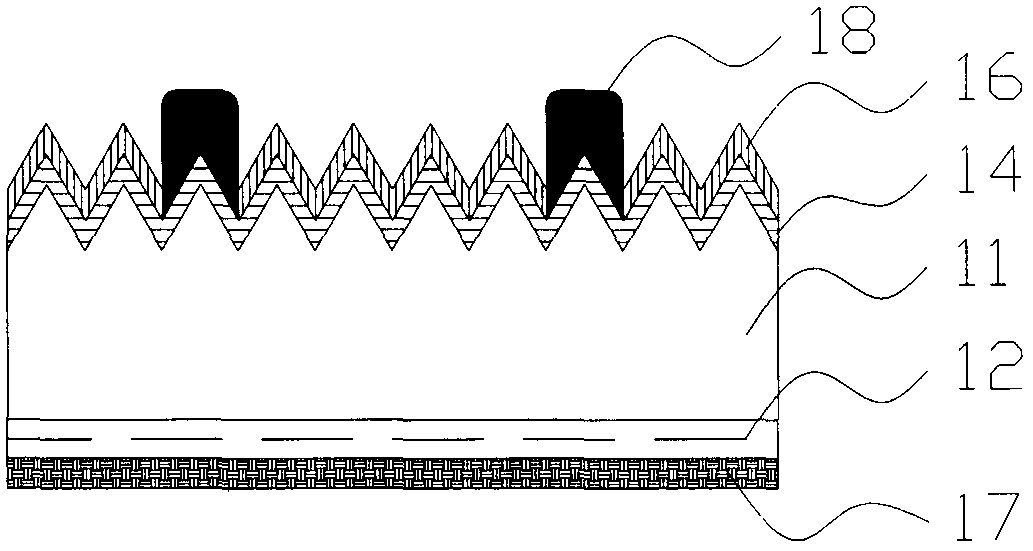

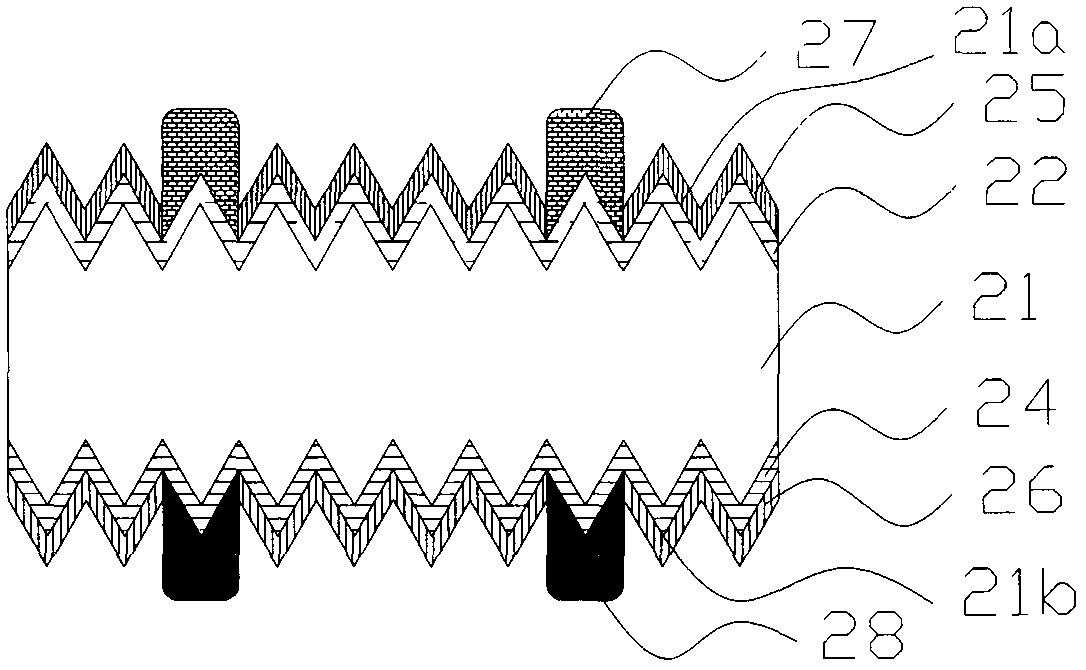

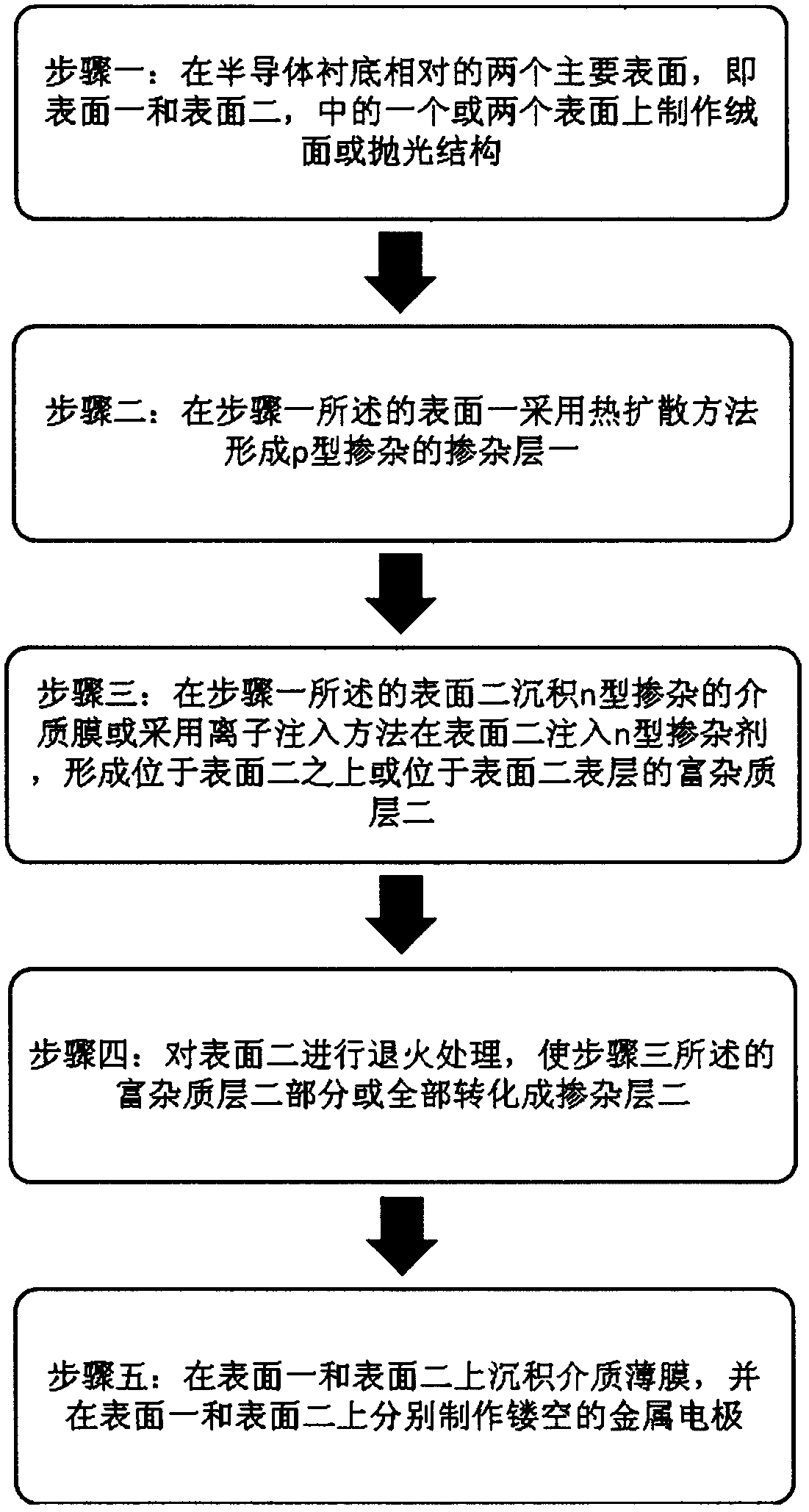

[0065] Embodiment 1 of the present invention discloses a method for manufacturing a double-sided light-receiving solar cell. The flow chart and the schematic diagram of the solar cell structure corresponding to each step are as follows Figure 4 ~ Figure 11 As shown, it specifically includes the following steps:

[0066] Step 1: If Figure 4 and Figure 5 As shown, a textured structure is fabricated on the two opposite main surfaces of a semiconductor substrate 21, such as a crystalline silicon wafer, namely surface one 21a and surface two 21b. The above steps are carried out by wet chemical etching, and the thickness of the material removed from the surface layer of the semiconductor substrate is between 3-8 um, for example 5 um.

[0067] Step 2: If Figure 6 As shown, a p-type doped doped layer 22 is formed on the surface 1 21a in step 1 by thermal diffusion. In the above steps, the textured semiconductor substrate 21 is placed in an environment filled with boron tribrom...

Embodiment 2

[0073] Embodiment 2 of the present invention discloses a method for manufacturing a double-sided light-receiving solar cell. The flow chart and the schematic diagram of the solar cell structure corresponding to each step are as follows: Figure 12 to Figure 19 As shown, it specifically includes the following steps:

[0074] Step 1: If Figure 12 and Figure 13 As shown, a textured structure is fabricated on the two opposite main surfaces of a semiconductor substrate 31, such as a crystalline silicon wafer, namely surface one 31a and surface two 31b. The above steps are carried out by wet chemical etching, and the thickness of the material removed from the surface layer of the semiconductor substrate is between 3-8 um, for example 5 um.

[0075] Step 2: If Figure 14 As shown, a p-type doped doped layer 32 is formed on the surface 1 31a in step 1 by thermal diffusion. In the above steps, the textured semiconductor substrate 31 is placed in an environment filled with boron t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More