Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of increased output power of gallium nitride semiconductor devices, uneven temperature distribution, increased process difficulty, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

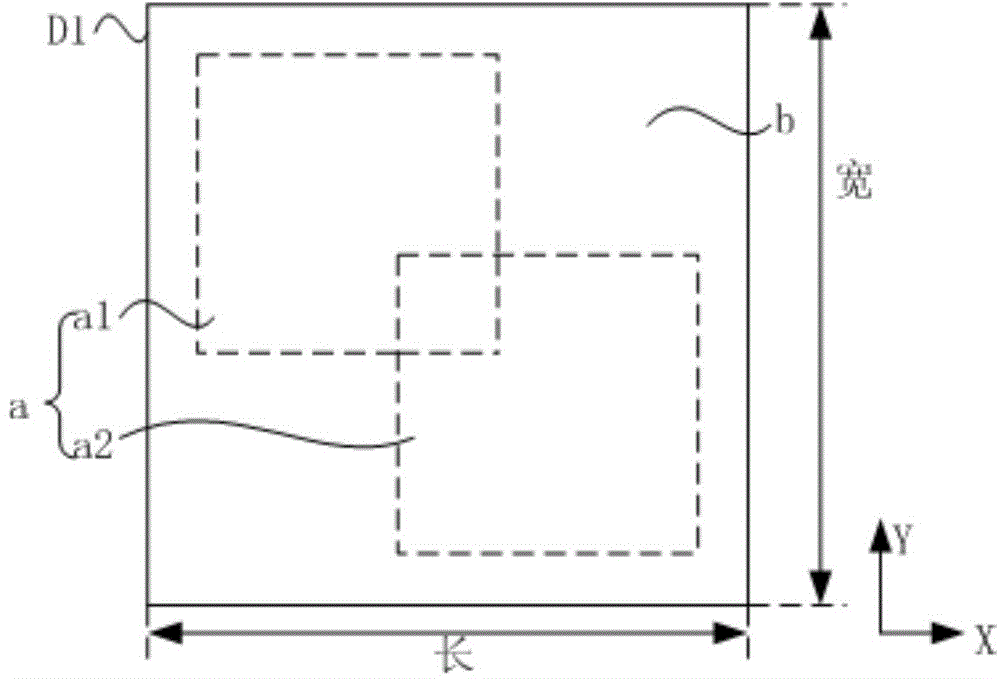

[0039] Figure 3A-Figure 3D It shows a schematic top view of the semiconductor device provided by Embodiment 1 of the present invention, please refer to Figure 3A-Figure 3D , the semiconductor device D1 includes: an active area a and an inactive area b, the active area a includes a plurality of active area units (such as: a1 and a2), and the plurality of active area units are in the The semiconductor device is staggered in the length direction, and the multiple active area units are staggered in the width direction of the semiconductor device.

[0040] In this embodiment, the length direction of the semiconductor device D1 is designated as the X direction, and the width direction of the semiconductor device D1 is designated as the Y direction, wherein the X direction is perpendicular to the Y direction.

[0041]The area other than the active area a is an inactive area. There are two-dimensional electron gas, electrons or holes under the active area a, which is the working ar...

Embodiment 2

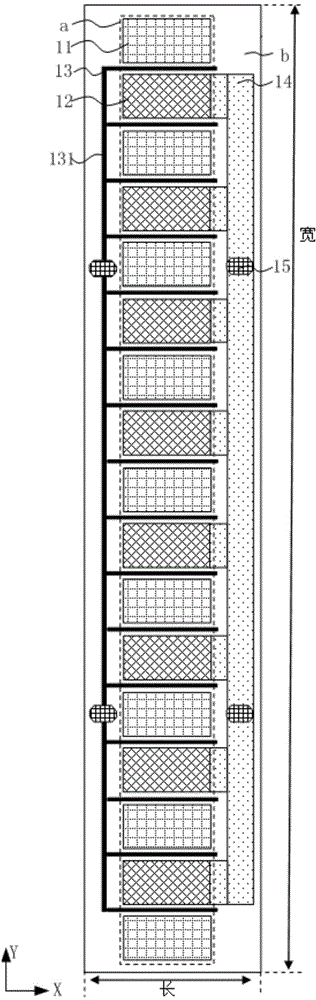

[0048] Figure 4 It shows a schematic top view of the semiconductor device provided by Embodiment 2 of the present invention, please refer to Figure 4 , the semiconductor device D2 includes: an active area and an inactive area b, the area outside the active area is an inactive area b, and the active area includes a plurality of active area units (such as: a1, a2 , a3 and a4), the plurality of active region units are staggered in the length direction of the semiconductor device, and the plurality of active region units are staggered in the width direction of the semiconductor device.

[0049] The active region of the semiconductor device D2 includes a plurality of active region units (such as: a1, a2, a3 and a4), and in the width direction of the semiconductor device, a plurality of active region units (such as: a1, a2, a3 and a4) Staggered arrangement, that is, each active region unit is repeatedly arranged in the width direction of the semiconductor device, and two adjacent...

Embodiment 3

[0060] Figure 6A-6E It shows a schematic top view of the semiconductor device provided by Embodiment 3 of the present invention. Embodiment 3 of the present invention is based on the above-mentioned embodiments, and the following combines Figure 6A-6E Embodiment 3 of the present invention will be described.

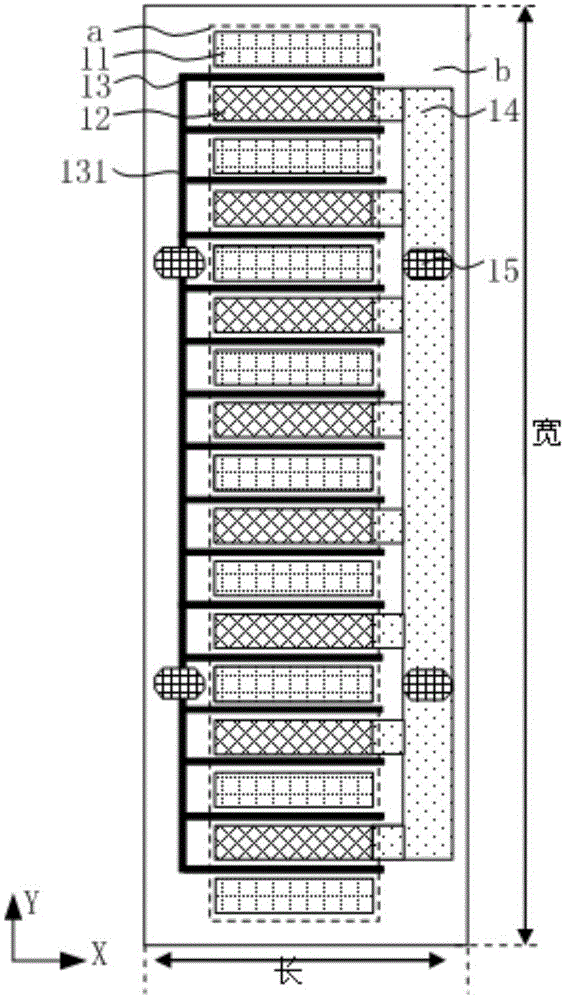

[0061] See Figure 6A ,exist Figure 6A Among them, the active area of the semiconductor device D3 includes a plurality of active area units (such as: a1, a2, a3 and a4), and each active area unit includes a source 11, a gate 13 and a drain 12, The source 11, the gate 13 and the drain 12 form a local interdigitated structure in the active area unit, and any two adjacent active area units do not overlap in the length direction of the semiconductor device. The width direction of the semiconductor device overlaps (such as: a1 and a2). The advantage of this treatment is that the distance between two adjacent active region units in the width direction of the semiconduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More