Method for efficiently electroplating and filling silicon-based TSV

A silicon-based, high-efficiency technology, applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the constraints on the application and development of 3D-TSV packaging technology, affect the thermomechanical stability and electrical properties of TSV, and the end of deep holes The difficulty of controlling the plating rate is high, achieving the effects of high thermomechanical stability, good electrical conductivity, and good bonding force

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

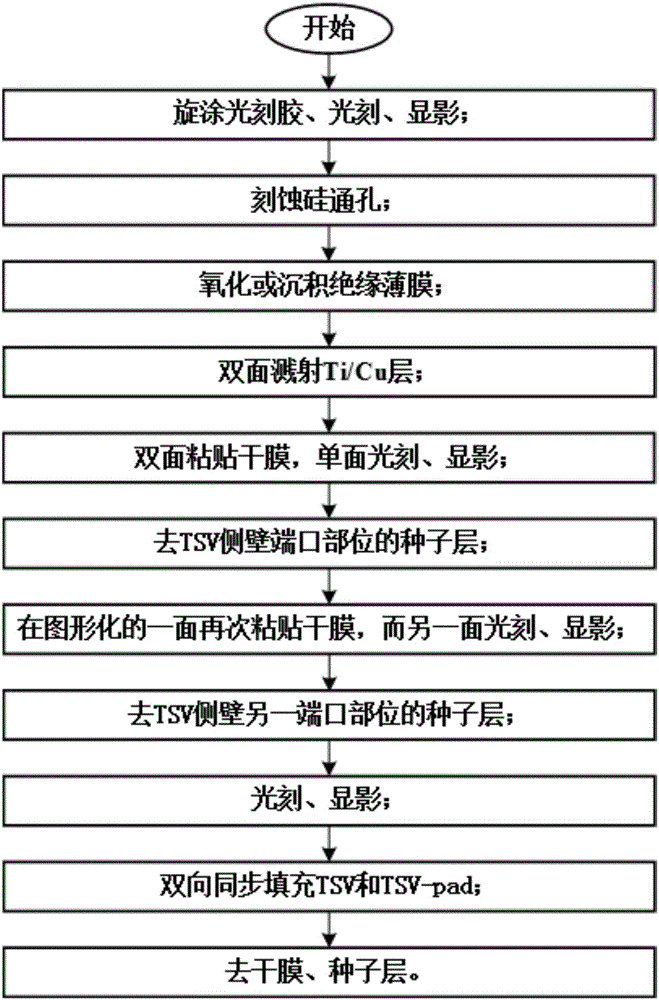

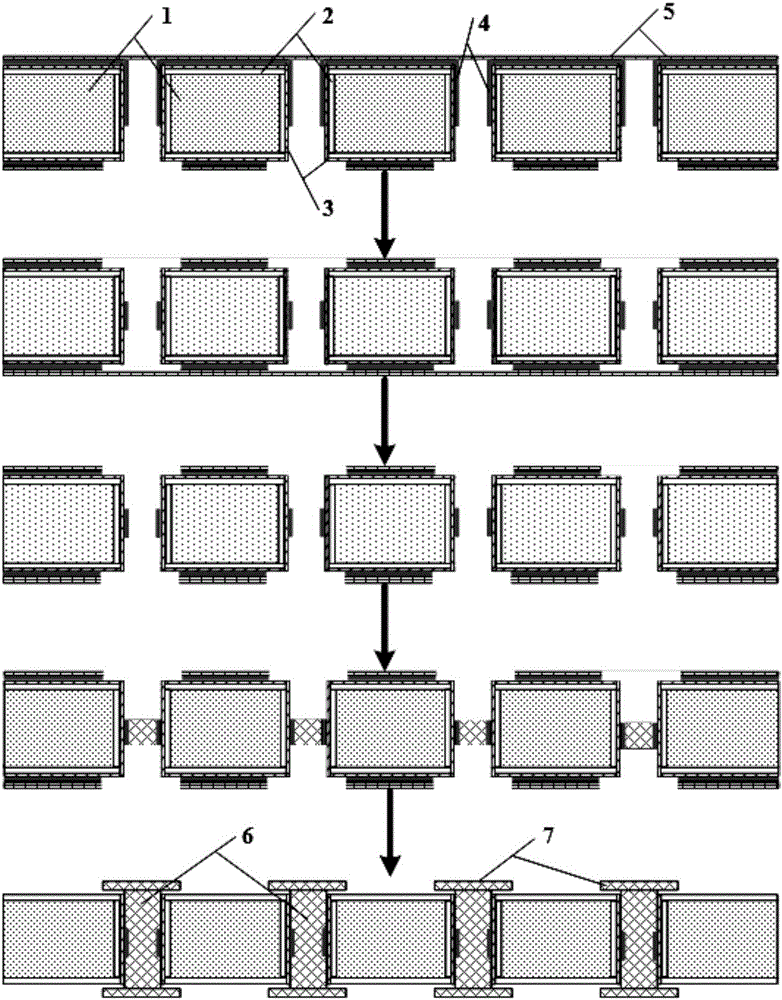

[0046] This embodiment provides a method for efficiently electroplating and filling silicon-based TSVs. Three times of TSV patterning are used to remove the seed layer at both ends of the TSV sidewall. Pre-wetting treatment is performed before electroplating. Perform bidirectional simultaneous blind via filling.

[0047] Described method specifically comprises the steps:

[0048] 1) Spin-coat positive resist with a thickness of 16 μm on the silicon wafer, bake the glue in a programmable oven, and perform photolithography and development on the baked wafer;

[0049] 2) using deep ion etching technology to etch TSVs on the wafer processed in step 1);

[0050] 3) high temperature oxidation is used to oxidize the surface of the wafer treated in step 2), and the oxidized thickness is 0.2 μm;

[0051] 4) on the wafer surface processed in step 3), carry out two-way sputtering Ti / Cu layer;

[0052] 5) paste dry film photoresist on both sides of the wafer after step 4), and then per...

Embodiment 2

[0064] This embodiment provides a method for efficiently electroplating and filling silicon-based TSVs. The previous steps are the same as in Embodiment 1, except that negative resist is selected as the coating, TSVs are etched by laser, and insulating films are deposited by chemical deposition techniques. The seed layer at the port portion of the side wall of the TSV is etched in a sealed pressure manner.

[0065] Described method specifically comprises the steps:

[0066] 1) Spin-coat the silicon wafer with a 10 μm negative glue, bake the glue in a programmable oven, and perform photolithography and development on the baked wafer;

[0067] 2) using laser technology to etch TSVs on the wafer processed in step 1);

[0068] 3) Depositing an insulating film on the surface of the wafer treated in step 2) by using chemical deposition technology, the thickness of the deposited insulating film is 0.21 μm;

[0069] 4) on the wafer surface processed in step 3), carry out two-way spu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More