Porous structure organic field effect transistor photosensitive memory and preparation method thereof

A porous structure and transistor technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the lack of research on the joint enhancement effect of photoresponse and storage characteristics, further explanation and systematic discussion, new material development costs Advanced problems, to achieve the effect of enhancing photoelectric conversion efficiency, increasing process complexity, improving storage performance and photosensitive performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

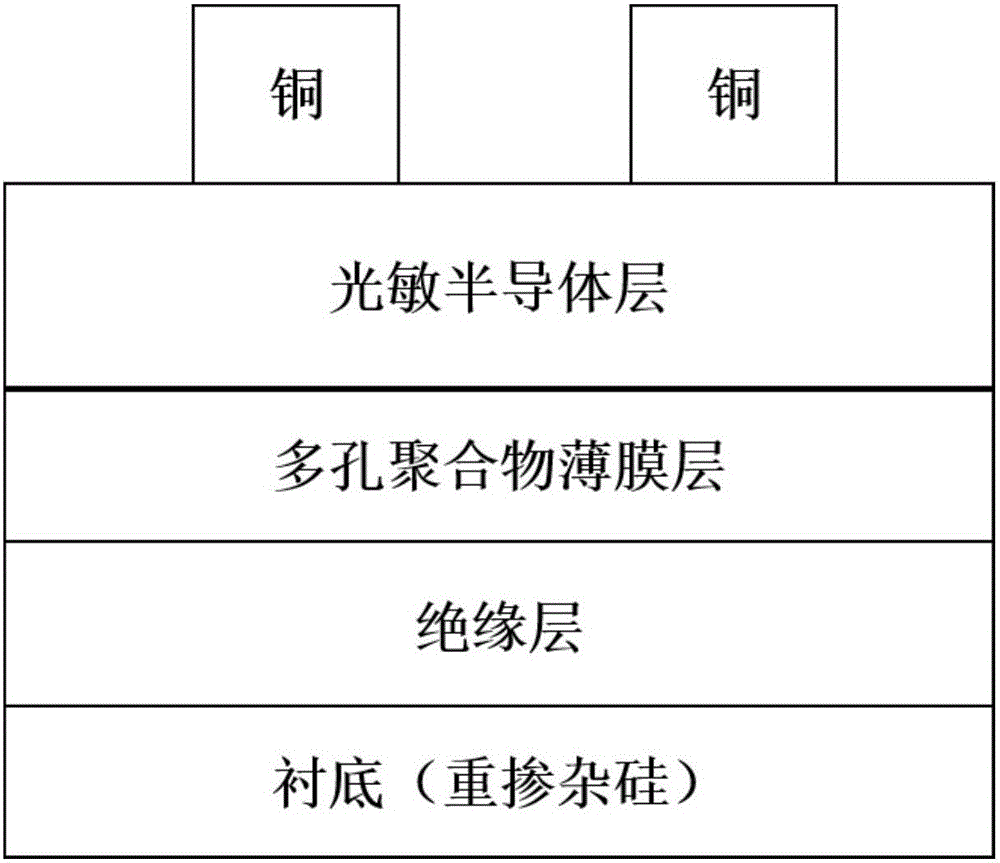

[0038] The present invention provides an organic field-effect transistor memory structure, and its structure diagram is as figure 1 Shown, including:

[0039] Substrate

[0040] A gate electrode formed on the substrate;

[0041] A gate insulating layer covering the gate electrode;

[0042] A polymer film layer with a porous structure formed on the gate insulating layer;

[0043] A porous organic photosensitive semiconductor layer formed on a porous polymer film layer; and

[0044] Porous source and drain electrodes formed on both sides of the channel region on the surface of the porous organic photosensitive semiconductor layer.

[0045] The substrate is a highly doped silicon wafer or glass wafer or plastic PET.

[0046] In the technical solution of this embodiment, heavily doped silicon is used as the substrate and gate electrode; a layer of 50-300nm silicon dioxide is used as the gate insulating layer; the polymer film layer with a porous structure is made of polymer polyethylene with a...

Embodiment 2

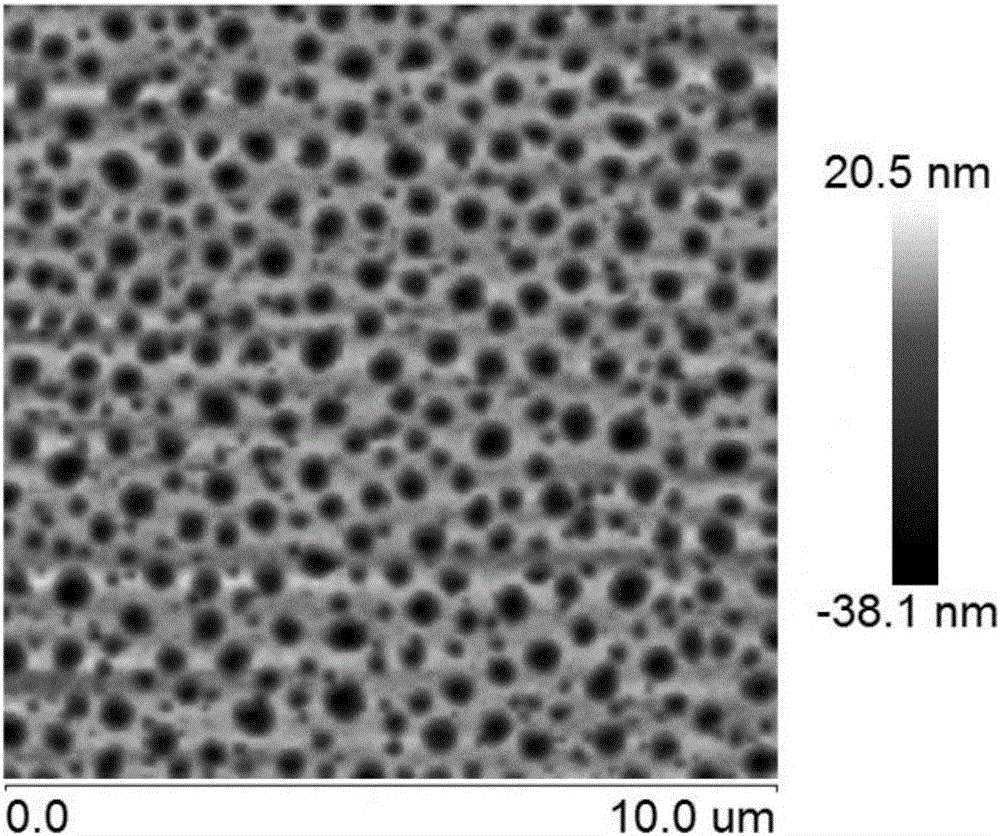

[0061] In the technical scheme of this embodiment, heavily doped silicon is used as the substrate and gate electrode; a layer of 50nm silicon dioxide is used as the gate insulating layer; the polymer film layer with porous structure is made of polymer polymethyl with porous structure. It is made of methyl acrylate (PMMA) with a thickness of 70nm; a 30nm thick pentacene layer is vapor-deposited on the gate insulating layer to serve as an organic photosensitive semiconductor layer; and then metal copper is vapor-deposited on both sides of the conductive channel as source and drain electrodes.

[0062] In the actual preparation, the laboratory room temperature is kept at about 25°C, and the indoor humidity is kept below 50%.

[0063] The specific preparation steps of the memory in this embodiment are as follows:

[0064] (1) Prepare PMMA solution, the concentration of the solution is 5mg / ml, and the solvent is tetrahydrofuran (THF) without additional water removal treatment and let stan...

Embodiment 3

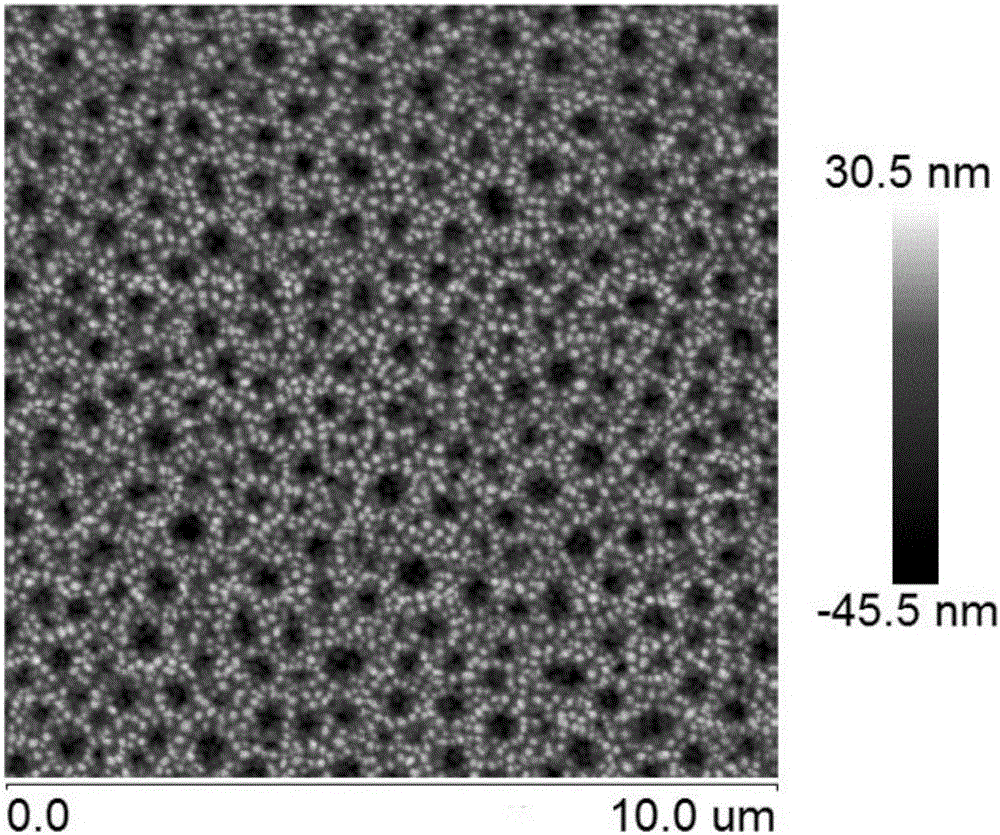

[0070] In the technical solution of this embodiment, heavily doped silicon is used as the substrate and gate electrode; a layer of 50nm silicon dioxide is used as the gate insulating layer; the polymer film layer with a porous structure is made of a polymer polyvinyl group with a porous structure. It is composed of carbazole (PVK) with a thickness of 25nm; a layer of 50nm thick titanium bronze is vapor-deposited on the gate insulating layer to serve as an organic photosensitive semiconductor layer; and copper metal is vapor-deposited on both sides of the conductive channel as source and drain electrodes.

[0071] In the actual preparation, the laboratory room temperature is maintained at about 25°C, and the indoor humidity is maintained at 40%.

[0072] The specific preparation steps of the memory in this embodiment are as follows:

[0073] (1) Prepare polyvinyl carbazole (PVK) solution, the solution concentration is 5mg / ml, the solvent is chloroform (CHCl 3 ) Let stand for 24 hours ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More